Quartus II使用—原理图输入步骤

- 格式:ppt

- 大小:1.10 MB

- 文档页数:22

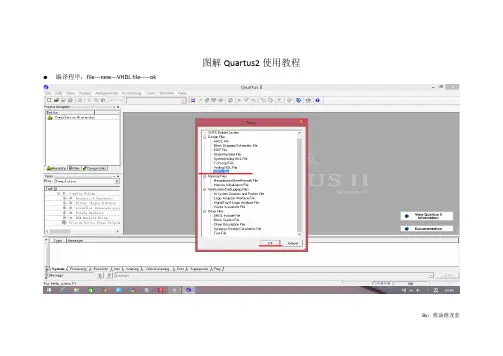

图解Quartus2使用教程编译程序:file---new---VHDL file-----okBy:酱油跑龙套编译程序---点保存---选择文件夹----修改文件名为of之前内容(注意大小写,保持相同)----点保存By:酱油跑龙套之后弹出建立工程的对话框,选…------选中文件,点打开,再添加By:酱油跑龙套Next之后按如下选择By:酱油跑龙套点finish---然后编译By:酱油跑龙套之后等待弹出编译成功的对话框,点确定。

编译文件完成By:酱油跑龙套原理图文件---左上窗口点file----选中文件右键----创建@¥#……¥By:酱油跑龙套创建原理图文件By:酱油跑龙套加入工程元件By:酱油跑龙套加入输入输出文件By:酱油跑龙套修改输入输出名字(强调方括号,中间两点)By:酱油跑龙套点保存(这个名字无要求)---设置顶层文件----点编译---弹出编译成功的对话框---点确定----原理图文件完成By:酱油跑龙套时序图文件,新建文件By:酱油跑龙套Edit---end timeBy:酱油跑龙套一般为55usBy:酱油跑龙套在时序图中加入引脚By:酱油跑龙套By:酱油跑龙套By:酱油跑龙套之后可以设置输入的高低电平,以及时钟信号By:酱油跑龙套保存,编译,名字无影响,编译成功By:酱油跑龙套●程序下载——pins●By:酱油跑龙套设置硬件引脚By:酱油跑龙套插上usb线后,会安装驱动,按默认安装就好连接成功后选择下载By:酱油跑龙套驱动安装成功后,点击start,下载完成后测试以上所有原文来自天津工业大学:酱油跑龙套By:酱油跑龙套。

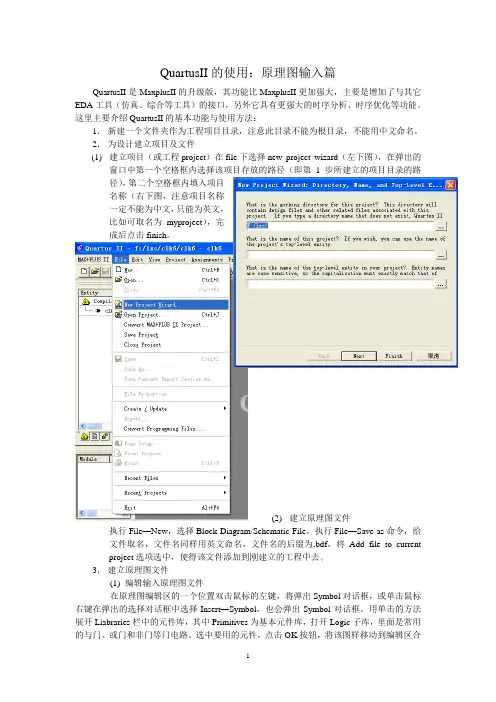

QuartusII的使用:原理图输入篇QuartusII是MaxplusII的升级版,其功能比MaxplusII更加强大,主要是增加了与其它EDA工具(仿真、综合等工具)的接口,另外它具有更强大的时序分析、时序优化等功能。

这里主要介绍QuartusII的基本功能与使用方法:1.新建一个文件夹作为工程项目目录,注意此目录不能为根目录,不能用中文命名。

2.为设计建立项目及文件(1)建立项目(或工程project)在file下选择new project wizard(左下图),在弹出的窗口中第一个空格框内选择该项目存放的路径(即第1步所建立的项目目录的路名称(右下图,注意项目名称一定不能为中文,只能为英文,比如可取名为myproject),完成后点击finish。

(2)建立原理图文件执行File—New,选择Block Diagram/Schematic File,执行File—Save as命令,给文件取名,文件名同样用英文命名,文件名的后缀为.bdf,将Add file to currentproject选项选中,使得该文件添加到刚建立的工程中去。

3.建立原理图文件(1)编辑输入原理图文件在原理图编辑区的一个位置双击鼠标的左键,将弹出Symbol对话框,或单击鼠标右键在弹出的选择对话框中选择Insert—Symbol,也会弹出Symbol对话框。

用单击的方法展开Liabraries栏中的元件库,其中Primitives为基本元件库,打开Logic子库,里面是常用的与门、或门和非门等门电路。

选中要用的元件,点击OK按钮,将该图样移动到编辑区合适的地方单击鼠标左键便可。

所需的元件都画好后,将所有的门电路按照连接好。

(2)设定各输入输出引脚名。

双击任意一个input元件,在弹出的引脚属性对话框中的第一行Pin name(s)文本框中填入引脚名称即可,第二行默认值,不需要改动。

用类似的方法设定其他输入和输出引脚名。

§2.3 相关技术基本知识与基本技能一、QuartusⅡ原理图输入法应用数字逻辑电路的基本知识,使用QuartusⅡ原理图输入法可非常方便地进行数字系统的设计。

应用QuartusⅡ原理图输入法,还可以把原有的使用中示规模的通用数字集成电路设计的数字系统移植到FPGA或CPLD中。

下面以一个二人表决器的设计为例说明QuartusⅡ原理图输入法的使用方法。

(一)建立工程文件夹1.新建一个文件夹作为工程项目目录首先在计算机中建立一个文件夹作为工程项目目录,此工程目录不能是根目录,比如D:,只能是根b录下的b录,比如D:\EDA _book\code\Chapter3\BiaoJueQi。

下一页§2.3 相关技术基本知识与基本技能2.建立工程项目运行Quartus Ⅱ软件,执行File=>New Project Wizard 命令,建立工程,如图2-17所示。

在图2-18界面中单击Next按钮。

在所弹出的图2-19 New Project Wizard对话框中,填写Directory,Name, Top-Level Entity等项目。

其中第一、第二、第三个文本框分别是工程项目目录、项目名称和项目顶层设计实体的名称。

单击Next按钮,出现添加工程文件的对话框,如图2-20所示。

若原来己有文件,可选择相应文件,这单直接单击Next进行下一步,选择FPGA器件的型号,如图2-21所示。

下一页上一页§2.3 相关技术基本知识与基本技能在Family下拉框中,根据需要选择一种型号的FPGA,比如Cyclone系列FPGA。

然后在“Available devices:”中根据需要的FPGA 型号选择FPGA型号,比如“EP1C3T144C8”,注意在Filters一栏中选中“Show Advanced Devices”以显示所有的器件型号。

再单击Next按钮,出现如图2-22所示对话框。

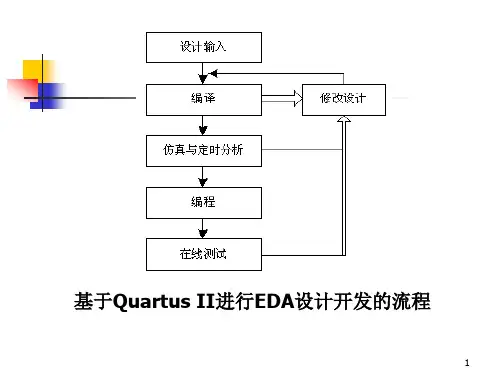

Quartus_II使用方法第1章QUARTUS II2.1 QUARTUSII概述设计输入是设计者对系统要实现的逻辑功能进行描述的过程。

设计输入有多种表达方式,常用的用原理图输入、硬件描述语言输入、网表输入等。

1、原理图输入:原理图设计输入方式是利用软件提供的各种原理图库,采用画图的方式进行设计输入。

这是一种最为简单和直观的输入方式。

原理图输入方式的效率比较低,半只用于小规模系统设计,或用于在顶层拼接各个以设计完成的电路子模块。

2、硬件描述语言输入:这种设计输入方式是通过文本编辑器,用VHDL,Verilog或AHDL等硬件描述语言进行设计输入。

采用语言描述的有点事效率较高,结果容易仿真,信号观察方便,在不同的设计输入库之间转换方便,适用于大规模数字系统的设计。

但语言输入必须依赖综合器,只有好的综合器才能把语言综合成优化的电路。

3、网表输入:现代可编程数字系统设计工具都提供了和它第三方EDA工具相连接的接口。

采用这种方法输入时,可以通过标准的网表把它设计工具上已经实现了的设计直接移植进来,而不必重新输入。

一般开发软件可以接受的网表有EDIF格式、VHDL 格式及Verilog格式等。

在用网表输入时,必须注意在两个系统中采用库的对应关系,所有的库单元必须一一对应,才可以成功读入网表[6]。

2.2 QUARTUSII建立工程项目在Quartus II 中,用户的每个独立设计都对应一个工程项目,每个工程项目可包含一个或多个设计文件。

其中一个是顶层文件,编译器是对项目中的顶层文件进行编译的,项目同时还管理编译过程中产生的各种中间文件,这些中间文件的文件名相同,但后缀名不同。

为了便于管理,对于每个新的项目应该建立一个单独的子目录。

指定项目名称的步骤如下:1. 打开Quartus II,在File 菜单中选择New Project Wizard 项,将出现工程项目建立向导对话框。

如图2-1 (a)所示。

2. 点击“Next”,进入到如图2-1 (b)所示的工程项目命名对话框,在最上面的文本输入框中输入为该项目所建的目录名,如本例为“E:\Clock”,在中间的文本输入框中输入项目名称,本次实验为“adder”,在最下面的文本输入框中输入最顶层模块的名称“adder”。

Quartus II 的使用 (2)1 工程建立 (2)2 原理图的输入 (5)3 文本编辑(verilog) (15)4 波形仿真 (16)Quartus II 的使用在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。

进入WINDOWS XP后,双击Quartus II图标,屏幕如图所示。

图 Quartus II 管理器工程建立使用 New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和 EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。

建立工程的步骤如下:(1)选择File菜单下New Project Wizard ,如图所示。

图建立项目的屏幕(2)输入工作目录和项目名称,如图所示。

可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图项目目录和名称(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图所示。

图加入设计文件(4)选择设计器件,如图所示。

图选择器件(5)选择第三方EDA综合、仿真和时序分析工具,如图所示。

图选择EDA 工具(6)建立项目完成,显示项目概要,如图所示。

图项目概要原理图的输入原理图输入的操作步骤如下:(1)选择File 菜单下 New ,新建图表/原理图文件,如图所示。

图新建原理图文件(2)在图的空白处双击,屏幕如图所示:(3)在图的Symbol Name 输入编辑框中键入dff后,单击ok按钮。

此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图)单击鼠标左键,使其固定;(4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图所示;在图中,将光标移到右侧input右侧待连线处单击鼠标左键后,再移动到D触发器的左侧单击鼠标左键,即可看到在input和D触发器之间有一条线生成;图空白的图形编辑器图选择元件符号的屏幕图放置所有元件符号的屏幕(5)重复(4)的方法将DFF和output连起来,完成所有的连线电路如图所示;(6)在图中,双击input_name使其衬低变黑后,再键入clk,及命名该输入信号为clk,用相同的方法将输出信号定义成Q;如图所示。

2.4 原理图输入设计方法利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。

Quartus Ⅱ提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。

但更为重要的是,Quartus Ⅱ还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。

以传统的数字电路实验相比为例,Quartus Ⅱ提供原理图输入设计功能具有显著的优势:①能进行任意层次的数字系统设计。

传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计;②对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1ns,因此能发现一切对系统可能产生不良影响的竞争冒险现象;③通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正;④能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件;⑤通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。

⑥如果使用FPGA和配置编程方式,将不会有任何器件损坏和损耗;⑦符合现代电子设计技术规范。

传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。

以下将详细介绍原理图输入设计方法,但读者应该更多地关注设计流程,因为除了最初的图形编辑输入外,其它处理流程都与文本(如VHDL文件)输入设计完全一致。

2.4.1 1位全加器设计向导1 为本项设计建立文件夹任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有文件的文件夹,此文件夹将被EDA软件默认为工作库(Work Library)。