PPT精品文档---实验七、基于Quartus II的原理图输入数字电路设计

- 格式:ppt

- 大小:1.96 MB

- 文档页数:15

数字电路与逻辑设计实验实验名称:Quartus II 原理图输入法设计班级:实验目的:1、熟悉用Quartus II 原理图输入法进行电路设计和仿真;2、掌握Quartus II图形模块的生成与调用;3、熟悉实验板的使用。

一、实验所用仪器与元器件:1、计算机2、直流稳压电源3、数字系统与逻辑设计实验开发板二、实验内容:1、用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。

2、用实验内容 1 中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号。

3、用3线-8线译码器和逻辑门设计实现函数=+++,仿真验证其功能,并下载到实验F C B A C B A C B A C B A板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

三、 设计思路与过程:1、半加器的实现:半加器是能够实现两个1位二进制数码相加求得和数及向高位进位的逻辑电路。

设被加数和加数用变量A 、B 表示,求得的和、向高位进位用变量S 、C 表示,则可得如下真值表:由真值表可以写出S 、C 的函数表达式:S A BC A B=⊕=所以半加器用一异或门和与门即可实现。

2、全加器的实现(可用1中封装好的半加器) 全加器是实现两个1位二进制数及低位来的进位相加(即将3个1位二进制数相加),求得和数及向高位进位的逻辑电路。

在该全加器中,A1、B1分别表示输入的被加数、加数、C_1表示低位来的进位,S1、C1分别表示本位和、高位的进位。

可得该电路的真值表:由真S1、C1的卡诺图为得1111111111111111S =A B C _+A B _A B _A B _=A B _C C C C ++⊕⊕同理可得111111()_C A B C A B =⊕+3、利用3线-8线译码器和逻辑门设计实现函数F C B A C B A C B A CBA=+++3线-8线译码器的符号如右图所示(由于没有74LS138,就用74138来替代了)。

基于QUARTUSII图形输入电路的设计基于QUARTUSII 图形输入电路的设计一、实验目的1、通过一个简单的3—8 译码器的设计,掌握组合逻辑电路的设计方法。

2、初步了解QUARTUSII 原理图输入设计的全过程。

3、掌握组合逻辑电路的静态测试方法。

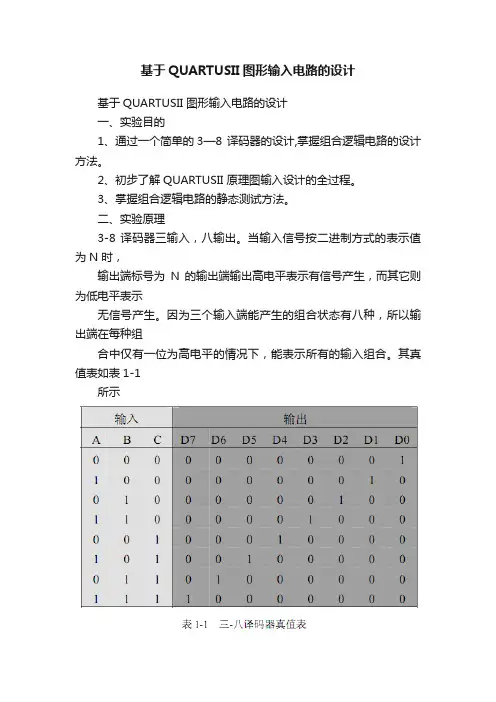

二、实验原理3-8 译码器三输入,八输出。

当输入信号按二进制方式的表示值为N 时,输出端标号为N 的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

其真值表如表1-1所示三、实验内容在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED 来表示三八译码器的八个输出(D0-D7)。

通过输入不同的值来观察输入的结果与三八译码器的真值表(表1-1)是否一致。

实验箱中的拨动开关与FPGA 的接口电路如下图1-1 所示,当开关闭合(拨动开关的档位在下方)时其输出为低电平,反之输出高电平。

其电路与FPGA 的管脚连接如表1-2 所示LED 灯与FPGA 的接口电路如图1-2 所示,当FPGA 与其对应的端口为高电平LED 就会发光,反之LED 灯灭。

其与FPGA 对应的管脚连接如表1-3 所示。

四、实验步骤下面将通过这个实验,向读者介绍QUARTUSII 的项目文件的生成、编译、管脚分配以及时序仿真等的操作过程。

1、建立工程文件2、建立图形设计文件3、对设计文件进行编译4、管脚分配5、5对设计文件进行仿真6从设计文件到目标器件的加载五、实验现象与结果文件加载到目标器件后,拨动拨动开关,LED灯会按表1-1所示的真值表对应的点亮。

六实验总结通过该实验第一次接触了QUARTUSII软件,实验一主要是熟悉了该软件的使用方法学习如何对管教进行分配,如何对程序进行加载仿真。

在实验中遇到很多的问题,首先就是对软件的不熟悉,一开始时不知道如何使用软件,在实验过程中通过老师的指导和自己的尝试基本上完成了实验要求。

实验一基于QUARTUS II图形输入电路的设计一、实验目的1、熟悉Altera FPGA开发流程,掌握Quartus 11原理图输入设计的开发流程。

2、通过一个简单的3-8译码器的设计,掌握组合逻辑电路的设汁方法。

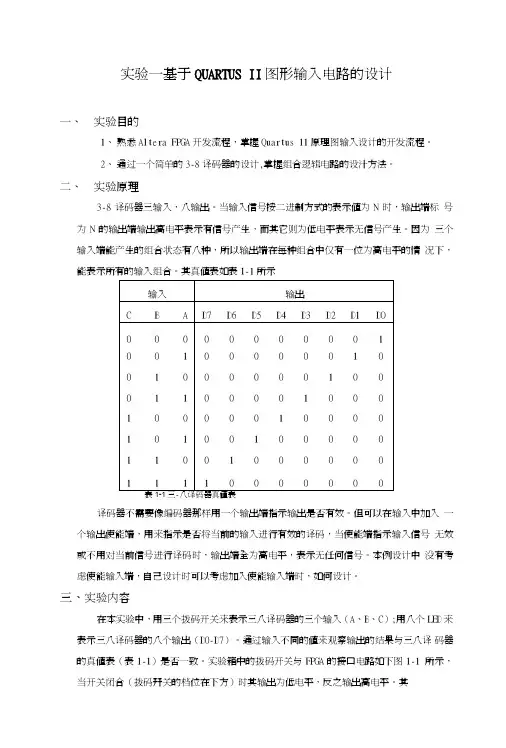

二、实验原理3-8译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

其真值表如表1-1所示1-1译码器不需要像编码器那样用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,如何设计。

三、实验内容在本实验中,用三个拨码开关来表示三八译码器的三个输入(A、B、C);用八个LED 来表示三八译码器的八个输出(D0-D7)。

通过输入不同的值来观察输出的结果与三八译码器的真值表(表1-1)是否一致。

实验箱中的拨码开关与FPGA的接口电路如下图1-1 所示,当开关闭合(拨码幵关的档位在下方)时其输出为低电平,反之输出高电平。

其电路与FPGA的管脚连接如表1-2所示图卜1拨码开关与FPGA接口电路1-2HPGALED灯与FPGA的接口电路如图1-2所示,当FPGA与其对应的端口为低电平时LED图1-2 LED灯与FPGA接口电路1-3 LED FPGA 下面将通过这个实验,向读者介绍QL'ARTUS I 丨的项目文件的生成、编译、管脚分配 以及时序仿真等的操作过程。

1、建立工程文件1)选择开始-〉程序-〉々116门->0此〃1^3丨1 9.0,运行QUARTUS II 软件。

或者双击 桌而上的QUAKTUS II 的图标运行QUAKTUS II 软件,出现如图1_3所示,如果是第一次 打开QUAHUS 丨1软件可能会有其它的提示信息,使用者可以根据自己的实际情况进行 设定后进入图1-3所示界面。