一种大频偏和低信噪比条件下的全数字锁相环设计

- 格式:pdf

- 大小:1.16 MB

- 文档页数:5

一种低抖动带宽自适应锁相环的设计与实现刘颖;田泽;邵刚;刘敏侠【摘要】随着高速通信系统的发展和传输速率的不断提高,锁相环作为提供精确时钟信号的核心电路,不仅需要产生低抖动、低噪声的时钟,而且要求频率覆盖范围广和支持多协议,而恒定带宽的锁相环无法满足多协议对锁相环带宽的要求。

为了实现统一架构下多协议对不同频率的带宽要求,文中设计了一种宽温低抖动带宽自适应的锁相环电路,利用比较器模块和电荷泵形成反馈回路灵活地改变电荷泵电流,实现了环路带宽对不同频率在锁定过程中的自适应调整。

同时采用改进的占空比校正、压控振荡器和电荷泵电路,降低了锁相环噪声。

采用0.13μm CMOS工艺。

测试结果表明输出频率为1.0625~3 GHz,数据率覆盖1.0625~5.9 Gbps,RJ<1.3 ps,温度范围为-55~125℃,满足了FC-PI-4、PCIE1.1和Rapid IO1.3的协议要求,已成功应用于多款高速SerDes芯片中。

%With the development of high speed communication system and the improvement of the transmissionspeed,PLL to be the core circuit of providing precision clock is not only required to produce low jitter and low noise clock,but also demanded wide frequency range and multi-protocol support,but the fixed bandwidth PLL cannot reach the requirement of multi-protocol. An adaptive bandwidth PLL with wide temperature range and low jitter is designed for achieving the requirements of multi-protocol in the unify configuration,using the comparator and charge pump to form a feedback loop to flexibly change the charge pump current,and making the loop bandwidth a-daptively adjusted at different rates. Adopt the improved duty-cyclecontroller,voltage control oscillator and charge pump circuit to de-creasethe noise of PLL. This chip is fabricated in 0. 13 μm CMOS process. The measured results show that the output frequency is from 1. 062 5 to 3 GHz and the data rate covers 1. 062 5~5. 9 Gbps,RJ is less than 1. 3 ps,the operating temperature range is-55~125 ℃, which meet the protocol requirements of FC-PI-4、PCIE1. 1 and Rapid IO1. 3,and has been successfully applied to a variety of high speed SerDes chip.【期刊名称】《计算机技术与发展》【年(卷),期】2015(000)006【总页数】4页(P163-165,175)【关键词】锁相环;带宽自适应;宽温;低抖动【作者】刘颖;田泽;邵刚;刘敏侠【作者单位】中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119【正文语种】中文【中图分类】TP31由于锁相环能够产生低抖动、低噪声的时钟,被广泛应用于高速兼容多种协议的通信系统中。

1

1ghz的锁相环电路

锁相环(PLL)是一种用于产生特定频率输出信号的电路,通常

用于时钟生成和频率合成。以下是一个简单的描述 1GHz 锁相环电路

的基本原理:

相比较器(Phase Comparator): 锁相环的核心是相比较器,它

比较输入信号和反馈信号的相位差。在 1GHz 的锁相环中,相比较器

会比较输入信号和反馈信号的相位,产生一个误差信号。

电荷泵(Charge Pump): 误差信号由相比较器输出,接着传递

到电荷泵。电荷泵会根据误差信号的极性来控制电荷的注入或抽出,

产生一个控制电压。

低通滤波器: 控制电压经过低通滤波器,平滑掉高频噪声,生

成锁相环的调整电压。

振荡器(Voltage-Controlled Oscillator,VCO): 调整电压连接到

VCO,通过调整 VCO 的频率,以使输出信号的相位与输入信号的相

位趋于一致。

分频器(Divider): VCO 的输出信号通过分频器,将频率降低

到所需的最终输出频率。在这里,可以设置分频比,以确保最终输出

频率为 1GHz。

反馈回路: 分频器的输出连接到相比较器,形成反馈回路。这

使得锁相环能够不断调整 VCO 的频率,使输出信号与输入信号的相

位保持锁定。

请注意,锁相环电路的设计需要考虑相位噪声、环的稳定性等因

素。实际的设计可能会更加复杂,具体取决于应用的要求和所用技术

的复杂性。在实际应用中,可能需要使用 PLL 集成电路(PLL ICs)来

简化设计和提高性能。

2

弱电网条件下锁相环对LCL型并网逆变器稳定性的影响研究及锁相环参数设计1. 本文概述随着可再生能源的广泛应用和电力电子技术的发展,LCL型并网逆变器在弱电网条件下的稳定性问题引起了广泛关注。

本文旨在研究弱电网条件下锁相环(PhaseLocked Loop, PLL)对LCL型并网逆变器稳定性的影响,并提出一种有效的锁相环参数设计方法。

本文分析了弱电网条件下LCL型并网逆变器的工作原理,明确了锁相环在系统稳定性中的关键作用。

接着,详细探讨了锁相环对系统稳定性的影响机制,包括其对系统动态响应、谐波抑制以及系统抗干扰能力的影响。

进一步地,本文针对锁相环参数设计问题,提出了一种基于系统稳定性和动态性能综合优化的参数设计方法。

该方法不仅考虑了锁相环的快速性和准确性,还兼顾了系统在弱电网条件下的稳定性和鲁棒性。

通过仿真和实验验证,本文所提出的锁相环参数设计方法在提高LCL型并网逆变器在弱电网条件下的稳定性方面具有显著效果。

本文的研究成果对于促进可再生能源的高效利用和电网稳定运行具有重要意义,并为类似系统的设计和优化提供了理论指导和实践参考。

2. 型并网逆变器与锁相环的基本原理在弱电网条件下探讨锁相环(PhaseLocked Loop, PLL)对LCL 型并网逆变器稳定性的影响以及锁相环参数设计,首先需要理解并网逆变器和锁相环的基本原理。

LCL型并网逆变器是一种广泛应用在新能源发电系统中的关键设备,特别是光伏和风能发电系统中。

它的结构主要包括逆变器、LCL 滤波器和并网接口。

LCL滤波器由串联的电感(L)和两个并联的电容(C)组成,这种配置能显著减少输出电流的谐波含量,提高电能质量,同时降低了对电网的电磁干扰。

LCL滤波器引入了固有的三阶动态特性,可能会导致谐振现象,对系统稳定性构成挑战。

为了保证并网逆变器能在宽频范围内稳定且高效地工作,需要设计有效的电流控制器,并结合电容电流反馈实现有源阻尼,以抑制LCL滤波器产生的谐振。

基于改进型SOGI的锁相环设计OUYANG Sen;MA Wenjie【摘要】针对传统锁相方法的锁相精度在电网电压含有负序分量、谐波分量、直流分量等情况下有所降低的问题,提出一种基于改进型二阶广义积分器(SOGI)的三相锁相环设计方案.首先简要介绍了SOGI可进行信号正交处理的原理;然后通过频域分析法,直观地指出传统SOGI抗直流偏移干扰能力弱的原因,并量化分析了直流分量对基于传统SOGI的不平衡锁相环的影响;为增强SOGI对电压检测信号中直流分量的抗干扰能力,通过新增一条低通滤波通道对其进行结构上的改进,提出一种基于改进型SOGI的不平衡锁相环设计方案.仿真与实验结果表明文中理论研究是正确的.【期刊名称】《华南理工大学学报(自然科学版)》【年(卷),期】2018(046)010【总页数】8页(P1-8)【关键词】二阶广义积分器;锁相环;并网逆变器【作者】OUYANG Sen;MA Wenjie【作者单位】;【正文语种】中文【中图分类】TM464随着分布式电源并网发电技术的快速发展,诸如风力发电、光伏发电等在电力系统中的渗透率日渐升高[1- 2].电网基波电压相位和幅值信息的准确获取是分布式电源实现并网有功和无功功率控制的重要保证.由于实际中电网电压常因三相负荷不平衡、大量的非线性负荷接入和电网不对称故障而呈现三相不对称、谐波含量较高的现象,因此,对并网锁相技术提出了更高的要求[2].单同步坐标系软件锁相环(SRF-SPLL)具有结构简单、易实现的优点,获得了广泛应用.在电网不平衡情况下,受电压负序分量影响,其锁相的相位与频率误差增大,严重时甚至不能满足并网逆变器的控制需求[3- 4].文献[5]提出在SRF-SPLL之前加装低通滤波器以抑制负序分量的干扰,该方案虽可改善锁相环性能,但由于所用低通滤波器的截止频率较低,存在相角偏移、系统动态响应变慢等问题.文献[6]在SRF-SPLL结构中加入滤除二次谐波的陷波滤波器,通过频域内优化的设计方法设计了系统参数,达到响应速度和稳态误差的合理折中.为解决电网不平衡所带来的问题,文献[7]中提出基于双同步坐标系解耦的软件锁相环,利用正、负序两个同步坐标系通过交叉解耦来分离正、负序电压分量,具有较高的稳态精度,但是其依赖于相位反馈,因此当电网相位突变时,其过渡过程中存在超调较大、恢复时间较长等问题.为消除电网电压谐波对锁相环的影响,文献[8- 9]中采用双滑动平均滤波器来设计锁相环,锁相效果良好.文献[10]采用自适应观测器(FRF)来进行电网相位锁定,但是该算法程序计算量较大,比较复杂.为更好地提取出电压正序分量,文献[11- 14]提出采用二阶广义积分器作为正交信号发生器,来提取基波正序电压,之后再利用SRF-SPLL实现相角锁定.该方法不仅能实现不平衡电网下的准确锁相,且可以实现频率自适应滤波.在实际应用中,通常由于测量、数据转换和电网电压参数估计误差等原因导致检测到的电压信号中含有一定的直流分量,从而影响锁相环的锁相精度[13,15].例如,基于定点DSP(数字信号处理器)的光伏逆变器在对模拟电压信号进行A/D转换之前需要设置一个偏移量,使输入给A/D模块的信号是 0~3 V.经A/D转换之后的信号数据类型是无符号整型,再变换成有符号整型.在整个过程中,很难找到一种变换使转换前后的数据完全匹配.因此,针对前述电压测量中的直流偏移影响锁相环精度的问题,文中提出一种基于SOGI的改进型锁相环设计方案.通过对传统型SOGI进行结构上的改进,增强其对直流量的滤除能力,并以该改进型SOGI为基础,设计出能有效消除电压负序分量、测量偏移影响的三相锁相环,并利用仿真与实验对文中所提方案进行验证.1 不平衡电网锁相原理不平衡电网电压中含有正、负、零序分量,可具体表示如下[3]:(1)(2)(3)式中,vabc为不平衡电网电压,采用上标“+”、“-”、“0”来区分正、负、零序,va、vb、vc分别为a、b、c三相电压,vabc=[va vb vc]T,a为120°旋转因子,a=ej2/3.对于三相无中线系统,其不存在零序电流通路,因此以下分析和讨论均不考虑零序电压.对式(2)、(3)进行数学变换可得[3]:(4)(5)其中:q=ej/2,为90°相位滞后因子,分别为αβ坐标系中的电压正、负序分量.分析式(4)可知,通过对输入信号进行90°偏移处理,可提取出电网电压基波正序分量.2 二阶广义积分器由内模原理可知:若要实现对某一频率正弦信号的无差跟踪,则要求系统的开环传递函数中必须包含该正弦信号的内部模型.二阶广义积分器就是据此提出来的,其结构框如图1所示.图中,v为输入信号,ω′为滤波器中心频率,k为阻尼系数,v′和v″为经滤波器处理所输出的正交信号对,ε为v′和v″之差,s为拉氏变换算子.图1 SOGI控制框图Fig.1 Control block diagram of SOGI根据图1,可得输入信号v到输出信号v′和v″的传递函数D(s)与Q(s)的幅值和相位频率特性:(6)(7)图2是系统在不同k值时的伯德图.图2 SOGI的频率特性Fig.2 Bode plots of D(s) and Q(s)从伯德图中可以看出,SOGI具有选频特性,因此可以提取出基波分量.k越小,滤波性能越好,但是系统带宽将随之变小,从而导致动态响应变慢.因此,为兼顾滤波和响应快速性,常取根据上述分析可知,当滤波器的中心频率ω′与输入信号的频率ω相同时,则输出信号v′与v具有相同的幅值和相位,v″与v幅值相同,但是相位滞后90°.基于此,结合式(4),可设计出如图3所示的基于双二阶广义积分器的锁相环(DSOGI-PLL).其中,ω0为电网基波频率,θ*为锁相所得电压相位,vd、vq分别为电压正序分量在同步坐标系中的d轴与q轴分量,X表示乘法运算.图3 DSOGI-PLL结构框图Fig.3 Control block diagram of DSOGI-PLL3 SOGI的改进分析与设计在实际应用中,由于各种原因导致检测到的三相电网电压含有一定的直流量,具体如下:(8)式中,va0、vb0、vc0为直流偏移量,V为正序基波电压幅值.经Clark变换可得:其中,(9)(10)根据图3所设计的不平衡锁相环,可得从输入电压信号vα、vβ到提取出的正序分量的传递关系为(11)因此中所含直流量为(12)从图2中可知,D(s)是一个带通滤波器,其对直流量的滤除能力极强.为简化分析,可认为直流分量经过D(s)处理后衰减为零,而Q(s)是一个低通滤波器,据SOGI的频率特性可知其对直流量的增益为|Q(s)|ω=0=k(13)因此,式(12)可进一步简化为(14)设电网电压矢量相角为θ,锁相所得相角为θ*,将图3中所得变换到旋转坐标系中有(15)其中,(16)当锁相环处于稳态时,锁相相位误差较小,可认为式(15)中σ≈0,可得:(17)稳态时vq≈0,因此,由直流偏移所引起的相位误差为(18)设锁相环经锁相得到的电网频率中的误差成分为Δω,可得:(19)由式(18)、(19)可以看出,直流分量会导致锁相得到的相位与频率中含有频率与工频相同的交流成分,且该交流成分的幅值与直流分量的大小有关.因此,需对SOGI 进行结构上的改进,以消除掉直流偏移的影响.由图1可知:ε=v-v′,当系统处于稳态时,ε包含v中的所有直流分量.因此可以在ε经过增益k放大后,再通过低通滤波器处理后与v″做差,这样可彻底消除掉信号v″中的直流量.综上,文中提出一种改进型SOGI,其结构如图4所示,其中,T为新增支路中低通滤波器的时间常数.图4 改进型SOGI结构框图Fig.4 Diagram of the improved SOGI根据图4,有:(20)结合第2节的分析,可知与输入信号v的具体关系为(21)(22)将式(21)、(22)代入式(20)可得由输入信号v到v″的传递函数为(23)当输入信号频率为ω′时,根据式(23)可得:v″=-jv(24)其中,j为虚数单位.因此,改进后的SOGI良好地保持了原有的信号正交处理能力,G(s)的频率特性如图5所示.根据图5可知:①G(s)特性与带通滤波器相似;②图4中的低通滤波器的截止频率越高,对直流分量的滤除能力越强,当低通滤波器的截止频率取为20 Hz时,其在零频率附近的增益小于-40 dB,可以很好地滤除掉直流分量;③低通滤波器的截止频率越高,动态响应越快,但G(s)对高频干扰的抑制能力越弱.图5 G(s)的频率特性Fig.5 Bode plot of the transfer function G(s)综上,对于图4中低通滤波器截止频率的设计需综合考虑动态响应速度与高频衰减能力.由图2(a)可知D(s)在200 Hz频率处的增益约为-10 dB,因此,文中在设计低通滤波器时,以G(s)在200 Hz频率处的增益接近-10 dB为参考,最终取低通滤波器的截止频率为40 Hz.图6为G(s)在不同截止频率下的单位阶跃响应曲线.由图6可知,随着截止频率的升高,系统动态响应加快,调节时间缩短,对直流信号的衰减作用增强.当截止频率取为40 Hz时,稳定时间约为0.022 s,且稳态精度较高.图6 不同截止频率下G(s)的阶跃响应曲线Fig.6 Step response curves of G(s)at different cut-off frequencies4 仿真验证为验证文中理论研究的正确性,在PSCAD软件中分别搭建出单同步坐标系锁相环(I型)、基于传统型SOGI的不平衡锁相环(II型)、基于改进型SOGI的不平衡锁相环(III型)的仿真模型来进行对比验证,各锁相环的结构如图7所示.其中,基于传统型SOGI的不平衡锁相环的内部结构如图3所示,而基于改进型SOGI的不平衡锁相环的不同点在于图3中的DSOGI部分使用了改进型的SOGI.仿真时,3种类型锁相环结构中的PI控制器的参数均一致:比例系数为2,积分系数为3.图7 3种类型锁相环结构Fig.7 Structure diagram of three types of PLL仿真条件设定:①初始电网电压三相对称,其有效值为220 V,在0.25 s时,a 相电压跌落至50 V,在0.40 s时恢复正常;②初始电网电压三相对称,有效值为220 V,在0.60 s时,a相电压叠加上10 V的直流分量.两种条件下的仿真所得结果如图8、图9所示,仿真图形中为进行清晰对比,将各锁相环的锁相相位波形进行了纵轴偏移处理.图8 不平衡电网环境下的仿真结果Fig.8 Simulation results under the unbalanced grid voltage由图8可知:当电网电压不平衡时,单同步坐标系锁相环检测到的旋转电压矢量幅值存在约80V的二倍工频波动;锁相频率存在幅值约为20 Hz的二倍频分量,从而导致锁相相位也存在二倍频分量,稳态精度较低,锁相性能较理想电网环境下大幅下降.基于传统型SOGI的不平衡锁相环与基于改进型SOGI的不平衡锁相环在动态响应与稳态精度等方面的性能几乎一样.当设定a相电压的直流偏移量为10 V时,根据第3节的理论分析,由式(18)可得稳态时检测到的频率偏差理论值为-0.757 57cos(θ+φ)(25)图9 含直流偏移情况下的仿真结果Fig.9 Simulation results in the case of DC offset由图9(c)可知,基于传统型SOGI的不平衡锁相环在测量信号含有直流偏移的情况下,稳态时检测到的电网频率存在幅值为0.706 5 Hz的工频周期分量,与理论计算基本一致.采用改进型SOGI的不平衡锁相环稳态时检测到的电压矢量幅值误差约为0.065 V,频率误差波动分量幅值仅为0.045 Hz,根据Δω与相位误差之间的积分关系,可计算此时的相位误差(单位:rad)为-0.000 9sin(θ+φ)(26)因此,基于改进型SOGI的不平衡锁相环在测量信号含有直流分量的情况下仍具有较高的稳态精度.5 实验验证为进一步验证文中理论研究的正确性,基于DSP28335硬件平台编程实现了第4节中所述的3种类型锁相环,分别在不平衡以及不平衡电压伴随直流偏移的环境条件下进行各锁相环的性能实验.实验时,三相电网电压由电压信号发生装置模拟产生,三相电压数据由DSP的ADC模块以20 kHz的采样频率采样获得,实验所得数据均是以数组保存,从DSP内部读取得来,具体实验结果如图10、图11所示. 从图10可以得知,单同步坐标系因受负序电压的影响而导致锁相性能严重恶化,而基于传统型SOGI的不平衡锁相环和基于改进型SOGI的不平衡锁相环因进行了正、负序分离,在不平衡电网环境下均能保持良好的锁相性能.图10 不平衡电压条件下的实验结果Fig.10 Experiment results under unbalanced grid voltage分析图11可知,当三相电压中含有一定的直流分量时,基于传统型SOGI的不平衡锁相环经锁相所得到的电网频率存在明显的波动,进而导致锁相精度降低,而基于改进型SOGI的不平衡锁相环仍表现出良好的适应性,具有较高的锁相精度.需要说明的是,文中所设计的基于改进型SOGI的锁相环与基于传统SOGI的锁相环相比,其抗直流干扰的能力有较大提升,从频域上来说是对低频段进行了修正,但其对于5、7、9次等低次谐波的抑制能力并未增强.因此,文中所设计锁相环,在电网电压低次谐波含量较高时,其锁相精度会有所下降,有待进一步研究.图11 不平衡电压伴随直流偏移条件下实验结果Fig.11 Experiment results under unbalanced grid voltage with DC offset6 结论文中针对不平衡电网环境下并网逆变器的锁相问题进行了研究,通过仿真与实验得出以下结论:(1)当三相电网电压不平衡或含有直流分量时,单同步坐标系锁相环的锁相精度大大降低,已不适用于对并网逆变器进行控制;(2)基于传统型SOGI的不平衡锁相环适用于不平衡电网环境,但在电压检测信号含直流偏移的情况下其锁相性能变差;(3)基于文中所设计改进型SOGI的不平衡锁相环,在不平衡电网及电压检测信号含直流偏移的情况下均具有较高的锁相精度.参考文献:【相关文献】[1] MORENO V M,LISERRE M,PAGANO A,et al.A comparative analysis of real-time algorithms for power signal decomposition in multiple synchronous reference frames [J].Power Electron,2007,22(4):1280- 1289.[2] 曾正,赵荣祥,汤胜清,等.可再生能源分散接入用先进并网逆变器研究综述 [J].中国电机工程学报,2013,33(24):1- 12.ZENG Zheng,ZHAO Rongxiang,TANG Shengqing,et al.An overview on advanced grid-connected inverters used for decentralized renewable energy resources [J].Proceedings of the CSEE,2013,33(24):1- 12.[3] 张兴,张崇巍.PWM整流器及其控制 [M].北京:机械工业出版社,2012:410- 417.[4] 杨仁增,张光先.谐波畸变电网下的频率自适应锁相方法 [J].中国电机工程学报,2013,33(16) :144- 152.YANG Renzeng,ZHANG Guangxian.Frequency adaptive PLL under distorted grid conditions [J].Proceeding of the CSEE,2013,33(16):144- 152.[5] CARUGATI I,MAESTRI S,DONATO P G,et al.Variable sampling period filter PLL for distorted three-phase systems [J].IEEE Transactions on Power Electronics,2012,27(1):321- 330.[6] FRANCISCO D F,ALEJANDRO G Y.An optimized implementation of phase locked loops for grid applications [J].IEEE Transactions on Instrumention and Measurement,2011,60(9):3110- 3119.[7] 周元峰,段善旭,刘宝其,等.改进的解耦双同步坐标系锁相环的设计与实现 [J].电力电子技术,2012,46(8):68- 70.ZHOU Yuanfeng,DUAN Shanxu,LIU Baoqi,et al.The design and implementation ofan improved decoupled double synchronous reference frame PLL [J].Power Electronics,2012,46(8):68- 70.[8] 吕广强,纪海平,李嘉,等.一种基于双滑动平均滤波器的单相软件锁相环 [J].电力系统自动化,2015,39 (13):151- 157.LÜ Guangqiang,JI Haiping,LI Jia,et al.A single-phase software phase-locked loop based on double moving average filter [J].Automation of Electric Power Systems,2015,39(13):151- 157.[9] 刘华吾,孙永恒,胡海兵,等.谐波畸变电网下的单相同步旋转坐标系锁相环 [J].电力系统自动化,2016,40(13):93- 99.LIU Huawu,SUN Yongheng,HU Haibing,et al.Single-phase synchronous reference frame phase-locked loop under harmonic distorted power grid condition [J].Automation of Electric Power Systems,2016,40(13):93- 99.[10] 霍现旭,胡书举,许洪华.电网不平衡下基于自适应观测器的锁相环研究 [J].电力系统保护与控制,2013,41(15):120- 125.HUO Xianxu,HU Shuju,XU Honghua.Phase-locked loop algorithm based on adaptiveobserver under unbalanced grid voltage condition [J].Power System Protection and Control,2013,41(15):120- 125.[11] 罗劲松,王金梅,张小娥.基于dq锁相环的改进型光伏电站并网点电压跌落检测方法研究[J].电测与仪表,2014,51(5):51- 55.LUO Jinsong,WANG Jinmei,ZHANG Xiao'e.Research on improved grid-connected point voltage sag detection method of photovoltaic power station based on dq-PLL [J].Electrical Measurement & Instrumentation,2014,51(5):51- 55.[12] 陆原,汪周玮,郭素兵.基于单二阶广义积分器的三相数字锁相环设计[J].电测与仪表,2015,52(6):96- 101.LU Yuan,WANG Zhouwei,GUO Subing.Design of three-phase digital phase locked loop based on single second-order generalized integrator [J].Electrical Measurement & Instrumentation,2015,52(6):96- 101.[13] 闫朝阳,贺红艳,李建霞,等.电网电压不平衡时基于二阶广义积分器SOGI的2倍频电网同步锁相方法 [J].电源学报,2014(6):93- 100.YAN Zhaoyang,HE Hongyan,LI Jianxia,et al.Double fundamental frequency PLL with second order genera-lized integrator under unbalanced grid voltages [J].Journal of Power Supply,2014(6):93- 100.[14] SEN B,SHARMA D,CHITTI B B.DSRF and SOGI based PLL-two viable zcheme for grid synchronization of DG systems during grid abnormalities [C]∥Procee-dings of the 2012 Students Conference on Engineering and Systems (SCES).Allahabad,Uttar Pradesh:IEEE,2012:1- 6.[15] 吴晓波,赵仁德,胡超然,等.基于改进自适应陷波滤波器的锁相方法[J].电力系统自动化,2014,38(5):103- 108.WU Xiaobo,ZHAO Rende,HU Chaoran,et al.A phase-locked method based on enhanced adaptive notch filter [J].Automation of Electric Power Systems,2014,38(5):103- 108.。

基于PI 控制算法的三阶全数字锁相环的详细分析与

实验结果

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。

随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。

因此,对全数字锁相环的研究和应用得到了越来越多的关注。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。

对于高阶全数字锁相环,其数字滤波器常常采用基于DSP 的运算电路。

这种结构的锁相环,当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SOC(system on chip)的设计带来一定困难。

另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N 后M 序列滤波器等。

这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。

由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确定锁相环的设计参数。

不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用需求。

本文提出了一种基于比例积分(PI)控制算法的高阶全数字锁相环。

给出。

stm32数字锁相环频率追踪原理

STM32数字锁相环(Digital Phase Locked Loop,简称DPLL)是一种用于频率合成和时钟恢复的数字电路。

它的原理是通过比较输入信号和本地参考信号的相位差来调整本地时钟频率,以使两者保持同步。

在STM32微控制器中,数字锁相环通常用于时钟生成和恢复,以确保系统中各个部件的时钟信号同步和稳定。

数字锁相环的工作原理大致可以分为三个步骤,相位检测、数字控制和频率合成。

首先,输入信号和本地参考信号被送入相位检测器。

相位检测器比较这两个信号的相位差,并产生一个误差信号,该误差信号表示了输入信号和本地参考信号之间的相位偏差。

接下来,误差信号被送入数字控制环路,数字控制器根据误差信号来调整本地时钟的频率。

这个过程涉及到数字滤波、积分和微调等技术,以确保误差信号趋近于零,从而使本地时钟频率与输入信号保持同步。

最后,频率合成器根据数字控制器的输出来生成最终的时钟信

号。

这个时钟信号经过数字锁相环的调节后,频率和相位都与输入

信号保持一致。

在STM32中,数字锁相环通常用于时钟信号的生成和恢复,以

确保系统中各个模块的时钟同步和稳定。

通过调节数字锁相环的参数,可以实现对时钟信号的精确控制和频率追踪,从而满足不同应

用场景对时钟信号精度和稳定性的要求。

总的来说,STM32数字锁相环的频率追踪原理是通过相位检测、数字控制和频率合成等步骤来实现对输入信号的频率追踪和时钟恢复,从而保证系统中各个部件的时钟信号同步和稳定。

一种基于E-FLASH工艺的低功耗全集成锁相环作者:***来源:《现代信息科技》2020年第20期摘要:基于国内0.13 μm E-FLASH工艺,设计了一种由E-FLASH控制的锁相环芯片,为芯片提供可配置的频率源,内置LC压控振荡器、射频分频器、数字分频器、环路滤波器接口和电荷泵,实现了锁相环的全集成。

芯片功耗仅为30 mA,面积仅1 mm ×1.5 mm。

工艺可集成于E-FLASH工艺的片上系统,能提供良好的相位噪声和抖动特性,最高输出频率可达2.4 GHz,锁定后10 kHz频偏的相位噪声优于-116 dBc/Hz。

关键词:锁相环;E-FLASH;相位噪声中图分类号:TN432;TN911.8 文献标识码:A 文章编号:2096-4706(2020)20-0050-04An Integrated Low Power Phase Lock Loop Based on E-FLASH ProcessGU Shaohua(The 14th Research Institute of China Electronics Technology Group Corporation,Nanjing 210013,China)Abstract:Based on the domestic 0.13 μm E-FLASH process,a phase lock loop chip controlled by E-FLASH is designed to provide a configurable frequency source for the chip,built-in LC voltage controlled oscillator,RF frequency divider,digital frequency divider,loop filter interface and charge pump,which can realize the full integration of phase lock loop. The power of the chip is only 30 mA,and the area is only 1 mm ×1.5 mm. The process can be integrated into the system-on-a-chip of the E-FLASH process,which can provide good phase noise and jitter characteristics. The maximum output frequency can reach 2.4 GHz. The phase noise of the locked 10 kHz frequency offset is better than -116 dBc/Hz.Keywords:PLL;E-FLASH;phase noise0 引言隨着频率源技术的不断发展,锁相环的应用范围也在逐步扩大。

本科生毕业设计(申请学士学位)论文题目基于Matlab的数字锁相环的仿真设计作者专业名称电子信息工程指导教师2014年5月学生:(签字)学号:答辩日期:2014 年 5 月24 日指导教师:(签字)目录摘要 (1)Abstract (1)1 绪论 (2)1.1 本文研究背景 (2)1.2 本文研究意义 (2)1.3 锁相环和仿真方式 (2)1.3.1 锁相环 (2) (2)3 2 模拟锁相环Matlab仿真 (3)2.1 模拟锁相环方案 (3)2.1.1 模拟鉴相器 (3)2.1.2 模拟低通滤波器 (6)2.1.3 模拟压控振荡器 (7)2.2 模拟锁相环仿真 (8)2.3 本章小结 (9)3 数字锁相环Matlab仿真 (10)3.1 数字锁相环方案 (10)3.1.1 数字鉴相器 (10)3.1.2 数字滤波器 (12)3.1.3 数字压控振荡器 (13)3.2 数字锁相环仿真 (14)3.3 本章小结 (15)4 总结与展望 (15)参考文献 (16)致 (18)基于Matlab的数字锁相环的仿真设计摘要:锁相环是一种能够自动跟踪信号相位并达到锁频目的的闭环负反馈系统。

数字锁相环在无线电领域得到较广泛的应用和发展。

而且已经成为雷达、通信、导航等各类电子信号产品不可替代的元器件之一。

锁相环的窄带跟踪性能使其得到较广泛应用。

因为锁相技术在实际应用中较为复杂,所以锁相环的设计通常采用仿真设计这种方式。

本次设计采用Matlab这一软件进行辅助仿真设计,完全能达到设计预期的目标。

Matlab中的Simulink仿真软件,具有很强的灵活性和直观性。

本次设计所采用的方法是在simulink中搭建模拟锁相的模型,并对模拟锁相环的组成、结构、设计进行不断的分析和改进。

然后根据模拟锁相环的原理进行改进,并搭建数字锁相环。

关键词:锁相环;自动跟踪;matlab;simulinkSimulative design of digital phase-locked loop based onMatlabAbstract:PLL is the automatic tracking system of close loop atracking signal phase. It is widely used in various fields of radio. It has become an irreplaceable part of radar, communication, navigation and all kinds of electronicsignal device. PLL is able to be widely used. Because, it has unique narrow-band tracking performance. However, because of the complexity of phase lock technique, for the design of PLL have brought great difficulty. This design uses Matlab, the simulative software for design assistance, can completely meet the design expectations. Simulink simulative software on Matlab, has strong flexibility and intuitive. Methods used by this project is to build the analog phase locked in the Simulink model, and the composition, structure, design of analog phase-locked loop of continuous improvement and analysis. It improved according to the principle of analog PLL, build digital phase-locked loop in Simulink, and then reach the simulation design of digitalphase-locked loop based on Matlab the design objective .Key words: PLL, Automatic tracking, Matlab, simulink1 绪论1.1 本文研究背景19世纪30年代法国H.de Bellescize首次提出同步检波这一概念,并且设计出锁相环电路这一划时代的研究成果[1]。

第27卷第8期2005年8月 电子与信息学报

Journal of Electronics&Information TechnologyVo1.27No.8

Aug. 2005

一种大频偏和低信噪比条件下的全数字锁相环设计 帅涛刘会杰梁旭文(中国科学院微小卫星联合重点实验室杨根庆

上海200050)

摘要:全数字锁相环设计是相干解调全数字接收机载波同步和位同步的关键技术,而大频偏和低信噪比分别从两个方面增加了环路设计的难度。该文在此背景下,以捕获时间和跟踪性能为指标,从模拟环路分析出发,给出一种适用于大频偏和低信噪比条件的全数字锁相环设计。关键词:数字锁相环,多普勒频偏,低信噪比,同步中图分类号:TN911.8文献标识码:A文章编号:1009-5896(2005)08-1208-05

The Design of DPLL for Low SNR Signals with Large Frequency OffsetShuai Tao Liu Hui一ie Liang Xu-wen Yang Gen-ping(Micro-satellite State Key Joint Laboratory, Chinese Academy of Sciences, Shanghai 200050, China)

Abstract The digital phase-locked loops design is a key technology for carrier and bit synchronization in coherentdemodulation digital receiver. Large frequency offset and low SNR add more dificulties of the loop design from twodiferent ways. Based on this condition, aim at fast acquisition and tracking, a method of digital loop parameter algorithmis proposed in this paper and some useful conclusions are given. Key words

1引言Digital Phase-Locked Loop(DPLL), Doppler frequency offset, Low SNR, Synchronization

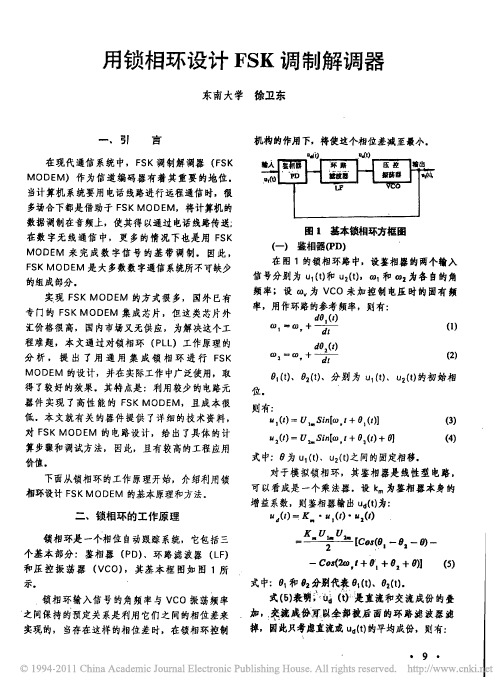

锁相环((PLL)是一个能够跟踪输入信号相位的闭环控制系统,在相千通信中,通常采用锁相环实现载波同步和位同步[[1,21,环路设计在很大程度上决定了通信系统的性能。由于通信条件的不同,常常对环路设计有不同的要求。 为了增强保密性和可靠性,现代通信系统广泛采用扩频技术和前向纠错编码技术,以降低正常工作所需信噪比,进而提高系统容量。另外,在突发数据通信中为提高系统效率,要求用于同步的前导字尽量短,这些导致锁相环设计难度增大。另一方面,由于通信双方相对移动产生多普勒效应使接收信号产生较大频偏。在低轨卫星通信系统中,该频偏可以与数据速率相当,此时采用锁相环实现同步也对环路设计提出了较高要求。 对于低信噪比或者大频偏下的环路设计已有较多深入的分析[[3-51,但对低信噪比和大频偏共存条件下实现信号快速捕捉和跟踪的环路设计研究还不多,对此,本文提出了一种环路设计思路。文章第2节从模拟锁相环出发,对比分析了法,第3节讨论了在大频偏、低设计,及相应的仿真结果,最后

2环路设计:从模拟电路到数字电路 锁相环的基本结构包括:鉴相器((PD),环路滤波器((LF)和压控振荡器(VCO),它们构成一个负反馈控制系统,其原理如图1所示:

图1锁相环的基本结构2.1模拟环路基本参数 LF的结构决定了锁相环的类型,这里主要讨论当LF为一阶有源低通滤波器时构成的二阶二型模拟环路。其基本参数有[11 LF传递函数:F(s) =(l+sr2)/(sr}) (1)

系统传递函数: K(1+sr,) 24ov_s+m? t1(s)=—=—几‘, s-叭+ SK几+K s-+L}wj+叮

其中K为环路增益,(0.为自然谐振频率,杏为阻尼系数,

、.户

、.

产

凡j4了

‘,

、

了吸、

它们与电路参数Ti > r2满足如下关系: fBn = K l z, 咨=(z2/2)了 K/z,

2004-03-15收到,2005-01一17改回第8期帅涛等:一种大频偏和低信噪比条件下的全数字锁相环设计1209

一般地,从一个模拟低通系统到一个数字低通系统的实现方法有脉冲响应不变法和双线性变换法。下面针对环路设计进行讨论:2.2两种数字环路实现方法 对于模拟积分器传递函数1/s,采用脉冲响应不变法可以得出数字域传递函数为T/(,一z-}),考虑到数字环路硬件实现时,反馈运算结果将至少产生一个采样点的延时,这样系统NCO的传递函数表达为(z-i约/(‘一z-}),由此可以得出对应的二阶数字环路相位模型如图2所示。

3大频偏和低信噪比条件下的环路设计 为了便于分析,这里先假设环路己经完成对载波频率捕获,同时二阶环的环路滤波器的设计满足基于维纳理论的优化值[61,即咨二行/2,下面分析固有频率然的设置与环路跟

踪性能。3.1跟踪环路固有频率设置 假设输入载波的相位可以表达为 9(t)=ee十△u)t +生Rte+上Lt} (11) 2 3!

其中R为频率变化率,L为频率变化率的导数,对该信号采用二阶二型环路进行跟踪,其稳态误差为

图2数字锁相环相位模型B(二)=)鳃sO(s)H(s)

对应式((1), (3), (4)可得到数字环路参数如下:=lim s么8又—十

△。R L、s2

一下尸+一丁十-了)xes犷卜二下一一-尸一了s- s- s s一十乙‘叭s十然

C,=2枷T l凡戈)(5)

C2=心T 21 (KdK.) (6) 现在从双线性变换法出发,考虑到要求数字环路低频斜摊删应,取:=(2/T平z一 })小z})代入式((2),

得到H(z) (46w-T +耐T2、十2耐T2Z-,十(002T 2一4,cm-T)z-2

(4 +4C;COnI +W}- I一)+(lwnL一tf)Z‘+(4一41;L&1 +(0;-l一)Z- (7)而图2所示的数字环路表达式可以表示为

=0+0+R/《+二其中第3项在时域可以表示为‘(,)二(L/W.') t,,>0(12)

假设要求环路在工作时间t.,k内的相位跟踪误差小于a弧度,则对于一个相位可以表示成式((11)的信号,对系统有如下要求:R Li + z two*CJn }n

H'(z)二KoKd (CI + C2 )Z-,一K.KdCIZ-21+[KoKd (C,+CZ)一2]z-'+(1一K.KdCI )Z-2(8)

取式((}), (8)分母相等,可以得到数字环路参数如下:C,二 ̄一一 ̄一 K .Y

8纯,T

4+4纵T+《T2(9)

C2=1 4心T2KeKd 4+4}0uT+《T2(10)

COn>_JIR+Lt,., I /a (13) 式((13)给出了在频率变化时,环路固有频率w.设置的下限,若不存在大的频率变化,则环路带宽的下限由晶振和VCO相位噪声决定[I)。下面从信噪比和跟踪性能角度分析环路固有频率oj设置的上限。 环路输入端的高斯噪声在经锁相环后,等效为相位噪声可表示为。,51

2.3对比分析 r匕较式(5), (6)和式(9), (10)可知,在mnT比较小时,两式得出的参数值相近。当固有频率Con增加时,由于数字环路反馈时延以及频域混叠效应,环路工作情况变差,仿真表明,脉于I时,容易发生振荡的压缩作用,在较高环路变换法实现从模拟域到范围内具有普适性,这信噪比下的载波同步环

2a}.=( sN〕一BL (14);式中B;为前置滤波器带宽,(SIN),为输入信号功率和通过前置带宽的噪声功率之比,B:为环路噪声带宽,对于二阶二型环,有BL=8} (1+“”(15)

环路对噪声的抑制能力可以通过环路信噪比反映出来,其定义为[S、1‘S、B.1一1=-=I,1一(10)IN少:嵘no }N)i风1210电子与信息学报第27卷 相位噪声引起误码率的恶化在文献[51中有详尽的分析,对于给定的目标,可以计算出对应的环路信噪比,并由此可以推出低信噪比下环路固有频率的上限:W.<_, 8李 ,x1slx(s丫xB; (17)

1+4右‘又N)r \N)L 为了在低信噪比下实现恶化误码率和周期滑动概率[[41比理想误码率低一个数量级,环路信噪比一般设置在I MB以上。3.2跟踪环捕获性能分析 对于前面设计的跟踪环路,现在考虑其捕获性能。这里以低轨卫星通信系统为实例作分析。 轨道高度为700km的低轨卫星,载波频率为450MHz时,多普勒频偏181在士9 kHz以内,频移变化率最大值为70Hz/s,频移变化二阶导数最大值为0.42 Hz/s2,并假设环路工作时间为卫星最大过境时间550s,且要求相位偏移最大值为)r/6,代入式(13)可得环路固有频率下限为60rad/sa 对于固有频率上限,假设输入信噪比为4dB,数据速率为4.8kbps,成型滤波器滚降系数为0.4,环路信噪比为1MB,代入式((17)可得固有频率上限为798rad/s. 对于大频偏下的载波同步,一般先采用扫频等辅助捕获手段将频偏缩小到11(4T),然后启动环路进行频率捕获和跟踪。而理想二阶环路的快捕带[[}l为:

AWL=2纵(18) 若采用前面分析的跟踪锁相环进行频率捕捉,在固有频率取最大值时,环路的快捕带为1117.2rad/s,小于最大频偏值1/(4T) (7536rad/s),而环路经周期跳越将频差从超过快捕带的频偏△CO.下降△WL需要的时间151为 ,,二(Og ) /(2粼)(19)

将前面结果代入式((19)可得t,为80ms o这个结果表明,对于以突发方式传送的上行短数据业务在帧长度为1 kbit时,用于同步的前导头消耗将达到30%左右。为了提高系统效率,降低前导头的消耗,对环路的改进是必要的。3.3频率辅助捕获锁相环设计

行

图3中下半部分为锁相环,用于载波跟踪,其参数设计和前面分析一致。上半部分为锁频环,用于大频偏的辅助捕捉。匹配滤波用于对下变频后的信号进行最佳接收,同时滤除载波高频分量。 根据不同的控制策略和系统要求,锁频环对锁相环的辅助有不同的几种方式。下面先分析锁频环的工作情况。 这里仍采用数据数率为采样率输入环路,同时假定位同步已经完成。鉴频输入(前导字部分)采用BPSK调制,可以推出如下鉴频方程:气△,)=Psin(AwT) =(I(n)Qc,一)一I (.-,)Q(.)) sgn(I (.)I (n-b+Q(n)Q(n-I)) (20)