基于FPGA的全数字锁相环的设计与应用

- 格式:pdf

- 大小:5.37 MB

- 文档页数:66

应用于数字锁相环的NCO设计保玲;佘世刚;周毅;金玉琳【摘要】本文鉴于数字锁相环在实际应用中对信号频率的准确度和稳定度有较为严格的要求,设计一种应用于数字锁相环的数控振荡器(NCO,Number Controlled Oscillator)。

基于直接数字频率合成(DDS)技术,介绍NCO工作原理,基于FPGA实现NCO,关键是相位累加器与波形存储器两个模块的设计,并利用QUARTUS对设计结果进行编译仿真。

对NCO杂散信号进行频谱分析,并提出解决方法。

该设计有效抑制杂散,修改灵活,便于调试,在数字锁相环设计中可有广泛应用。

%Based on the high standard for veracity and stability of signal frequency applied in digital PLL,a kind of NCO(Number Controlled Oscillator) is designed applied in digital PLL.Based on DDS(Direct Digital Frequency Synthesizers),the basic principle of NCO is introduced,NCO is realized based on FPGA.The key point is how to design phase accumulator and ROM,the design result is complied and simulated with applied software tool QUARTUS.The frequency spectrum of NCO is analyzed,and the resolve measure is given.This design can control spurious,modify conveniently,it has widely application in design of digital PLL.【期刊名称】《电子设计工程》【年(卷),期】2011(019)014【总页数】3页(P160-162)【关键词】NCO;DDS;杂散;FPGA【作者】保玲;佘世刚;周毅;金玉琳【作者单位】兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000【正文语种】中文【中图分类】TN802数字锁相环已在数字通信、无线电电子学及电力系统自动化等领域得到广泛应用。

一、引言数字锁相环(DPLL)是一种相位反馈控制系统。

DPLL通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

本文采用超前-滞后型数字锁相环(LL-DPLL)的设计方案,在LL-DPLL中,DLF用双向计数逻辑和比较逻辑实现,DCO采用加扣脉冲式数控振荡器。

这样设计出来的DPLL 具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

二、数字锁相环的分类1.过零型数字锁相环路这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行A/D变换,得到数字相位误差信号输出。

2.触发器型数字锁相环路这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。

其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置“ 0”和置“ 1” 的时间间隔内,得到相位误差信号。

置“ 0”和置“ 1”的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

3.超前-滞后型数字锁相环路这种数字锁相环路采用的鉴相器是超前-滞后型数字鉴相器。

超前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。

因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。

然后将误差相位的超前或滞后信息送到序列滤波器,产生对DCO的“ 加” 或“ 扣” 脉冲控制指令去改变DCO的时钟周期,使本地估算信号的相位输入信号相位靠拢。

4.奈奎斯特速率采样型数字锁相环路在这种数字锁相环路中,对输入信号的采样按照奈奎斯特速率进行。

也就是说,对输入信号进行A/D变换的采样频率必须按照奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。

A/D变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

三、系统设计本设计是基于直接数字频率合成器(Direct Digital Synthesizer)原理的信号发生器,用硬件描述语言Verilog来编程,用Altera公司的开发平台QUARTUSⅡ6.0来仿真,最后下载到StratixⅡ系列的EP2S60器件中进行验证。

基于FPGA的全数字锁相环设计与实现一、前言全数字锁相环(Digital Phase-Locked Loop,简称DPLL)是一种数字电路设计技术,可实现同步数字信号的调制和解调。

基于FPGA的全数字锁相环设计与实现,是一个极为重要的课题。

它可以有效地提高数字电路的性能,使得数字系统具有更优越的特性,并可广泛应用于数字电路的设计、数字信号的处理等领域。

二、DPLL 的体系结构DPLL是由相频检测器、滤波器、数字控制振荡器和时钟输出等多个部分组成的。

其中,相频检测器、滤波器和数字控制振荡器通常被集成到FPGA的内部,而时钟输出则需要通过FPGA的普通I/O口与市场上常见的外部输出设备相结合。

三、数字锁相环的工作原理数字锁相环的工作原理基于一个反馈循环系统,其中参考振荡器的频率与输入信号会被比较,然后通过差错检测网络来确定缺陷。

如果这些信号频率不匹配,则通过调整数字控制振荡器的频率来达到匹配。

然后,系统会根据输出信号和参考信号的相位差异来调整数字控制振荡器的频率,并通过PLL的反馈路径传输至输入端,进而得到和参考信号相同频率的输出信号。

四、数字锁相环的应用数字锁相环在通信领域有着广泛的应用,如数据码隆、数字调制、同步检测等;在数字领域,数字锁相环主要应用于数字信号处理、频谱分析、信噪比提高等方面;在电子仪器领域,数字锁相环可以被应用于测量领域、噪声分析、频率合成等方面。

五、基于FPGA的数字锁相环的设计数字锁相环的设计是一项非常复杂的工作,其中需要解决的问题主要有相频检测、低通滤波、数字控制振荡器的设计和时钟输出等方面。

在基于FPGA的数字锁相环设计过程中,可以采用很多不同的方法和技术来解决这些问题。

在数字锁相环的设计中,相频检测器是极其关键的部分,其主要功能是检测输入信号与数字控制振荡器的频率是否匹配。

其中,相频检测器常用的方式有两种:一是通过比较输入信号和数字控制振荡器的频率来实现;二是通过测量输入信号和数字控制振荡器的相位差来实现。

目录第一章绪论...................................... 错误!未定义书签。

1.1锁相环技术的发展及研究现状................................................... 错误!未定义书签。

1.2课题研究意义 .............................................................................. 错误!未定义书签。

1.3本课题的设计内容....................................................................... 错误!未定义书签。

第二章 FPGA的设计基础............................. 错误!未定义书签。

2.1硬件设计语言-Verilog HDL..................................................... 错误!未定义书签。

2.2 FPGA的设计流程 ......................................................................... 错误!未定义书签。

第三章锁相环的原理. (2)3.1全数字锁相环基本结构 (3)3.2全数字锁相环的工作原理 (4)第四章数字锁相环的设计 (5)4.1基于FPGA的数字锁相环总体设计方案 (5)4.2数字鉴相器的设计 (6)4.3 K变模可逆计数器的设计 (7)4.4脉冲加减器的设计 (10)4.5 N分频器的设计 (12)第五章实验仿真与调试 (14)5.1数字锁相环的仿真 (14)5.2数字锁相环的系统实验 (15)结束语 (19)参考文献 (20)附录 (21)第一章锁相环的原理许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

全数字锁相环及其数控振荡器的FPGA设计作者:邵帅李曼义刘丹非和伟李树晨来源:《现代电子技术》2008年第10期摘要:全数字锁相环(ADPLL)在数字通信领域有着极为广泛的应用。

由于SoPC技术的发展和FPGA的工作频率与集成度的提高,在1块FPGA芯片上集成整个系统已成为可能。

以片内同时嵌入CPU和全数字锁相环为目的,结合现阶段的相关研究成果,简单介绍片内全数字锁相环系统的结构和全数字锁相环的工作原理,详细论述一种可增大全数字锁相环同步范围的数控振荡器的设计方法,并给出部分VHDL设计程序代码和仿真波形。

在此数控振荡器的设计中引入翻转触发器的概念,并通过改变翻转触发器的动作特点,使得数控振荡器的输出频率提高,以达到增大全数字锁相环同步范围的目的。

关键词:全数字锁相环;数控振荡器;翻转触发器;VHDL;SoPC;中图分类号:TN76 文献标识码:B文章编号:1004-373X(2008)10-001-02Design of All Digital Phase-locked Loop(1.Physics and Electronics Information Institute,Yunnan Normalputer Science and Information Technology Institute,Yunnan NormalAbstract:All Digital Phase-Locked Loop (ADPLL) is generally used in digital communication field.The whole system on chip can be achieved due to development of SoPC and FPGA.Considering the relevant research achievements and the techniques of embedded CPU and ADPLL,the system structure and the principle of ADPLL is introduced in the paper.A design way of a digital control oscillator that will increase synchronous range of ADPLL is discussed in detail,and the partial VHDL code and simulation waveform is given.In this design,toggle flip flop is mentioned.Output frequencyKeywords:all digital phase-locked loop;digital control oscillator;toggle flip与传统的模拟锁相环相比较,全数字锁相环(ADPLL)在抗干扰能力和可靠性方面都有着明显的优势。

安路fpga锁相环用法

安路FPGA锁相环的使用方法如下:

1. 添加IP核:使用MegaWizard工程规范,将其添加到ipcore文件夹下。

设置相关参数,例如速度等级,以及是否添加异步复位、locked信号等。

locked信号用于表示锁相环的稳定性,并在时钟自锁时自动复位。

2. 配置输出时钟:包括频率、相位和占空比。

3. 编写激励文件模板:在Processing-Start-Start Test Template Writer

中创建并保存。

在Assignment-Setting-Stimulation中编译。

4. 设计复位信号:在系统锁相环不稳定或系统复位信号有效时,输出复位信号。

例如,可以assign rst_n=sys_rst_n&locked来实现这一功能。

建议查阅安路FPGA的技术手册,以获取更多信息。

同时请注意,具体使用步骤可能会根据FPGA型号有所不同,请以实际产品为准。

全数字锁相环的设计及分析1 引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

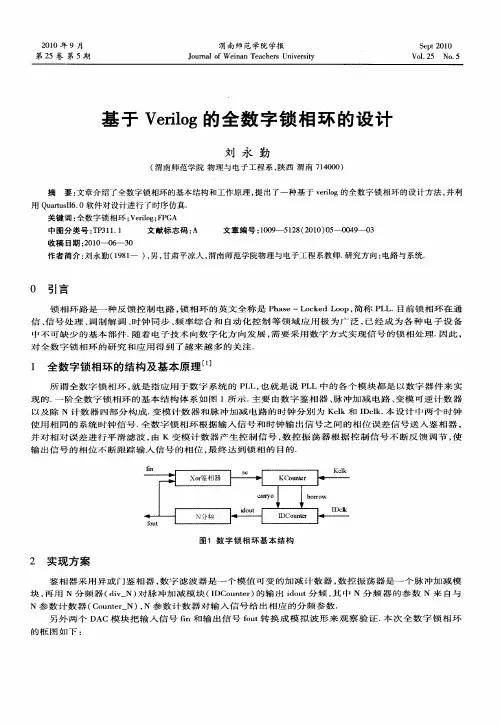

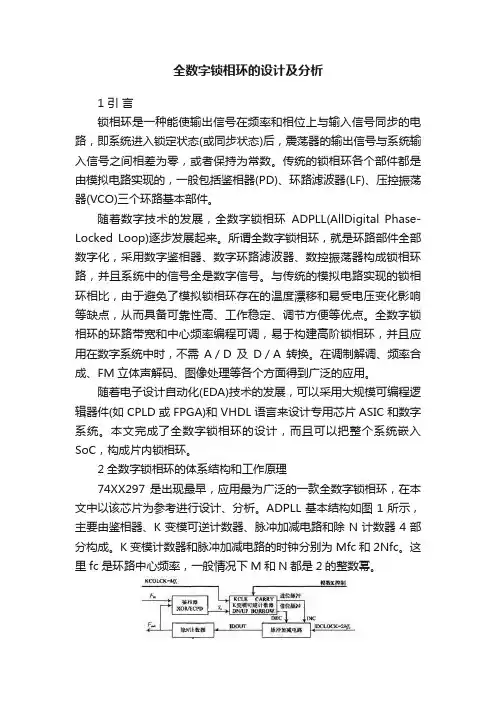

2全数字锁相环的体系结构和工作原理74XX297 是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1 鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

一种基于FPGA的全数字锁相环设计作者:陈华君, 杨涛来源:《物联网技术》2011年第10期摘要:给出了使用verilog HDL语言对锁相环进行基于FPGA的全数字系统设计,以及对其性能进行分析和计算机仿真的具体方法。

该方法采用综合仿真工具Quartus Ⅱ8.0来对数字锁相环进行输入设计、功能时序仿真及器件编程。

仿真结果表明:该方法可通过在传统数字锁相环基本结构的基础上增加自动变模控制模块来有效解决缩短捕捉时间和减小同步误差之间的矛盾。

关键词:FPGA; verilogHDL;全数字锁相环(DPLL);自动变模中图分类号:TN914.3 文献标识码:A文章编号:2095-1302(2011)10-0076-03Design of DPLL Based on FPGACHEN Hua-jun, YANG Tao(UESTC, Chengdu 611731, China)Abstract: A DPLL based on FPGA by using verilog HDL language is introduced for analyzing the system perfor-mance and computer simulation. A comprehensive simulation tool Quartus Ⅱ 8.0. was used to perform input, functional and timing simulation and device programming for digital phase-locked loop. Simulation results show that the automatic variable module should be added to the traditional digital PLL to shorten the capture time and reduce the conflict among the synchronization error.Keywords: FPGA; verilogHDL; DPLL; automatic variable module0 引言数字锁相环中的数字环路滤波器是由模数为K的可逆计数器构成。

科技与创新┃Science and Technology&Innovation ·138·2020年第17期文章编号:2095-6835(2020)17-0138-02一种FPGA实现的全数字锁相环*阎昌国,李青,马登秋,安玉(遵义师范学院工学院,贵州遵义563006)摘要:锁相环技术是新能源并网发电的关键技术之一。

针对传统锁相环存在零点漂移、精度低、易受温度影响的缺点,提出了一种用FPGA实现的全数字锁相环。

详细分析了全数字锁相环的工作原理,完成了该全数字锁相环的FPGA设计与实现。

最终通过逻辑仿真与实验证实,该全数字锁相环能有效地跟踪电网电压的频率与相位,具备精度高、不受温度影响、具备可编程能力等优点。

关键词:锁相环;全数字;FPGA;逻辑仿真中图分类号:TM46文献标识码:A DOI:10.15913/ki.kjycx.2020.17.059随着科学技术的快速发展,锁相环技术已被广泛地应用在了通信、测量、自动控制等领域[1-3]。

面对当下改善生态环境、解决能源短缺的紧迫问题,诸如太阳能、风能、核能等新能源发电成了良好的方案,其并网运行的应用便成为了潮流趋势[4-6]。

其中,新能源发电系统能否实现并网运行,关键技术就在于锁相环是否能够有效并准确地保证并网逆变器输出的电流始终跟随电网电压的频率与相位。

而传统的锁相环主要由模拟电路实现,因存在直流零点漂移与器件饱和现象,易受温度与电源的影响,会导致锁相环跟踪精度下降[7]。

EDA(电子设计自动化)技术的发展,为克服模拟电路固有缺陷实现全数字化提供了良好的路径[8]。

为此,本文以FPGA(现场可编程门阵列)为载体,提出了一种全数字锁相环的实现方案,详细分析了该方案的工作原理,通过逻辑仿真与实验结果表明该方案能有效地跟踪电网电压频率与相位,可以应用到新能源并网发电系统中。

1工作原理分析全数字锁相环的原理图如图1所示,它主要由鉴相器、K模可逆计数器、脉冲加减控制电路与N分频电路四个部分组成。

1.设计要求利用MAX PLUSII软件工具,设计一个全数字锁相环路,通过它从19.2k的信号中提取同步信号。

本地源时钟为11.0592MHz。

要求实现的功能:a当远端信号(方波)的占空比分别为1:1、1:3、1:5和1:7时,从其中提取同步信号。

b先将远端信号(方波)转变成伪随机序列,然后从中提取同步信号。

完成仿真过程,给出测试结果,要求得到同步带宽、捕捉带宽和最大同步时间。

2.设计原理2.1数字锁相环基本原理一个典型的锁相环(PLL)系统,是由鉴相器(PD),压控荡器(VCO)和低通滤波器(LPF)三个基本电路组成,如图1所示。

图1 PLL模块图传统的锁相环是模拟电路,它利用环路中误差信号去连续地调整位同步信号的相位。

全数字锁相环路完全用数字电路构成,采用高稳定度的振荡器(信号钟),从鉴相器所获得的与同步误差成比例的误差信号不是直接用于调整振荡器,而是通过一个控制器在信号钟输出的脉冲序列中附加或扣除一个或几个脉冲,这样同样可以调整加到鉴相器上的位同步脉冲序列的相位,达到同步的目的。

全数字锁相环(ADPLL)由数字鉴相器(DP)、数字滤波器(DF)与数字压控振荡器(DCO)三个数字电路部件组成,如图2所示。

图2 ADPLL模块图2.2数字锁相环原理框图本设计中的数字锁相环由信号钟、控制器、分频器、相位比较器组成。

其原理框图如图3所示。

图3 数字锁相环原理框图信号钟包括一个高稳定度的晶体振荡器和整形电路。

若接收码元的速率为F=1/T,那么振荡器频率设定在nF,经整形电路之后,输出周期性脉冲序列,其周期T0=1/(nF)=T/n。

本设计中时钟为11.0592MHz。

控制器包括图中的扣除门(常开)、附加门(常闭)和“或门”,它根据相位比较器输出的控制脉冲(“超前脉冲”或“滞后脉冲”)对信号钟输出的序列实施扣除(或添加)脉冲。

分频器是一个计数器,每当控制器输出n个脉冲时,它就输出一个脉冲。

控制器与分频器的共同作用的结果就调整了加至相位比较器的位同步信号的相位。

8期侯卫民等:基于FPGA的数字锁相环的研究与实现或者滞后输入码元相位大于相位调整步长时,锁定检测器的输出信号lock为低电平,环路进入调整状态。

图4锁定检测器模块3.4数控振荡器的设计数控振荡器的功能是产生同步时钟信号,它的控制信号来自数字滤波器的输出信号inc和dec以及锁定检测信号lock,本文中的数控振荡器是由添扣门和m分频器(本文中m取值为16)构成,与门1、与门2、与门3构成添门,与f-I4构成扣门。

在系统没有到达锁定状态时,/lock信号保持高电平,若滤波器输出了一个扣脉冲信号dec加到扣门,扣除一个时钟周期,这样分频器的输出脉冲相位就滞后了1/m图5数控振荡器模块个周期。

若滤波器输出了一个添脉冲信号到添门,控制添门打开,加入一个晶振脉冲(clk64M)到或门。

由于添加到添门的时钟信号(clkl6M2n)与添加到扣门的时钟信号(clkl6M1)频率相等,相位相差900,即这两路时钟信号在时间上是错开的,因此当从添门加入一个晶振脉冲到或门时,相当于在扣门输出的晶振信号中间插入了一个窄脉冲,就是分频器输入端添加了一个脉冲,这样分频器输出相位提前了1/m周期,整个数字锁相环按上述方式,反复调整本地时钟相位,直到本地同步时钟信号相位滞后输入码元小于2宵r/m,此时锁定检测信号/lock变为低电平,这时或门的输出信号就是clkl6M1,经过m分频器后,本地同步信号不再发生相位改变。

4仿真结果j7针对上面的设计,用VHDL语言在ISE7.1开发环境下,实现了数字锁相环的设计,并在Modelsim6.0下进行仿真,结果如下图所示。

图6有相位检测器情况的系统仿真波形98微计算机应用2008矩图7无相位检测器情况的系统仿真波形图6表示有相位检测器情况的系统仿真波形图,由图6可以看出,在环路工作初期本地时钟信号滞后与输人码元,经过环路的反复跟踪,在30us左右系统进入锁定状态,此时本地时钟信号相位滞后于输入码元并且滞后相位小于调整步长,因此锁定检测器输出为高电平,本地同步时钟相位不再进行调整图7是没有相位检测电路的仿真结果,可以看出,系统在30us时系统进入锁定状态后,系统仍然进行不断的相位调整,从而导致本地同步信号的相位抖动。

基于FPGA的全数字锁相环的设计与实现一、本文概述本论文聚焦于基于现场可编程门阵列(FieldProgrammable Gate Array, FPGA)技术设计与实现全数字锁相环(AllDigital PhaseLocked Loop, ADPLL)的研究工作。

全数字锁相环作为一种关键的信号处理模块,广泛应用于通信系统、雷达系统、高速数据采集、频率合成等领域,其性能直接影响到整个系统的稳定性和精度。

随着FPGA技术的发展,ADPLL在灵活性、集成度、可编程性及实时调整等方面展现出显著优势,成为现代电子系统中实现高精度频率合成与同步控制的理想选择。

本文旨在深入探讨基于FPGA平台构建全数字锁相环的理论基础、设计方案及关键技术,并通过实际工程实践验证其性能。

研究内容主要涵盖以下几个方面:理论背景与技术综述:对全数字锁相环的基本原理、组成结构以及工作模式进行全面阐述,对比分析其与传统模拟锁相环和混合信号锁相环的优缺点。

在此基础上,详细介绍FPGA技术的特点及其在ADPLL设计中的应用价值,为后续设计工作奠定理论基础。

系统架构与模块设计:详细阐述所设计的基于FPGA的全数字锁相环的整体架构,包括鉴相器(Phase Detector)、数字环路滤波器(Digital Loop Filter)、数控振荡器(Digitally Controlled Oscillator, DCO)等核心组件的设计思路与实现细节。

针对FPGA资源特性,优化各模块算法及硬件实现,确保其在有限逻辑资源下达到高性能指标。

关键算法与技术实现:探讨用于提升ADPLL性能的关键技术,如低噪声鉴相算法、快速锁定策略、频率牵引与抖动抑制技术等,并展示如何将其有效融入FPGA实现中。

同时,阐述如何利用FPGA的可编程特性实现实时参数调整与在线监控,增强系统的动态适应能力和故障诊断能力。

仿真验证与实验结果:通过高级硬件描述语言(HDL)对设计进行建模,并利用FPGA开发环境进行功能仿真与时序分析,验证设计的正确性和稳定性。