新型全数字锁相环的逻辑电路设计动态参数调节

- 格式:pdf

- 大小:185.35 KB

- 文档页数:4

一、引言数字锁相环(DPLL)是一种相位反馈控制系统。

DPLL通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

本文采用超前-滞后型数字锁相环(LL-DPLL)的设计方案,在LL-DPLL中,DLF用双向计数逻辑和比较逻辑实现,DCO采用加扣脉冲式数控振荡器。

这样设计出来的DPLL 具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

二、数字锁相环的分类1.过零型数字锁相环路这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行A/D变换,得到数字相位误差信号输出。

2.触发器型数字锁相环路这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。

其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置“ 0”和置“ 1” 的时间间隔内,得到相位误差信号。

置“ 0”和置“ 1”的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

3.超前-滞后型数字锁相环路这种数字锁相环路采用的鉴相器是超前-滞后型数字鉴相器。

超前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。

因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。

然后将误差相位的超前或滞后信息送到序列滤波器,产生对DCO的“ 加” 或“ 扣” 脉冲控制指令去改变DCO的时钟周期,使本地估算信号的相位输入信号相位靠拢。

4.奈奎斯特速率采样型数字锁相环路在这种数字锁相环路中,对输入信号的采样按照奈奎斯特速率进行。

也就是说,对输入信号进行A/D变换的采样频率必须按照奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。

A/D变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

三、系统设计本设计是基于直接数字频率合成器(Direct Digital Synthesizer)原理的信号发生器,用硬件描述语言Verilog来编程,用Altera公司的开发平台QUARTUSⅡ6.0来仿真,最后下载到StratixⅡ系列的EP2S60器件中进行验证。

一种新型带宽自适应全数字锁相环的设计方案

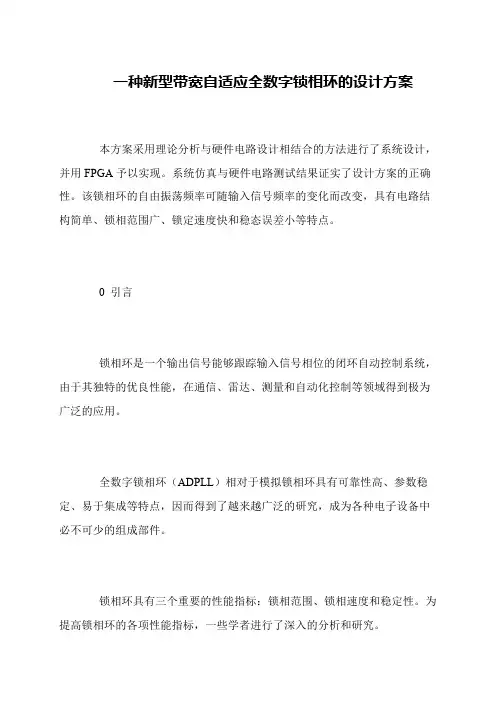

本方案采用理论分析与硬件电路设计相结合的方法进行了系统设计,并用FPGA予以实现。

系统仿真与硬件电路测试结果证实了设计方案的正确性。

该锁相环的自由振荡频率可随输入信号频率的变化而改变,具有电路结构简单、锁相范围广、锁定速度快和稳态误差小等特点。

0 引言

锁相环是一个输出信号能够跟踪输入信号相位的闭环自动控制系统,由于其独特的优良性能,在通信、雷达、测量和自动化控制等领域得到极为广泛的应用。

全数字锁相环(ADPLL)相对于模拟锁相环具有可靠性高、参数稳定、易于集成等特点,因而得到了越来越广泛的研究,成为各种电子设备中必不可少的组成部件。

锁相环具有三个重要的性能指标:锁相范围、锁相速度和稳定性。

为提高锁相环的各项性能指标,一些学者进行了深入的分析和研究。

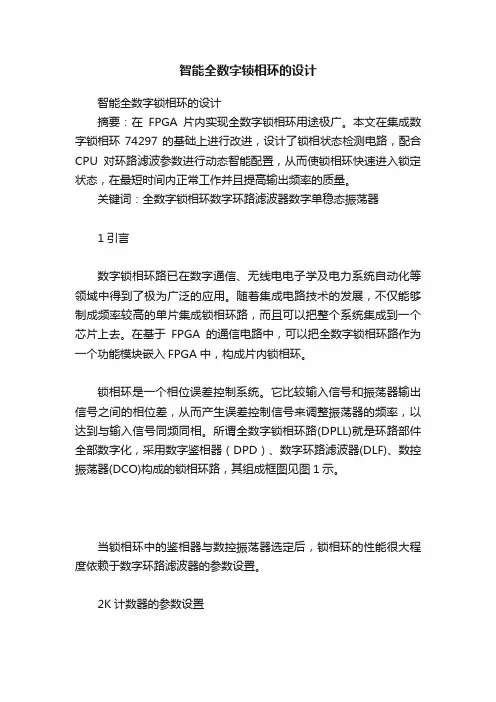

智能全数字锁相环的设计智能全数字锁相环的设计摘要:在FPGA片内实现全数字锁相环用途极广。

本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配置,从而使锁相环快速进入锁定状态,在最短时间内正常工作并且提高输出频率的质量。

关键词:全数字锁相环数字环路滤波器数字单稳态振荡器1引言数字锁相环路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。

随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。

在基于FPGA的通信电路中,可以把全数字锁相环路作为一个功能模块嵌入FPGA中,构成片内锁相环。

锁相环是一个相位误差控制系统。

它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。

所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,其组成框图见图1示。

当锁相环中的鉴相器与数控振荡器选定后,锁相环的性能很大程度依赖于数字环路滤波器的参数设置。

2K计数器的参数设置74297中的`环路滤波器采用了K计数器。

其功能就是对相位误差序列计数即滤波,并输出相应的进位脉冲或是借位脉冲,来调整I/D数控振荡器输出信号的相位(或频率),从而实现相位控制和锁定。

K计数器中K值的选取需要由四根控制线来进行控制,模值是2的N次幂。

在锁相环路同步的状态下,鉴相器既没有超前脉冲也没有滞后脉冲输出,所以K计数器通常是没有输出的;这就大大减少了由噪声引起的对锁相环路的误控作用。

也就是说,K计数器作为滤波器,有效地滤除了噪声对环路的干扰作用。

显然,设计中适当选取K值是很重要的。

K值取得大,对抑止噪声有利(因为K值大,计数器对少量的噪声干扰不可能计满,所以不会有进位或借位脉冲输出),但这样捕捉带变小,而且加大了环路进入锁定状态的时间。

一种新型PID控制的全数字锁相环的设计与实现锁相环是一种能够跟踪输入信号相位的闭环自动控制系统,广泛应用于信号处理、时钟同步、倍频、频率综合等领域。

它根据输入信号和反馈信号的相位差来调整压控振荡器的输出频率,最终达到输入信号频率和输出信号频率相等,输入信号和输出信号保持恒定的相位差。

传统的PI控制器可以消除稳态误差,保证锁定精度,但是对阻尼有不利影响。

在PI控制器中引入微分项可以改善响应速度和阻尼,保证了锁定时间,但不能减少稳态误差,因此本文提出积分分离PID控制,能够大大改善响应时间和阻尼并减少稳态误差,从而保证了锁相精度和锁相时间。

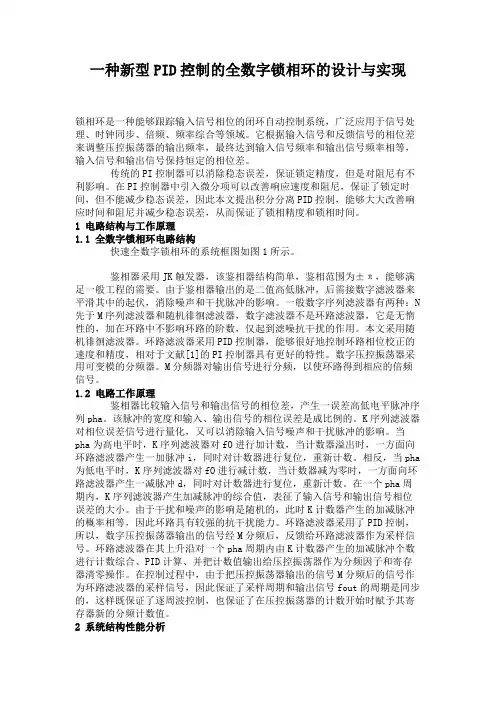

1 电路结构与工作原理1.1 全数字锁相环电路结构快速全数字锁相环的系统框图如图1所示。

鉴相器采用JK触发器,该鉴相器结构简单,鉴相范围为±π,能够满足一般工程的需要。

由于鉴相器输出的是二值高低脉冲,后需接数字滤波器来平滑其中的起伏,消除噪声和干扰脉冲的影响。

一般数字序列滤波器有两种:N 先于M序列滤波器和随机徘徊滤波器,数字滤波器不是环路滤波器,它是无惰性的,加在环路中不影响环路的阶数,仅起到滤噪抗干扰的作用。

本文采用随机徘徊滤波器。

环路滤波器采用PID控制器,能够很好地控制环路相位校正的速度和精度,相对于文献[1]的PI控制器具有更好的特性。

数字压控振荡器采用可变模的分频器。

M分频器对输出信号进行分频,以使环路得到相应的倍频信号。

1.2 电路工作原理鉴相器比较输入信号和输出信号的相位差,产生一误差高低电平脉冲序列pha。

该脉冲的宽度和输入、输出信号的相位误差是成比例的。

K序列滤波器对相位误差信号进行量化,又可以消除输入信号噪声和干扰脉冲的影响。

当pha为高电平时,K序列滤波器对fO进行加计数,当计数器溢出时,一方面向环路滤波器产生一加脉冲i,同时对计数器进行复位,重新计数。

相反,当pha 为低电平时,K序列滤波器对fO进行减计数,当计数器减为零时,一方面向环路滤波器产生一减脉冲d,同时对计数器进行复位,重新计数。

开题报告专业:电子信息工程全数字锁相环的VHDL设计一、综述本课题国内外研究动态,说明选题的依据和意义锁相技术是一种实现相位自动控制的方法,是专门研究相位的技术。

利用锁相技术得到的锁相环PLL是一个闭环的相位自动控制系统,它的输出信号能够自动跟踪输入信号的相位变化,也可以将之称为一个相位自动跟踪系统,它能够自动跟踪两个信号的相位差,并且靠反馈控制达到自动调节输出信号相位的目的。

锁相环的研究一直是学术界的一个研究重点,由于条件所限,国内对于锁相环的研究主要停留在理论方面,高性能锁相环的产品基本基本依赖进口。

而在国外,锁相环技术则在不断发展,从最初采用分离器件到采用集成电路,从采用双极工艺到使用CMOS 工艺,从需要挂电阻和电容到锁相环完全集成在一块芯片上,并且作为嵌入式IP核应用在大的数字系统中。

随着ASIC芯片电源电压下降,使得电源电压与核心薄氧化器件的阈值电压相比裕量有限从而使模拟电路设计,尤其是低噪声低电压锁相环的设计变得非常困难。

因而,当前锁相环的设计关键集中在高速、低电压、低噪声方面。

目前国外的锁相环产品大多采用3.3V电源电压的CMOS工艺,工作频率可从100MHz一直达到2.4GHz,输出噪声(周期到周期)在几十皮秒左右。

VHDL语言的英文全写是:VHSIC(Very High Speed Integrated Circuit)Hardware Description Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

其是一种行为描述语言, 其编程结构类似于计算机中的C 语言, 在描述复杂逻辑设计时, 非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

基于VHDL 语言的数字锁相环设计,不仅简化了硬件的开发和制作过程,而且使硬件体积大大减小,并提高了系统的可靠性。

该方法可以在不修改硬件电路的基础上,通过修改设计软件、更改移相范围就可满足不同用户的需要。

一种新型的全数字锁相环[ 来源:机电论文 | 类别:技术 | 时间:2006-3-11 16:33:27 ][字体:大 中 小]原作者:庞 浩,俎云霄,王赞基 原作者出处:(清华大学电机工程与应用电子技术系,北京,100084) 出处【论文摘要】该文提出了一种实现全数字锁相环的新方法。

在基于该方法实现的全数字锁相环中,一种 论文摘要 论文摘 数字比例积分控制的设计结构取代了传统的一些数字环路滤波控制方法。

通过线性近似,该文推导出该 锁相环系统的数学模型,并进一步对该系统的局部动态特性进行了讨论。

理论分析表明这种新型的全数 字锁相环具有很宽的锁相范围,并且在不同被锁频点的局部范围内都具有相同的稳定形式,锁相跟踪达 到稳定的时间与被锁信号的周期成正比。

由于充分利用了鉴相脉冲宽度所包含的相位误差信息,同时又 引入了积分控制,使锁相环的跟踪响应速度得到提高。

仿真实验进一步验证了理论分析的结论。

该文锁 相环采用数字电路方式实现,其性能可以通过比例和积分控制参数进行调节,因而简化了设计过程,便 于应用在电机调速系统、有源滤波器和静止无功补偿器等领域。

1 引言 信号锁相技术广泛应用于自动化控制等领域。

利用该技术可以产生同步于被锁输入信号的整数倍频或 者分数倍频的输出控制信号。

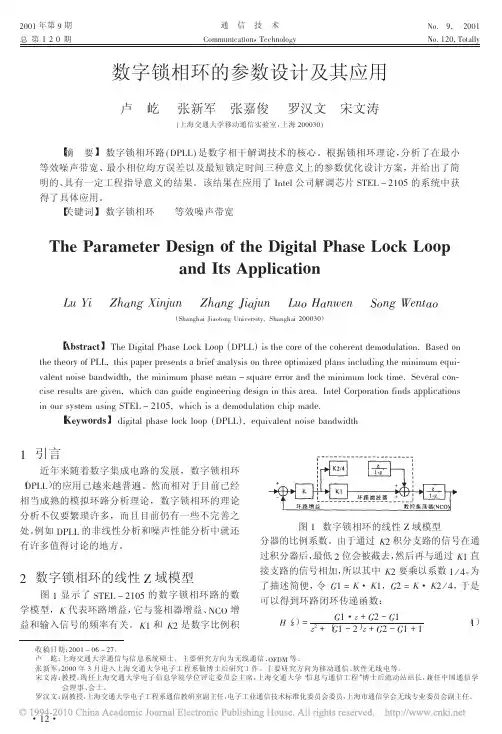

锁相环的基本结构是由鉴相、环路滤波、可控振荡器和 M 倍分频等模块组 成的一个反馈环路,如图 1 所示。

输入的被锁信号首先与同步倍频信号经过 M 倍分频后产生的锁相信号 进行鉴相处理,输出相位误差信号。

环路滤波模块通常具有低通特性,它将相位误差信号转化为稳定的 控制信号,从而控制可控振荡器模块,产生稳定的频率信号输出。

这个频率信号就是所需的同步倍频信 号。

如果整个反馈环路锁相稳定, 锁相环输出的同步倍频信号的频率就是其输入的被锁信号频率的 M 倍。

假如被锁信号在输入鉴相模块之前又先被分频了 L 倍,则锁相获得的同步倍频信号的频率就是被锁信号频率的 M/L 倍。

全数字锁相环的设计及分析1 引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

2全数字锁相环的体系结构和工作原理74XX297 是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1 鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

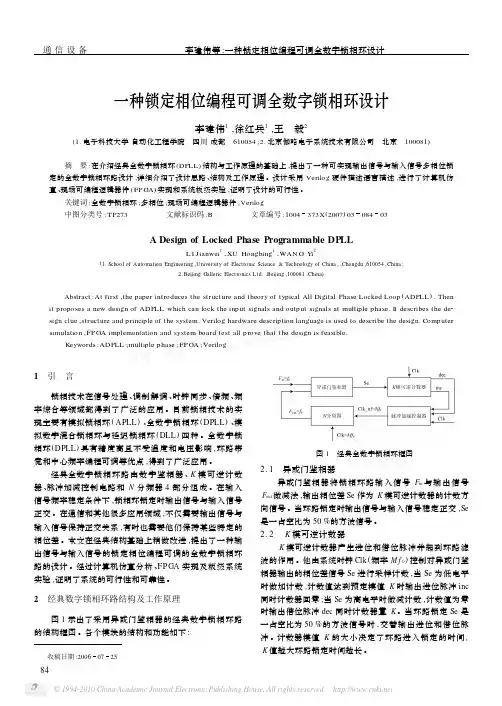

一种锁定相位编程可调全数字锁相环设计李建伟1,徐红兵1,王 毅2(1.电子科技大学自动化工程学院 四川成都 610054;2.北京伽略电子系统技术有限公司 北京 100081)摘 要:在介绍经典全数字锁相环(DPLL )结构与工作原理的基础上,提出了一种可实现输出信号与输入信号多相位锁定的全数字锁相环路设计,详细介绍了设计思路、结构及工作原理。

设计采用Verilog 硬件描述语言描述,进行了计算机仿真、现场可编程逻辑器件(FP GA )实现和系统板级实验,证明了设计的可行性。

关键词:全数字锁相环;多相位;现场可编程逻辑器件;Verilog中图分类号:TP273 文献标识码:B 文章编号:1004373X (2007)0308403A Design of Locked Phase Programmable DPLLL I Jianwei 1,XU Hongbing 1,WAN G Y i 2(1.School of Automation Engineering ,University of Electronic Science &Technology of China ,,Chengdu ,610054,China ;2.Beijing G alleric Electronics L td.,Beijing ,100081,China )Abstract :At first ,the paper introduces the structure and theory of typical All Digital Phase Locked Loop (ADPLL ).Then it proposes a new design of ADPLL which can lock the input signals and output signals at multiple phase.It describes the de 2sign clue ,structure and principle of the system.Verilog hardware description language is used to describe the puter simulation ,FP GA implementation and system board test all prove that the design is feasible.K eywords :ADPLL ;multiple phase ;FP GA ;Verilog收稿日期:200607251 引 言锁相技术在信号处理、调制解调、时钟同步、倍频、频率综合等领域都得到了广泛的应用。

采用VHDL设计的全数字锁相环电路设计叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。

0 引言全数字锁相环(DPLL) 由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点。

从而具备可靠性高、工作稳定、调节方便等优点。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA) 技术的发展,采用大规模可编程逻辑器件(如CPLD 或FPGA) 和VHDL 语言来设计专用芯片ASIC 和数字系统,而且可以把整个系统集成到一个芯片中,实现系统SOC ,构成片内锁相环。

下面介绍采用VHDL技术设计DPLL 的一种方案。

1 DPLL 的基本结构全数字锁相环结构框图如图1 所示, 由数字鉴相器、数字环路滤波器和数控振荡器3 部分组成。

'0') ;end if ;elseif cq > 0 then cq '0') ;end if ;end if ;end process ;process (en ,j ,cq ,k)beginif en = '1'thenif j = '0'thenf cq = k then cao1图4 变模可逆计数器(取k = 24) 的仿真波形图2. 3 数控振荡器的设计数控振荡器由加/ 减脉冲控制器和除N 计数器组成的。

加/ 减脉冲控制器其实是一个增量—减量计数器式DCO。

它和环路滤波器连用。

如果在环路滤波器无进位、错位的时候,加/ 减脉冲控制器对时钟2NFo 进行二分频。

当加/ 减脉冲控制的增量输入端( I = 1) 输入一个进位脉冲时, 输出脉冲中通过该计数器内部加上一个时钟脉冲。

反之,当加/ 减脉冲控制的减量输入端( D = 1) 时输入一个借位脉冲输出脉冲中就减去一个时钟脉冲。

开题报告专业:电子信息工程全数字锁相环的VHDL设计一、综述本课题国内外研究动态,说明选题的依据和意义锁相技术是一种实现相位自动控制的方法,是专门研究相位的技术。

利用锁相技术得到的锁相环PLL是一个闭环的相位自动控制系统,它的输出信号能够自动跟踪输入信号的相位变化,也可以将之称为一个相位自动跟踪系统,它能够自动跟踪两个信号的相位差,并且靠反馈控制达到自动调节输出信号相位的目的。

锁相环的研究一直是学术界的一个研究重点,由于条件所限,国内对于锁相环的研究主要停留在理论方面,高性能锁相环的产品基本基本依赖进口。

而在国外,锁相环技术则在不断发展,从最初采用分离器件到采用集成电路,从采用双极工艺到使用CMOS工艺,从需要挂电阻和电容到锁相环完全集成在一块芯片上,并且作为嵌入式IP 核应用在大的数字系统中。

随着ASIC芯片电源电压下降,使得电源电压与核心薄氧化器件的阈值电压相比裕量有限从而使模拟电路设计,尤其是低噪声低电压锁相环的设计变得非常困难。

因而,当前锁相环的设计关键集中在高速、低电压、低噪声方面。

目前国外的锁相环产品大多采用3.3V电源电压的CMOS工艺,工作频率可从100MHz一直达到2.4GHz,输出噪声(周期到周期)在几十皮秒左右。

VHDL语言的英文全写是:VHSIC(Very High Speed Integrated Circuit)Hardware Description Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

其是一种行为描述语言, 其编程结构类似于计算机中的C 语言, 在描述复杂逻辑设计时, 非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

基于VHDL 语言的数字锁相环设计,不仅简化了硬件的开发和制作过程,而且使硬件体积大大减小,并提高了系统的可靠性。

该方法可以在不修改硬件电路的基础上,通过修改设计软件、更改移相范围就可满足不同用户的需要。

Vol. 15 No. 4 系统仿真学报April 2003 JOURNAL OF SYSTEM SIMULATION• 581 • 一种新型快速全数字锁相环的研究单长虹, 邓国扬(南华大学电气工程学院, 湖南衡阳421001)摘 要: 提出了一种具有自动变模控制的快速全数字锁相环。

该系统利用鉴相器的输出信号进行快捕区、慢捕区和锁定区的切换,并通过对数字环路滤波器的模数进行自动调节,来实现对环路带宽的实时控制。

它能够有效地克服环路捕捉时间与抗噪声性能的矛盾。

具有同步建立时间短、抗干扰能力强、静态相差小和易于集成等特点。

该文介绍了该锁相环的原理和实现,并对其性能进行了分析和计算机仿真。

关键词:全数字锁相环;VHDL;仿真;片上系统文章编号:1004-731X (2003) 04-0581-03 中图分类号:TN914.3 文献标识码:A Research on a New Type of Fast All Digital Phase-Locked LoopSHAN Chang-hong, DENG Guo-yang(College of Electronic Engineering, Nanhua University, Hunan 421001, China)Abstract: A fast all digital phase-locked loop with automatic modulus control is presented. It switches fast pull-in area, slow pull-in area and locking area by using the out signal of phase detector and controls the loop bandwidth by controlling the modulus of digital loop filter automatically. The system can overcome efficiently contradiction between pull-in time and anti-interference property. Its merits are that synchronization setting-up time is short, anti-interference ability is strong, static phase error is small and integration is easy. The work principle and implementation of DPLL is introduced. Its performances are analyzed and verified by simulation.Keywords: all digital phase-locked loop; VHDL; simulation; SOC引言全数字锁相环与模拟锁相环相比具有性能稳定、工作可靠和易于集成等优点,因而在数字通信和自动控制等领域得到了广泛的应用。

0引言锁相环是一个能对输入信号进行自动跟踪的负反馈控制电路。

锁相环在通信、无线电电子学、自动控制和电力系统自动化等领域得到了极为广泛的应用,其性能的好坏将直接影响整个电子系统的工作性能[1]。

随着数字技术的不断发展,全数字锁相环的应用范围也更加广泛[2]。

全数字锁相环具有比模拟锁相环更多的优点,它可以解决模拟锁相环中设计复杂性较高、可移植性较差和对噪声十分敏感等问题[3]。

对于系统芯片而言,系统运行速度和功耗是衡量其性能优劣的重要指标之一,如何提高其运行速度和降低其功耗是国内外学者关注的热点问题[4]。

全数字锁相环作为系统芯片中常用的功能模块,这些问题也是我们在设计锁相环时迫切需要解决的问题。

另一方面,提高锁相环的锁相速度与增强锁相环的稳定性是相互矛盾的。

在锁相环设计时,若数字滤波器的参数取较小值,可加快锁相环的锁相速度,缩短锁相时间,但在系统锁定后会出现相位抖动,影响系统的稳定性;而其参数取较大值时,虽可减小相位抖动,增强系统的稳定性,但却又会造成锁相速度变慢。

由于传统全数字锁相环中数字滤波器的参数是固定不变的,不能实现参数的动态调节,因此,在锁相环设计时只能取某一固定的折中值,这就不能从根本上解决同时提高锁相环的动态性能与稳态性能之间所存在的矛盾,也就不能最大限度地提高锁相系统的整体性能。

本文提出的基于流水线技术的全数字锁相环,一是能够提高锁相系统的运行速度,降低系统功耗;二是可实现数字滤波器参数的动态调节,从根本上解决提高锁基于流水线技术的全数字锁相环设计*田帆,杨檬玮,单长虹(南华大学电气工程学院,湖南衡阳421001)摘要:为了提高全数字锁相环的系统运行速度、降低系统功耗,同时提高锁相系统的动态性能与稳态性能,提出一种基于流水线技术的全数字锁相环。

采用电子设计自动化技术完成了该系统的设计,并对所设计的电路进行了计算机仿真与分析。

仿真结果证明,该锁相环中数字滤波器的参数能够根据相位误差的大小进行动态调节,既可加快锁相速度,又能增强系统的稳定性。

新型全数字锁相环的逻辑电路设计

徐健飞;庞浩;王赞基;陈建业

【期刊名称】《电网技术》

【年(卷),期】2006(30)13

【摘要】设计出一种新型全数字锁相环(enhancedphase-lockloop,EPLL)的逻辑

电路。

该电路基于轨迹跟踪原理实现与交流基波成分的同步,其锁相速度快,精度高。

同时,为兼顾锁相速度和稳定性的设计要求,提出调节EPLL动态参数的新方法,获得

具有优化结构的全数字锁相逻辑电路。

锁相跟踪实验验证了该锁相环技术的性能,

证实了其在提取和分析谐波方面的有效性。

【总页数】4页(P81-84)

【关键词】全数字锁相环;动态参数调节;同步;数字逻辑电路

【作者】徐健飞;庞浩;王赞基;陈建业

【作者单位】清华大学电机工程与应用电子技术系

【正文语种】中文

【中图分类】TM715

【相关文献】

1.基于FPGA的超声波电源数字锁相环电路设计 [J], 车保川

2.一种新型的用于高速串行接口电路的单片锁相环电路设计 [J], 孙振国;何乐年;温显光;严晓浪

3.基于 CD4046锁相环的数字频率合成器电路设计 [J], 刘艳红

4.数字电路设计好帮手嵌入式系统开发利器——LA系列逻辑分析仪=逻辑分析仪+总线分析仪+协议分析仪+频率计+逻辑笔 [J],

5.一种改进的用于FPGA的快速数字锁相环电路设计 [J], 谭聪;卜海祥;唐璞山因版权原因,仅展示原文概要,查看原文内容请购买。