时序逻辑电路分析举例

- 格式:docx

- 大小:127.19 KB

- 文档页数:7

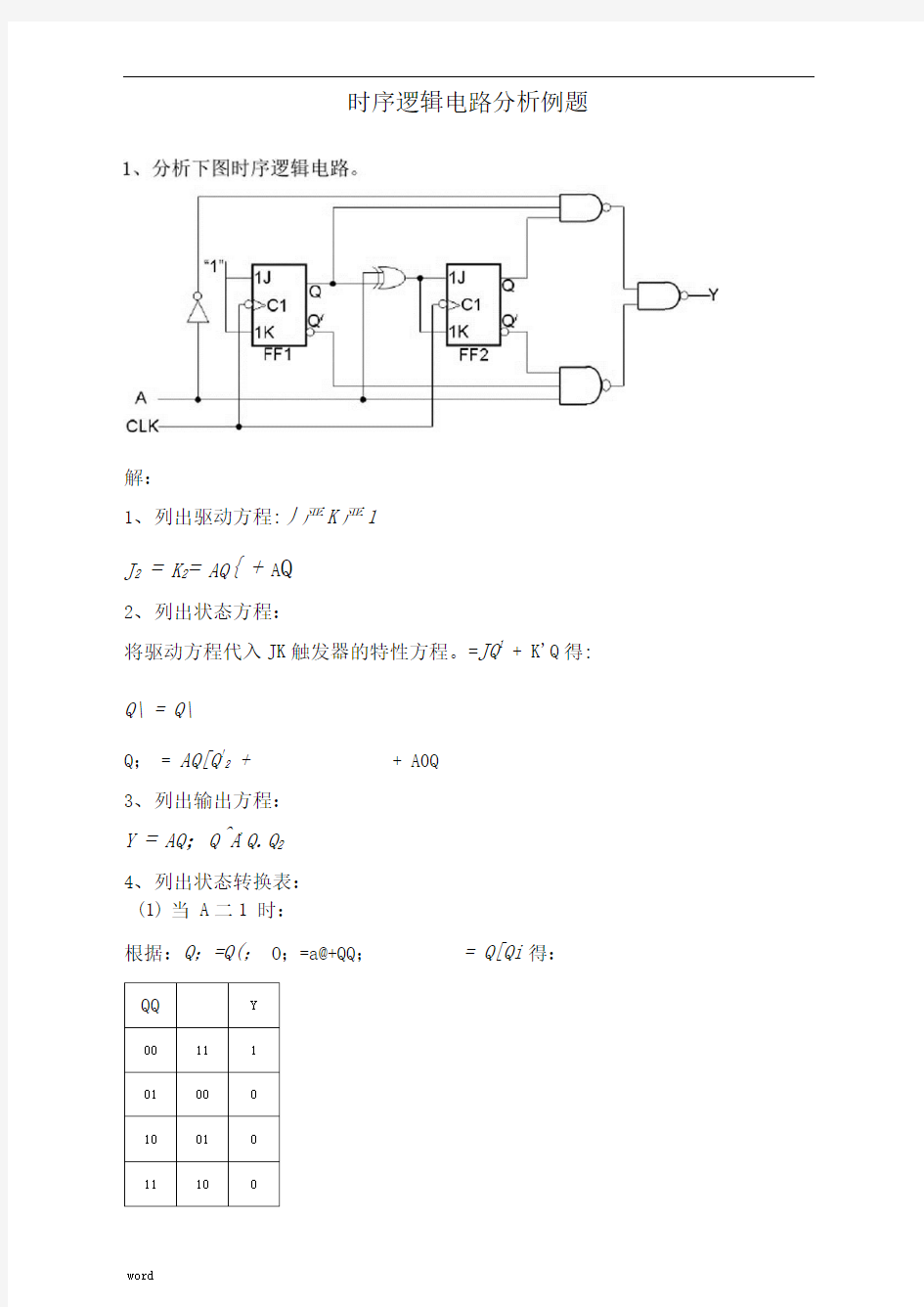

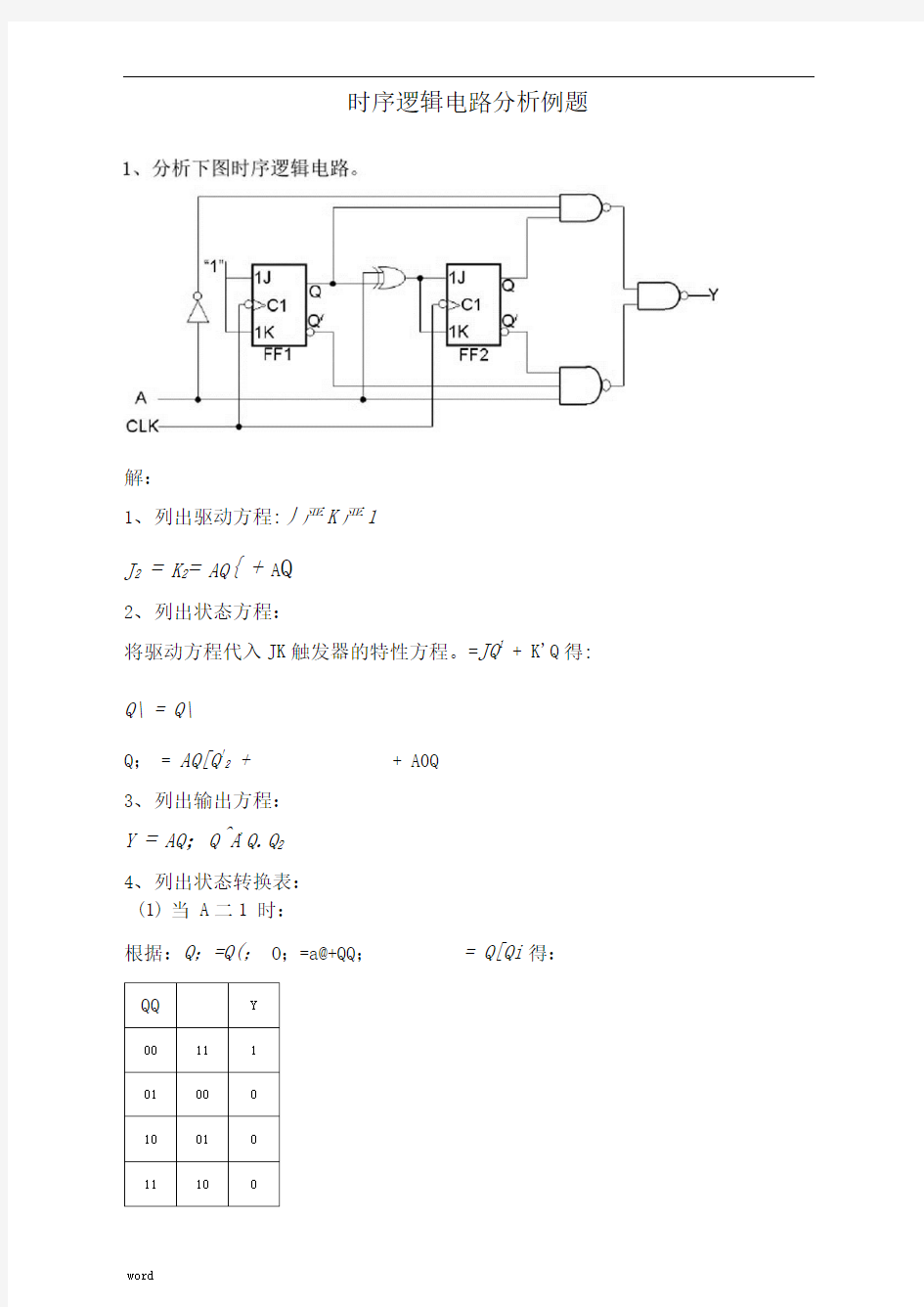

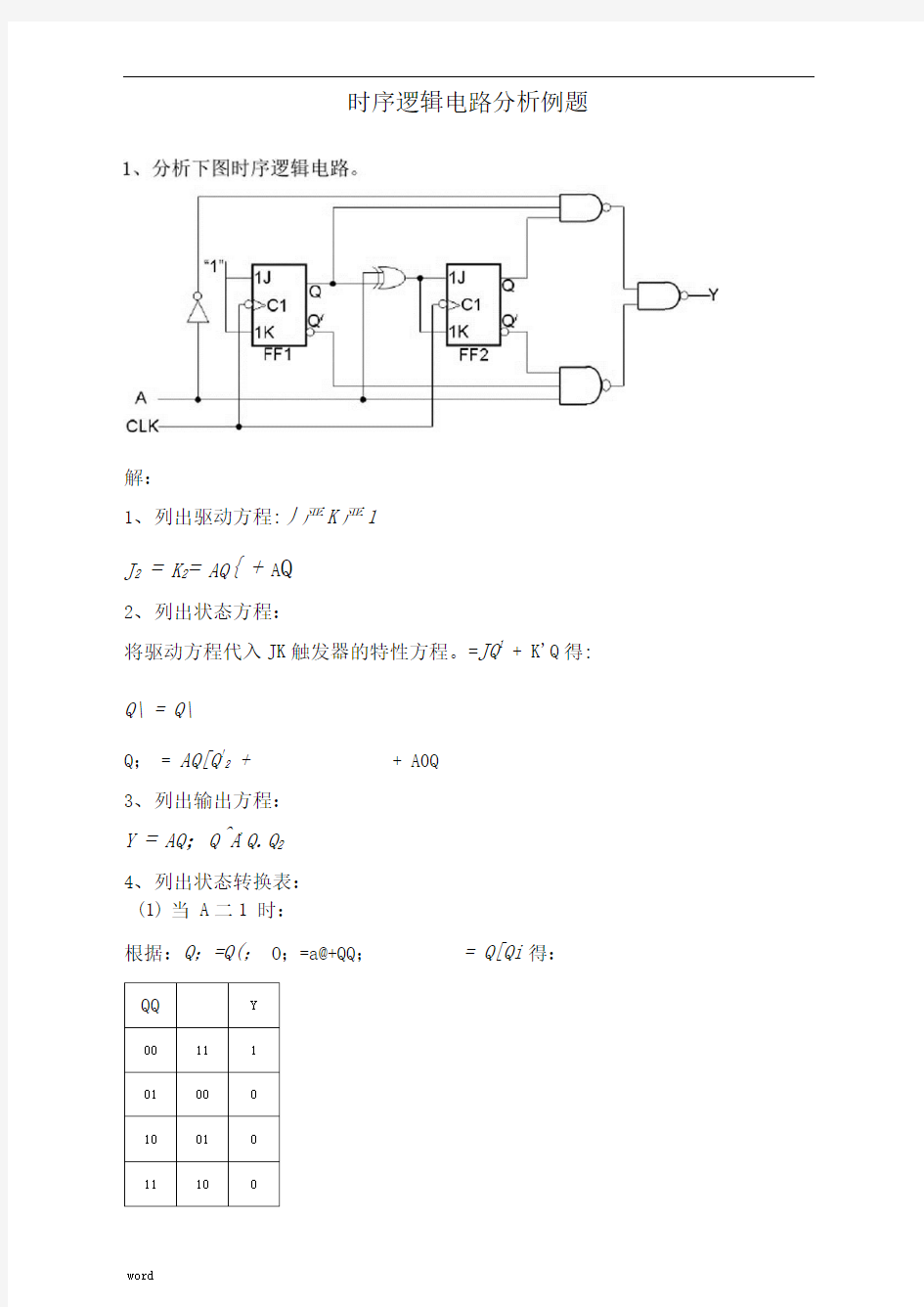

时序逻辑电路分析例题

解:

1、列出驱动方程:丿严K严1

J2= K2= AQ{+A Q

2、列出状态方程:

将驱动方程代入JK触发器的特性方程。=JQ1 + K'Q得: Q\ = Q\

Q; = AQ[Q!2 + + A0Q

3、列出输出方程:

Y = AQ;Q^A,Q.Q2

4、列出状态转换表:

(1)当A二1 时:

根据:Q;=Q(; O;=a@+QQ;= Q[Qi得:

(2)当A二0 时:

根据:e;=Q[;

6、说明电路实现的逻辑功能:

此电路是一个可逆4进制(二位二进制)计数器,CLK是计数脉冲输入端,A 是加减控制端,Y是进位和借位输出端。当控制输入端A为低电平0时,对输入的脉冲进行加法计数,计满4个脉冲,Y输出端输出一个高电平进位信号。当控制输入端A为高电平1时,对输入的脉冲进行减法计数,计满4个脉冲,Y输岀端输出一个高电平借位信号。

2、如图所示时序逻辑电路,试写出驱动方程、状态方程,画出状态图,说明该电路的功能。

解:驱动方程

J.=X®Q^{J,=X ㊉Q;;

A=I k=i

状态方程

er* =(X ㊉0 広"=XQ;'Q'^ + XQ;l Q;;

Q;r =(X ㊉Q;'= XQ;'Q;; + XQ;Q;;

输出方程

Z = (x㊉0也

1、状态转换表,如表所示。状态转换图,略。

2、这是一个3进制加减讣数器,当X二0时为加计数器,计满后通过Z

向高位进位;X二1时为减计数器,计满后通过Z向高位借位;能

自启动。

例3

0),要求

(1)画出状态转换图。

(2)画出时序图。

(3)说明是多少进制计数器。

答:(1)

(2)时序图

4、分析下图所示时序逻辑电路,写出电路的驱动方程、状态方程和输出方程, 画岀电路的状态转换图,说明电路实现的的逻辑功能。A为输入变量。

解:

(1)列写方程驱动方程:触发器的驱动方程为:

D、= Q[ D2 = A㊉© ㊉Q2

(2)列写方程驱动方程:

触发器的特性方程为:Q"=D

将驱动方程代入特性方程可得状态方程为:

CLK-

CP

Q = D = Q{

Q; = 2 = A ㊉© ㊉Q

(3)列写输出方程:Y = A(Q i Q2+AQ;Q,2

(4)列出状态转换表:

当A二1时:

根据:Q; =Q;; 0;= 00+00;Y = Q\Q1得:

当A=0时:

根据:Q: = Q;;Y = 得:

(5)画状态转换图:

(6)说明电路实现的逻辑功能:(2分)

此电路是一个可逆4进制计数器,CLK是计数脉冲输入端,A是加减控制端,Y 是进位和借位输出端。当控制输入端A为低电平0时,对输入的脉冲进行加法计数,计满4个脉冲,Y输出端输出一个高电平进位信号。当控制输入端A为高电平1时,对输入的脉冲进行减法计数,计满4个脉冲,Y输出端输岀一个高电平借位信号。