基于FPGA的CameraLink视频转SDI视频的转换器的设计

- 格式:docx

- 大小:46.17 KB

- 文档页数:6

基于FPGA的Camera Link视频信号分配系统设计

韩红霞;钟子晶

【期刊名称】《微计算机信息》

【年(卷),期】2010(026)017

【摘要】在给出标准CameraLink视频信号协议的基础上,设计基于FPGA的视频分配系统.实现视频信号一分三.扩展Camer-aLink信号接口,提供给后续图像处理、存储等设备.实验表明视频分配系统可以正确的将CameraLink视频信号进行一比

三分配,系统工作稳定,信号传输质量良好.

【总页数】3页(P8-9,80)

【作者】韩红霞;钟子晶

【作者单位】130033,中科院长春光学精密机械与物理研究所;130000,空军航空大学

【正文语种】中文

【中图分类】TP711

【相关文献】

1.基于FPGA的SDI到Camera Link视频接口转换系统设计 [J], 朱超;刘艳滢;董

月芳

2.基于Camera Link标准的DSP+FPGA高速实时数字图像处理系统设计 [J], 陈

炎斌;金钢

3.基于Cameralink标准的DSP+FPGA数字图像处理系统设计 [J], 黄志超

4.基于Cameralink标准的DSP+FPGA数字图像处理系统设计 [J], 黄志超

5.基于FPGA的Camera Link视频信号转换与控制系统设计 [J], 徐大鹏

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的高清视频实时处理系统设计摘要:随着高清视频技术领域的日新月异,对实时视频处理系统的性能需求愈发严苛,特别是在处理速度与效率方面提出了更高标准。

现场可编程门阵列(FPGA),作为一款具备强大并行处理能力的硬件平台,凭借其出色的性能表现,已在全球范围内被广泛应用到各类高清视频实时处理系统之中。

在此背景下,我们创新性地提出一种以FPGA为核心的高清视频实时处理系统设计方案。

关键词:FPGA;高清视频;实时处理;系统设计引言高清视频技术的广泛应用推动了视频处理技术的快速发展。

实时视频处理系统要求处理速度快、处理效率高,并且需要支持高清视频的处理。

传统的基于CPU或GPU的视频处理系统难以满足这些要求,因此,基于FPGA的高清视频实时处理系统成为了研究的热点。

FPGA作为一种可编程的硬件,具有高度的并行性和灵活性,非常适合用于视频处理。

通过优化算法和硬件架构,可以实现高速、高效的视频处理。

本文提出了一种基于FPGA的高清视频实时处理系统设计方法,旨在满足高清视频实时处理的需求。

1.系统设计1.1系统架构本系统以FPGA为核心运算单元,高效对接并快速处理高清视频数据,其数据输入端通过高速接口无缝接纳视频流。

系统整体架构划分为三个关键模块:视频输入模块、处理模块以及视频输出模块。

首先,视频输入模块肩负起视频数据的接纳重任,精准捕获每一帧高清影像,并确保其无损、实时地传送至后续的处理环节。

其次,处理模块作为系统的中枢大脑,集中执行一系列复杂的视频处理任务。

这包括但不限于图像质量的精细化提升(如增强)、噪声的有效抑制(如去噪)以及数据量的合理压缩,以满足不同应用场景对视频内容的多样需求。

最后,视频输出模块扮演着桥梁角色,将经深度加工的视频数据精准推送至显示终端,确保用户能够获得清晰流畅的视觉体验。

1.2算法优化为实现高速、高效的视频处理,系统设计中对算法进行了针对性优化:①精选与FPGA特性匹配的算法(如滤波器图像增强、压缩编码视频压缩),以利用其并行计算优势;②对算法深度并行化,精细划分任务,优化调度,实现多步骤同步执行,大幅提升执行速度;③精简与优化算法,通过计算复用、数据预取、冗余消除等手段减少计算量与存储需求,有效提高整体处理速度。

基于FPGA的视频转换系统设计任勇峰;王大伟;石永亮;于丽娜【摘要】为解决不同视频系统之间显示时序、色彩空间、帧频、分辨率等不一致的问题,设计了一种以FPGA为控制核心, DDR2 SDRAM为高速缓存的视频转换系统,该系统从图形工作站采集到DVI视频,先进入高速缓存模块,然后通过视频转换算法在FPGA内部完成RGB至YCbCr的色彩空间转换,最后控制硬件实现PAL视频输出,实现了由DVI视频向PAL视频的转换。

经长期测试证明:该系统稳定可靠,达到设计要求。

%In order to solve the display between different video systems in consistencies timing,color space,framerate,resolution,etc,a video conversion system was designed,which regards FPGA as the control core,DDR2 SDRAM for cache. the device system collected DVI video from workstation graphics,firstly enters the cache mod⁃ule,and then completes the color space conversion and frame rate conversion via video conversion algorithm within the FPGA,and finally controls hardware PAL video output,completed by the DVI video conversion to PAL video. The long-term test proves:the system is stable and reliable,and meet the design requirements.【期刊名称】《电子器件》【年(卷),期】2016(039)003【总页数】7页(P655-661)【关键词】视频转换;DVI;PAL;高速缓存;转换算法【作者】任勇峰;王大伟;石永亮;于丽娜【作者单位】中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学电子测试技术重点实验室,太原030051【正文语种】中文【中图分类】TP274.2随着多媒体信息技术的高速发展,视频技术多元化发展成为趋势,而同时也激化了视频系统之间互联的矛盾。

CameraLink协议和FPGA的数字图像信号源设计关键字: FPGA Camera Link 标准 CMOS1 引言目前,各种图像设备已广泛应用到航空航天、军事、医疗等领域。

图像信号源作为地面图像采集装置测试系统中的一部分,其传输方式及信号精度都是影响系统性能的重要因素。

由于图像信号的传输速率高,数据量大,在传输过程中,其精度和传输距离易受影响。

为了提高信号传输距离和精度设计了由FPGA内部发出图像数据,并通过FPGA进行整体时序控制;输出接口信号转换成符合Camera Link标准的低电压差分信号(LVDS)进行传输。

该图像信号源已成功应用于某弹载记录器的地面测试台系统中。

2 Camera Link接口及图像数据接口信号Camera Link标准是由国家半导体实验室(National Semiconductor)提出的一种Channel Link技术标准发展而来的,该接口具有开放式的接口协议,使得不同厂家既能保持产品的差异性,又能互相兼容。

它在传统LVDS传输数据的基础上又加载了并转串发送器和串转并接收器,可在并行组合的单向链路、串行链路和点对点链路上,利用SER,DES(串行化,解串行化)技术以高达4.8 Gb,s的速度发送数据。

CameraLink标准使用每条链路需两根导线的LVDS传输技术。

驱动器接收28个单端数据信号和1个时钟信号,这些信号以7:1的比例被串行发送,也就是5对LVDS信号通道上分别传输4组LVDS数据流和1组LVDS时钟信号,即完成28位数据的同步传输只需5对线,而且在多通道66 MHz像素时钟频率下传输距离可达6 m。

Camera Link是在Channel Link的基础上增加了一些相机控制信号和串行通信信号,定义出标准的接头也就是标准化信号线,让Camera及影像卡的信号传输更简单化,同时提供基本架构(Base Configuration)、中阶架构(Medium Configuration)及完整架构(Full Configuration)三种:基本架构属单一Camera Link元件,为单一接头;中阶架构属双组Camera Link元件,为双组接头;完整架构属三组Camera Link元件,为三组接头。

基于FPGA的视频格式转换系统设计

张国庆;刘一清;程文华

【期刊名称】《中国有线电视》

【年(卷),期】2011(000)001

【摘要】针对电视制式PAL/NTSC信号输出VGA显示格式的解决办法,详细讲述了基于FPGA视频格式转换系统的设计实现.采用CycloneⅢ系列的

EP3C16F484C6作为核心处理器件,实现了NTSC/PAL制式视频的解码、色空间

转换(CSC)、帧速率转换和隔行逐行转换、缩放、视频DAC转换,最终实现分量R、G、B的VGA视频格式的视频输出,分辨率可达1600×1200@100Hz.

【总页数】5页(P31-35)

【作者】张国庆;刘一清;程文华

【作者单位】华东师范大学信息学院,上海,200241;华东师范大学信息学院,上

海,200241;华东师范大学信息学院,上海,200241

【正文语种】中文

【中图分类】TN941.1

【相关文献】

1.基于FPGA的视频格式转换电路设计 [J], 韩贵黎;李中显

2.基于FPGA的视频格式转换电路设计 [J], 韩贵黎;李中显

3.基于DSP和FPGA的视频格式转换 [J], 张廷华;樊桂花

4.基于FPGA的自适应实时视频梯形矫正系统设计与实现 [J], 索军红;张冠茂;乔鑫;

赵汉卿

5.基于Sobel算子的实时视频处理系统设计与FPGA实现 [J], 朱高锋

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的3GHDSD―SDI信号光纤传输系统的设计摘要:介绍了基于FPCJA和高速串行复接/解复接技术,将3G/HD/SD-SDI 信号通过光纤实现无损长距离传输的方法。

与传统的传输方案相比,此方案可以完成传输高清视频的平滑升级,并向下兼容现有的视频传输网络,降低了网络的改造升级成本。

关键词:3G/HD/SD-SDI;自动均衡;时钟恢复;光纤传输引言SDI(Serial Digital Interface)是一种“数字分量串行接口”,通过75Ω同轴线缆传输无压缩的数字视频信号。

由于串行数字信号的数据率很高,在传送前必须经过处理。

用扰码的不归零倒置(NRZI)来代替早期的分组编码,其标准为SMPTE 259M和EBU-Tech-3267,标准包括了含数字音频在内的数字复合和数字分量信号,支持4种速率:143Mbit/s的NTSC制复合编码信号:177.3Mbit/s的PAL制复合编码信号:270Mbit/s的NTSC制和PAL制分量编码信号:360Mbit/s 16:9长宽比的NTSC制和PAL制分量编码信号,其中最常见的是270Mbit/s。

在传送前,对原始数据流进行扰频并变换为NRZI码,确保在接收端可靠地恢复原始数据。

在概念上可以将数字串行接口理解为一种基带信号调制。

SDI接口能通过270Mbit/s的串行数字分量信号,对于16:9格式的图像,应能传送360Mbit/s 的信号。

NRZI码是极性敏感码。

用“1”和“O”表示电平的高和低,如果出现长时间的连续“1”或连续“O”,会影响接收端从数字信号中提取时钟。

因为串行数字信号接口不单独传送时钟信号,接收端需从数字信号流中提取时钟信号,所以要采用以“1”和“O”来表示有无电平变换的NRZI码。

在接收NRZI 码流时,只要检出电平变换,就可恢复数据,再经过加扰,连“1”的机会减少,也就使高频分量进一步减少,使解码和提取时钟信息更加容易。

实现加扰/解扰的生成多项式为G1(x)=X9+X4+1,该步主要是将数字化的视频信号变成NRZ 扰码信号。

FPGA的3G高清视频信号转换接口设计分析摘要:在我国现代数字电视技术迅速发展的背景下,目前高清电视节目的高质量建设以及传输已经得到了大范围的推广与应用。

显而易见的是,信息时代背景下的电视节目制作标准已经被不断完善并落实了统一规范制度,逐步得到了多家设备制造厂商的高度认可,而高清电视节目的制作市场也已经成为各大设备制造厂商所关注的行业热点内容。

从目前的发展现状来看,大部分高清电视节目的制作上都采用了SDI口来落实电视信号的摄入与传输,但由于其生产成本较高,所以很难实现大范围高清视频制作的推广。

对此,本文基于FPGA的3G高清视频信号转换接口系统的设计方案进行阐述,重点分析其系统建设的指标需求,并针对该系统的主要工作流程进行阐述,在全面提升节目质量建设的前提下,满足高清视频大范围推广的必然趋势。

关键字:FPGA;3G高清视频信号;转换接口设计前言:随着我国现代科学技术水平的迅速发展,进一步提升了我国广大人民群众的活质量,而高清设备也在多媒体技术迅速提升的背景下得到了快速推广。

从目前的发展现状来看,数字高清不仅在很大范围内改善了人们的生活方式,同时更成为未来携式电子显示设备所必备的重要特征。

需要注意的是,在数字高清发展逐步落实的大环境下,虽然高清设备的混乱使用却导致我国现代数字视频业务没有得到深入推广,但仍然清晰可见现代高清市场行业已经逐步迈向的规范化与统一化的发展历程,并逐步成为各大设备制造厂商争夺的行业热点。

基于此背景下,如何进一步提升高清电视节目制作在传输接口上的建设标准,也成为未来数字电视技术创新发展的必然趋势。

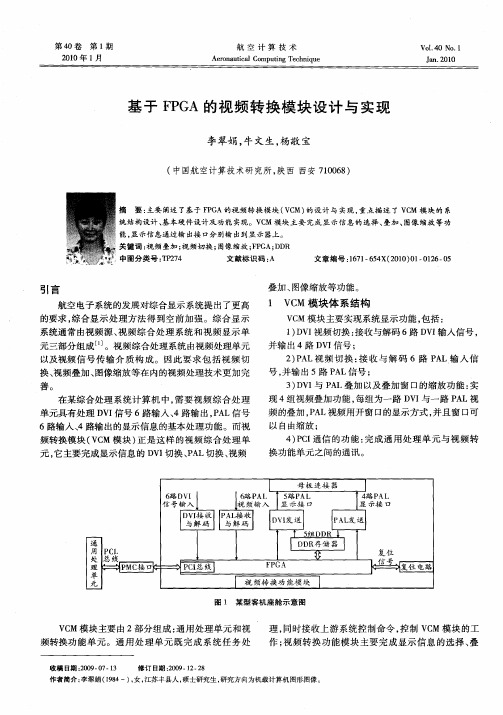

1.基于FPGA的3G高清视频信号转换接口系统设计方案如图一所示,为本文在针对基于FPGA的3G高清视频信号转换接口系统设计的总框图,可明显看出的是,本系统设计总体可分为三大模块,即输入模块、转换模块以及输出模块。

在这一系统设计流程当中,由于传统的SDI格式视频信号在电缆中的距离将会由于距离过长产生信号传输的衰减或畸变的现象,所以本系统在设计信号输入的过程当中首先就优先采用了均衡器以及始终恢复器设备来针对输入端的信号质量进行初次恢复,然后再将被恢复后的数据进行串联、转换、解忧等一系列的信号校验操作,以此生成以20 bit并行数据【1】以及一个同步像素时钟数据为主的信号状态。

基于FPGA的视频信号发生器设计

摘要:目前数字相机逐步取代模拟相机应用在光电测量设备中,因此图像处理器也逐渐转化为接收数字视频的接口,对数字图像处理器检测的信号发生器的研制也变得十分迫切。

本文介绍了一种基于FPGA的两种数字视频格式输出的视频发生器,它可以产生LVDS制式的数字视频信号和CamerLink制式的数字视频信号,而且可以通过串口对产生的视频中的目标大小、运动速度、灰度及背景灰度进行实时更改。

它满足了对数字视频输入的图像处理平台的检测,具有一定应用前景。

关键词:现场可编程门阵列;视频发生器;LVDS;图像处理平台

0 引言

在光电测量系统中,需要图像处理器进行图像采集、处理。

而为了对图像处理器的图像采集能力及处理能力进行评估、检测,常常需要对图像处理器输入特定视频,进行各项功能测试。

目前随着数字化相机的广泛应用,图像处理器多采用数字化接口。

而且对图像处理器的检测要求信号发生器产生的视频内容越来越丰富,帧频越来越高,而目前检测图像处理器的信号发生器多是标准的模拟视频输出,如文献提出的模拟视频发生器,有的虽然能产生数字视频但内容是固定的,如果对内容进行更改则需要对数字视频信号发生器重新编程以达到要求,比较麻烦,不能满足日益复杂的要求。

因此灵活改变视频内容的数字视频信号发生器的研制变得十分迫切。

本文提出一种数字视频信号发生器的设计方法,此方法可以同时得到LVDS和CamerLink制式。

收稿日期:2012-08-19作者简介:李志强(1980-),男,硕士,助理研究员,主要从事电子学硬件和软件设计方面的研究,E-mail:mybugatti@ 。

长春理工大学学报(自然科学版)Journal of Changchun University of Science and Technology (Natural Science Edition )第35卷第4期2012年12月Vol.35No.4Dec.2012Camera Link 数字视频光纤传输系统的FPGA 实现李志强,张建华(中国科学院长春光学精密机械与物理研究所;中国科学院航空光学成像与测量重点实验室,长春130033)摘要:为解决实时转动的光电平台中高速Camera Link 数字视频信号的传输问题,在光电平台设计中采用了光纤滑环替代传统的导电滑环作为传输介质,为此提出了一种基于FPGA 的Camera Link 接口转光纤信号传输的设计方案。

利用FP-GA 强大的并行处理能力,采用乒乓缓存技术将Camera Link 视频信号编解码并传输,解决了Camera Link 数字视频信号数据量大导电滑环难以实时传输的问题。

试验结果表明,在传输速率120Mb/s 的条件下系统可长时间稳定工作,最高传输速率可达到1.25Gb/s 。

关键词:Camera Link ;光纤传输;FPGA ;乒乓缓存;FIFO 中图分类号:TP394.1;TH691.9文献标识码:A 文章编号:1672-9870(2012)04-0109-04Realization of Camera Link Digital Video FiberTransmission System Based on FPGALI Zhiqiang ,ZHANG Jianhua(Key Laboratory of Airborne Optical Imaging and Measurement ,Changchun Institute of Optics ,Fine Mechanics and Physics ,Chinese Academy of Sciences ,Changchun 130033)Abstract:In order to transmit the high-speed Camera Link digital video signal in the continuous rotate Opto-electronic platform ,we used a fiber-optical rotating connecter instead of the traditional electrical rotating connecter as the transmis-sion medium ,and designed a Camera Link to fiber transmission system based on FPGA.By its strong ability of parallel processing ,it can decode and encode Camera Link digital video by ping-pang operation ,then transmit them.The data of camera link digital video signal is large and the slip ring is difficult to real-time transmisson.But now ,these problems are all resolved by this system in some degree.The result of the examination has proved that the system can work steadily in a long time on the transmit speed of 120Mb/s ,and its top transmit speed can reach 1.25Gb/s.Key words:Camera Link interface ;fiber transmission ;FPGA ;ping-pang cache ;FIFO随着基于数字成像技术的遥感相机和光电设备在视场和分辨率指标要求上的不断提高,所采用的数字CCD 图像数据量急剧增加,同时要将图像传送到上位机实时显示,对传输通道带宽的要求大幅度提高,传统的电传输方式已经很难满足传输速度和传输距离的要求,因此光纤传输技术越来越多地被应于数字图像的传输。

基于FPGA的CameraLink视频转SDI视频的转换器的设计摘要:目前,CameraLink视频无法直接显示,均需经专业采集卡处理后显示,给实际调试应用带来了不便,本文基于Xilinx公司Artix系列的XC7A200T-2FBG484I,设计了CameraLink视频转SDI视频的转换器,无需配备采集卡和调试计算机,可直接在监视器显示。

转换器采用DS90CR286MTD解码接收到的CameraLink视频信号,两片DDR3作为视频处理的缓冲单元,最后经SDI编码芯片输出显示。

关键词:CameraLink FPGA SDI 视频转换器Design of CameraLink video to SDI video converter based on FPGAYANG Zhong-zhou(Luoyang Electro-optical Equipment Research Institute ofAVIC,Luoyang471000,China)Abstract: At present, CameraLink videos cannot be displayed directly, and they all need to be processed by professionalacquisition cards, which brings inconvenience to practical debugging application. In this paper, based on Xilinx Artix series XC7A200T-2FBG484I, a CameraLink video to SDI video converter is designed.It can be displayed directly on the monitor without acquisition card and debugging computer.The converter uses DS90CR286MTD to decode the received CameraLink video signal, and two DDR3 pieces as the bufferunit for video processing. Finally, the SDI encoding chip outputs the display.Keyword: CameraLink FPGA SDI video converter一引言CameraLink标准是由国家半导体实验室提出的一种ChannelLink技术标准,该接口具有开放式的接口协议,使得不同厂家既能保持产品的差异性,又能互相兼容。

由于Camera Link视频协议仅对物理接插件、线缆定义和传输信号规范进行了定义,未对分辨率、帧频和输出时序进行严格的定义,实际应用中方便灵活,同时也带来了极大的不规范及不统一。

实际应用中,Camera Link接口的相机可以输出任意帧频和分辨率的视频图像,但普通监视器对显示视频时序要求严格,视频图像分辨率和帧频都必须符合特定的视频显示标准,因此普通监视器无法直接显示Camera Link视频。

随着数据视频技术的不断发展,越来越多的终端显示采用SDI(Serial Digital Interface,串行数字接口)[1]作为输入接口。

本文将从硬件电路设计到逻辑时序设计出发,设计CameraLink视频转SDI视频的转换器。

二系统组成和工作原理视频转换器包括解码单元、电源管理单元、可编程器件、SDI编码单元和存储器单元。

解码单元将接收的CameraLink串行差分信号转换成TTL电平的并行数字图像信号,包括行有效、场有效、图像数据和时钟信号。

可编程器件(FPGA)单元将图像缓存至存储器单元,根据行有效和场有效计算输入视频的分辨率,FPGA控制缩放单元将图像缩放至SDI视频分辨率,FPGA控制SDI编码单元按照SDI输出时序从存储器单元读取图像数据,最后输出SDI视频至显示器显示。

图1 系统组成和工作原理三硬件设计1、CameraLink解码单元CameraLink视频传输信号由四对LVDS数据信号和一对LVDS时钟信号组成,CameraLink解码单元选用DS90CR286MTD将五对LVDS信号解码为24位数据信号和行信号LVAL、场信号FVAL、空信号和数据有效等28位TTL数据信号,以及一路时钟信号。

FPGA在FVAL和LVAL均有效时,在解码出的时钟的上升沿,采集图像数据,存入缓存单元。

为了保证信号完整性,原理图设计中,需要为LVDS信号进行终端阻抗匹配,以减少终端信号的反射,保证视频信号的完整性,提高信号的传输质量。

2、可编程器件可编程器件选用的XC7A200T-2FBG484I[2]是Xilinx新一代7系列低功耗、低成本FPGA,内部集成215360逻辑单元,13140 Kb的分布式BRAM,10个时钟单元,740个DSP片段,16个GTP高速接口。

可编程器件主要完成图像采集、图像变换、图像存储和图像显示等功能。

图像采集在本设计中主要是针对Cameralink解码的图像数据按照解析出的时序进行数据采集[3];图像变换在本设计中主要是指完成图像缩小、放大等功能,其中图像的缩放均采用IP核来实现;图像存储在本设计中主要是为完成图像显示、图像变换等功能需要对图像进行缓存,在本设计中与FPGA连接的主要缓存为DDR3,其中DDR3采用2片MT41K128M16-125。

图像显示在本设计中指SDI视频的产生,由FPGA按照SDI标准输出规定时序信号,在行信号和场信号均有效时,从存储器单元读取图像数据,输出给SDI驱动芯片显示。

3、电源管理单元根据Xilinx芯片手册,为了使FPGA的IO引脚在FPGA上电过程中保持三态,防止芯片管脚损坏,规定了FPGA各电压上电顺序,VCCINT(1.0V)->VCCBRAM(1.0V)->VCCAUX(1.8V)->VCCO(3.3V,1.8V,1.5V);如果VCCINT和VCCBRAM电压相同可以同时上电,如果VCCAUX和VCCO电压相同也可以同时上电;GTP上电顺序为,VCCINT(1.0V)->MGTAVCC(1.0V)->MGTAVTT(1.2V)。

此外,CameraLink解码芯片、SDI编码芯片需3.3V电压,存储单元DDR3需1.5V和0.75V电压。

选用带输出使能和输出状态的LINEAR公司的LTM4644, LTM4644主要特性如下:4通道4A(峰值5A)电流输出,并联最高可输出16A;输入电压4V~14V;输出电压0.6V~5.5V;在~55℃~125℃之间,输出电压浮动值±1.5%;具有热保护和过流保护功能;有PowerGood信号和电源使能控制信号;通过输出使能和输出状态反馈控制LTM4644各通道的电压输出,达到符合FPGA上电顺序从目的。

4、存储器单元由于CameraLink图像数据为RGB编码格式,而SDI视频为YUV编码格式,需要对图像数据进行颜色空间转换[4];输入的CameraLink图像分辨率未知,在转换为SDI输出时,需要对图像进行放大或缩小;为了满足图像处理对缓存大小的需求,选用2片容量大小128M×16bit(16M×16bit×8banks)的micro公司的MT41K128M16-125 DDR3芯片,支持最高1600Mhz的数据传输速率。

4.SDI编码单元SDI驱动采用TI公司的LMH0387,该芯片主要特性如下:支持ST 424、ST292、ST344、ST259视频编码协议;接收速率为125Mbsp~2.97Gbps;传输距离可达120米;根据需要可配置为输入模式(SDI均衡)或者输出模块(SDI驱动);温度范围:-40℃~+85℃,工业档。

四逻辑设计FPGA逻辑通过QSPI接口完成FPGA程序的固化,通过SPI接口完成SDI均衡驱动芯片LMH0387的参数配置,通过GPIO口完成复位信号产生及分发功能。

FPGA逻辑处理流程如图2所示。

图2 FPGA逻辑处理流程图像数据采集在本设计中主要是针对Cameralink解码,图像数据按照解码产生的控制信号进行数据采集,并将图像数据缓存在外部缓存单元;色彩空间变换将采集到的RGB数据转换为SDI显示需要的YUV数据格式;视频分辨率转换是指逻辑将采集到的Cameralink数据计算出分辨率,通过配置逻辑参数,将分辨率放大或缩小至1920X1080,FPGA逻辑按照高清视频输出时序,向显示单元发送图像数据[5]。

五结论本文设计的Cameralink视频转SDI视频的转换器,可以将Cameralink视频转换为HD-SDI视频在监视器显示,摆脱对专业采集卡和调试计算机的依赖,可以方便的应用于各类Cameralink相机调试场合,具有广阔的市场应用场景。

参考文献:[1]SMPTE259M-Television 10bit 4:2:2 Component and 4fsc Composite Digital Signal-Signal Interface[S].1997[2] Artix-7 FPGAs Data Sheet:DC and AC SwitchingCharacteristics[S].2015[3](美)沃尔夫.《基于FPGA的系统设计》.机械工业出版社.[4](美)冈萨雷斯.《数字图像处理》.电子工业出版社.[5]夏宇闻 . Verilog 数字系统设计教程 . 北京: 北京航空航天大学出版社,2007个人简介:杨中州(1988-),男,硕士研究生,研究方向为数字图像处理。