锁相环电路设计和调试

- 格式:doc

- 大小:18.00 KB

- 文档页数:3

《应用于LVDS的锁相环电路研究》一、引言随着现代电子技术的飞速发展,数据传输速率的要求日益提高,低电压差分信号传输(LVDS)技术因其低功耗、高速度和低噪声的特性,在高速数据传输领域得到了广泛应用。

锁相环(PLL)电路作为LVDS系统中的关键部分,其性能的优劣直接影响到整个系统的稳定性和传输质量。

因此,对应用于LVDS的锁相环电路进行研究具有重要的现实意义。

二、锁相环电路的基本原理锁相环电路是一种闭环相位控制系统,主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成。

其基本原理是通过鉴相器比较输入信号和压控振荡器输出的信号之间的相位差,将相位差转换为电压或电流信号,经过环路滤波器的滤波后,控制压控振荡器的频率和相位,使输出信号的相位与输入信号的相位保持一致。

三、LVDS中锁相环电路的应用在LVDS系统中,锁相环电路主要用于实现数据的同步传输。

由于LVDS采用差分信号传输方式,要求发送端和接收端之间的时钟信号必须保持严格的同步。

锁相环电路通过捕获输入信号的相位信息,将其与压控振荡器输出的信号进行比对和调整,从而保证数据的准确传输。

四、应用于LVDS的锁相环电路设计要点在应用于LVDS的锁相环电路设计中,需要注意以下几个要点:1. 输入范围和稳定性:设计时应考虑到输入信号的范围、频率波动和噪声干扰等因素,确保鉴相器能够准确捕获输入信号的相位信息。

2. 环路滤波器的设计:环路滤波器的作用是滤除鉴相器输出的高频噪声和杂散信号,为压控振荡器提供稳定的控制信号。

设计时需要考虑滤波器的带宽、阶数和稳定性等因素。

3. 压控振荡器的选择:压控振荡器的性能直接影响到锁相环电路的频率和相位调整范围。

选择时需要考虑其频率范围、相位噪声、功耗和稳定性等因素。

4. 电路布局与调试:在电路布局和调试过程中,需要考虑到电磁干扰(EMI)和电磁兼容性(EMC)等问题,确保锁相环电路的稳定性和可靠性。

五、实验结果与分析通过实验验证了应用于LVDS的锁相环电路的有效性和性能。

锁相环实验报告引言在电子、通信和控制系统中,锁相环(Phase-Locked Loop,PLL)是一种广泛应用的反馈控制系统,用于提供稳定的频率和相位锁定。

本实验旨在探究锁相环的原理、结构和性能,并通过实际实验验证其工作原理。

锁相环原理锁相环是一种负反馈控制系统,通常由相频控振荡器(VCO)、相锁环比较器、波形整形电路和滤波器组成。

其基本原理是:通过不断调节VCO的频率,使其输出信号与参考信号的相位差保持在一个稳定的工作范围内。

实验目的1.了解锁相环的基本原理和结构;2.学习锁相环在频率和相位锁定中的应用;3.通过实际实验验证锁相环的工作原理。

实验器材1.锁相环实验台;2.函数信号发生器;3.示波器;4.电压表;5.连接线等。

实验步骤搭建实验平台1.将锁相环实验台与函数信号发生器、示波器和电压表连接;2.正确接入电源,打开锁相环实验台的电源开关; 3.确认各仪器仪表的正常工作。

设置参考信号1.使用函数信号发生器产生一个正弦波信号作为参考信号;2.设置参考信号的频率和幅度。

调节锁相环参数1.调节锁相环的增益参数,观察VCO输出信号的变化;2.尝试不同的锁相环参数组合,观察系统的稳定性和响应性。

改变输入信号1.改变函数信号发生器输出信号的频率;2.观察锁相环的相位锁定和频率锁定过程。

测量锁相环性能1.使用示波器观察锁相环输入信号、输出信号和参考信号的波形;2.使用电压表测量VCO输出信号的频率。

实验结果与分析通过实验我们可以观察到锁相环的工作原理和性能。

在不同的锁相环参数设置下,VCO输出信号的频率和相位与参考信号的变化情况不同。

根据实验数据,我们可以分析锁相环的稳定性、响应速度和抗干扰能力等性能。

结论锁相环是一种广泛应用于电子、通信和控制系统中的反馈控制系统。

通过本实验,我们深入了解了锁相环的原理和结构,并通过实际实验验证了其工作原理。

锁相环具有稳定的频率和相位锁定能力,可以在信号处理和调节控制中起到重要作用。

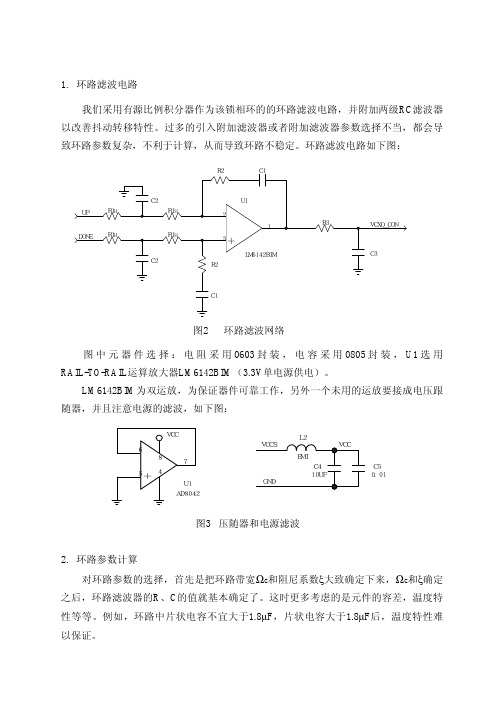

1.环路滤波电路我们采用有源比例积分器作为该锁相环的的环路滤波电路,并附加两级RC 滤波器以改善抖动转移特性。

过多的引入附加滤波器或者附加滤波器参数选择不当,都会导致环路参数复杂,不利于计算,从而导致环路不稳定。

环路滤波电路如下图:图2 环路滤波网络图中元器件选择:电阻采用0603封装,电容采用0805封装,U1选用RAIL-TO-RAIL 运算放大器LM6142BIM(3.3V 单电源供电)。

LM6142BIM 为双运放,为保证器件可靠工作,另外一个未用的运放要接成电压跟随器,并且注意电源的滤波,如下图:0.01C5L2图3 压随器和电源滤波2.环路参数计算对环路参数的选择,首先是把环路带宽Ωc 和阻尼系数ξ大致确定下来,Ωc 和ξ确定之后,环路滤波器的R 、C 的值就基本确定了。

这时更多考虑的是元件的容差,温度特性等等。

例如,环路中片状电容不宜大于1.8µF ,片状电容大于1.8µF 后,温度特性难以保证。

考虑到单板对155.52MHz 时钟抖动要求很高,而且在输入38.88MHz 基准时钟相位发生跳变(主备倒换时,相位有2ns 跳变)时,要求锁相环不能失锁,而是相位缓慢跟踪,所以初步选定环路带宽f c 为50Hz ;阻尼系数ξ为2。

采用理想积分滤波器的锁相环闭环传递函数可写作:H p p p p n nn n ()=+++22222ξωωξωω 式中,,为环路自然角频率。

ωτn K =1,为环路阻尼系数。

ξττ=212K为环路增益,K d 为鉴相灵敏度,K 0为压控灵敏度,N 为分频比。

K K K N d =a. 鉴相器鉴相灵敏度,V m 为鉴相器输出高低电平的差值,因为我们采K V d m=2π用3.3V 工作的FPGA ,V m 可取2.8V ,∴ k d = 2.82o=0.45V /radb. 压控灵敏度 k 0=2oD f vco D V vco∆f vco 为压控振荡器输出范围。

实验11 锁相调频与鉴频实验一、实验目的1.掌握锁相环的基本概念。

2.了解集成电路CD4046的内部结构和工作原理。

3.掌握由集成锁相环电路组成的频率调制电路/解调电路的工作原理。

二、预习要求1.复习反馈控制电路的相关知识。

2.锁相环路的工作原理。

三、实验仪器1.高频信号发生器2.频率计3.双踪示波器4.万用表5.实验板GPMK8四、锁相环的构成和基本原理(1)锁相环的基本组成图11-1是锁相环的基本组成方框图,它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。

图11-1 锁相环的基本组成① 压控振荡器(VCO )VCO 是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO 上的电压。

所谓压控振荡器就是振荡频率受输入电压控制的振荡器。

② 鉴相器(PD )PD 是一个相位比较器,用来检测输出信号0V (t )与输入信号i V (t )之间的相位差θ (t),并把θ(t)转化为电压)(t V d 输出,)(t V d 称为误差电压,通常)(t V d 作为一直流分量或一低频交流量。

③ 环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在)(t V d 中产生的无用组合频率分量及干扰,产生一个只反映θ(t)大小的控制信号)(t V C 。

4046锁相环芯片包含鉴相器(相位比较器)和压控振荡器两部分,而环路滤波器由外接阻容元件构成。

(2)锁相环锁相原理锁相环是一种以消除频率误差为目的反馈控制电路,它的基本原理是利用相位误差电压去消除频率误差。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使)(t V O 与)(t V i 的相位差θ(t)发生变化,该相位差经过PD 转换成误差电压)(t V d 。

此误差电压经过LF 滤波后得到)(t V c ,由)(t V c 去改变VCO 的振荡频率,使其趋近于输入信号的频率,最后达到相等。

锁相环电路设计PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一 PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

如果有相位差存在时,便会产生正或负的脉波输出。

锁相环集成电路设计嘿,朋友们!今天咱就来聊聊锁相环集成电路设计这档子事儿。

你说这锁相环集成电路啊,就像是一个神奇的魔法盒子。

它能把那些杂乱无章的信号变得乖乖听话,整整齐齐地排好队。

就好比一个调皮的孩子,被老师好好管教后变得乖巧懂事了。

咱设计这玩意儿的时候,可得像个细心的工匠,一点一点雕琢。

每个元件的选择,就像给房子选砖头,得挑质量好的,不然房子可就不结实啦!布线呢,就跟给城市规划道路似的,得合理安排,不能这儿堵那儿塞的。

你想想看,如果设计不好,那会出啥乱子呀?信号就跟没头苍蝇似的到处乱撞,那可不行!咱得让它按照咱的想法,稳稳当当、顺顺利利地跑。

在这个过程中,经验可太重要啦!就跟老司机开车一样,开得多了,啥路况都见过,自然就得心应手啦。

要是没经验,那可就像刚学开车的新手,手忙脚乱的。

还有啊,测试也不能马虎。

这就好比给刚做好的衣服检查有没有线头一样,得仔细再仔细。

要是有个小毛病没发现,等用起来出问题了,那不就傻眼啦?设计锁相环集成电路也得有耐心,不能着急。

就像炖一锅好汤,得小火慢慢炖,急不得。

要是火大了,汤就烧干啦,那可就全白费功夫了。

而且啊,这可不是一个人能搞定的事儿,得团队合作。

大家各显神通,把自己的本事都拿出来,一起攻克难题。

这就像一场足球比赛,每个人都有自己的位置和任务,只有配合好了,才能赢得比赛。

你说,要是咱能设计出一个超级厉害的锁相环集成电路,那得多有成就感啊!就跟登上了珠穆朗玛峰似的,那感觉,爽歪歪!总之,锁相环集成电路设计可不是一件容易的事儿,但只要咱用心、细心、有耐心,再加上团队的力量,就一定能把它搞定!让那些信号都乖乖听咱的话,为我们所用!怎么样,是不是觉得很有意思呀?那就赶紧行动起来吧!。

锁相环及频率调制与解调电路一.实验电路图双电源供电调制电路双电源供电解调电路1.配置LM565的工作电源2.调制电路部分(1)调制电路的振荡频率调节与8脚相连的电位器来改变LM565的振荡频率调节为100KHz 第一次改进:为了提高振荡的稳定性,可以采用接晶振来稳定电路,在LM565的2,3脚接入100KHz的正弦波,发现此时的频率变为188KHz,继续调节电位器,使得震荡频率变为100KHz,但是解调电路部分不能解调出信号。

第二次改进:在LM565的2,3脚接入100KHz的正方波,发现此时的频率变为188KHz,继续调节电位器,使得震荡频率变为100KHz,解调电路部分可以解调出信号。

(2)调制指数的验证调制指数为2时:调制信号为12KHz,0.8Vpp的正弦信号最大频偏为24KHz,(如图所示,最小频率为76KHz,最大频率为124KHz,中心频率为100KHz)其频谱为第一类贝塞尔函数,当MF=2时:J0=0.22 J1=0.58 J2=0.35 J3=0.13调制信号调制信号与已调信号(此时频率最大为124KHz)调制信号与已调信号(此时频率最小为76KHz)调制指数为2时的频谱图第一类被贝塞尔函数调制指数为3时:调制信号为8KHz,0.8Vpp的正弦信号最大频偏为24KHz,(如图所示,最小频率为76KHz,最大频率为124KHz,中心频率为100KHz)其频谱为第一类贝塞尔函数,当MF=3时:J0=0.26 J1=0.34 J2=0.49 J3=0.31 J4=0.13调制信号与已调信号(此时频率最大为124KHz)调制信号与已调信号(此时频率最小为76KHz)调制指数为3时的频谱图结论:通过对调制指数2和3情况下的测量,可以与第一类贝塞尔函数当MF分别等于2和3时相比较,十分相近。

并且也可以验证调频波的最大频偏不随调制信号的频率的改变而改变,仅与调制信号的幅度和调制电路的比例常数有关。

基于sopc的锁相环设计班级:XXX姓名:XXX学号:XXX目录基于sopc的锁相环设计 (3)摘要 (3)关键字:全数字锁相环、环路鉴相器、滤波器、数控振荡器 (3)1.引言 (4)2.锁相环简介 (4)2.1锁相环的工作原理: (4)2.2.锁相环的分类 (4)2.3锁相环的应用 (5)3. SOPC简介 (6)3.1 SOPC研究方向 (6)3.2 SOPC的技术内容 (6)3.3 SOPC的应用 (7)4.基于SOPC的锁相环设计 (8)4.1全数字锁相环 (8)4.2全数字锁相环工作原理 (9)4.3全数字锁相环的VHDL设计 (9)5.结语 (16)基于sopc的锁相环设计摘要本次研究的是基于sopc的锁相环设计,锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

锁相环最初用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。

20世纪50年代后期随着空间技术的发展,锁相环用于对宇宙飞行目标的跟踪、遥测和遥控。

60年代初随着数字通信系统的发展,锁相环应用愈广,例如为相干解调提取参考载波、建立位同步等。

具有门限扩展能力的调频信号锁相鉴频器也是在60年代初发展起来的。

在电子仪器方面,锁相环在频率合成器和相位计等仪器中起了重要作用。

关键字:全数字锁相环、环路鉴相器、滤波器、数控振荡器1.引言锁相环的英文全称是Phase-Locked Loop,简称PLL。

其作用是使得电路上的时钟和某一外部时钟的相位同步。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

实验十锁相环调频一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

二、实验使用仪器1.NE564锁相和调频实验板2.200MHz泰克双踪示波器3. FLUKE万用表4. 射频信号发生器5. 低频信号源三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,工作原理压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号与压控振荡器输出信号的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO 输出信号的相位和输入信号的相位保持某种特定的关系,达到相位 锁定的目的。

*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

这种锁相环路称载波跟踪型PLL ,本实验中使用的锁相环是NE564。

NE564内部压控振荡器的最高工作频率是50MHz ,从图10-5的逻辑框图中可以看到,NE564的内部包含一个限幅放大器,对外部的输入信号进行限幅放大,抑制寄生调幅,内部还包含压控振荡器和相位比较器。

锁相环电路设计和调试

1. 锁相环的设计的起因:

这个电路设计的初衷就是为了我项目中的DDS电路提供可选的时钟输入。因为我选用的DDS电路本身自带有

内部的倍频器,其实现的方法就是内部的锁相环。开始我一位内部的锁相环会比我自己外部设计性能更好,但

是后来查到AD的技术资料,发现内部的锁相环的性能并不是达到很好的配置,仔细一想,也是这样的,因为

外部的环路滤波器的配置对于任意的频率都如此,显然没有经过精心设计的更加有效果。鉴于上面分析的原因,

我把采用锁相环提供时钟作为一项可选的优化方案。

再有一个原因,就是大学的时候采用的锁相环,到最后也没有调好,所以对这件事情还是老放不下,所以想借

此机会完善一下这个过程。

2. 锁相环的设计过程:

整个设计过程,比起dds电路来说,时间是非常的短的。原因之一就是整个PLL的设计就是一个芯片实现。比

大学的PLL要简单一些。再有就是,这个毕竟不是项目的重点,而是一个改进方案。电路板采用两层板设计,

环路滤波器在背板设计。环路滤波器的设计采用AD公司的ADSIMPLL。开始的供电设计,由于电路板的走线

上比较困难,所以采用多处引线的方法。后来调试过程中发现,这样做是在是太麻烦,也比较危险,因为万一

出现加反电,或加错电压就危险了。所以我建议以后做电路时,采用通用的便携式的变压器插头,这样调试起

来就非常的简单了,不用再依赖于庞大的稳压电源了,而且绝对不会出现危险。调试时发现电路中的测试点对

于测试非常的方便,对于地,可以留两个焊盘,然后安装弧形的金属勾,这样对于采用示波器测试是非常方便

的,可以很方便的用小架子加上。再有就是安装孔的问题,内径为3mm的安装空可以采用通用的八角螺母进

行固定,这样对于调试和焊接,即方便有安全。在一个就是SMA接头到底是选朝上的还是侧面的,其实再对于

空间和对接口电路要求来考虑。在PCB 中间的接头肯定是选朝上的。如果没有别的要求,在电路板的边上的信

号尽量采用侧面的接头。调节电流在技术资料上说是典型为50uA,最大值为100uA.我采用的是50K的电位器

调节。25K*50uA=1.25V。显然由于输入的变化造成输出的变化是一定的。建议以后采用值比较小的电阻或

电位器。

3. 锁相环的调试过程:

真正是调试才能发现设计中的问题。太哦是工程的第一件就是先调节电源电路。在电电原的调试过程中,我发

现LM317输出总是受到输入的影响。可能就是因为调节端子的电流在输出端产生的电压太大了,这个原因可能

和我采用比较的大电位器来作为调节电阻有关。

着就是晶振的问题。我采用的是KSS的晶振。发现这个晶振每个的引脚在晶振的下面,而后每个引脚的侧面有

两个小的引脚,后来发现其中的一个并没有和下面的引脚连在一起。在第一次焊接的时候就是没有注意到这个

问题,然后把侧面的两个都连上,最后没出信号。后来正确的安装后就号了。引脚的顺序,带点的引脚和与其

相邻的引脚要接3.3V的电压,一个是电源引脚另一个是选通引脚。与带点的引脚相对角的是输出引脚。另一个

引脚接地,整个晶振的外壳是接地的。因为这个资料不太好查,所以这里说明一下供以后参考。

这些配置完,然后按照仿真的结果把环路滤波器电阻和电容安装好。接着就是单片机程序的调试了。我特意在

一次机会买了个特价的PIC 单片机的调试工具PICKIT2 DEBUG express,后来买到之后发现这个的调试功能

有限,不能支持PIC12xx系列的单片机。这个对于我的调试极为的不方便。这的进行烧写。在烧写过程中也一

直报错,原因好像是USERID的问题,后来经过几次的尝试,始终不行。最后我采用的是开发板自带的pic单

片机PIC16F917,开始的时候采用SPI 模式进行工作,但是后来一直不太理想。最后采用最原始的高低电平的

变换来模拟时钟的方法。最后采用这种方法成功了。但是其中还是遇到了很多的问题。开始我并不是很清楚PIC

单片机的存储结构的问题。PIC 的单片机有程序存储器和数据存储器。对于PIC16F917来说,他的程序存储

器和数据存储器都有四个页面。当程序很长时,需要占用多个页面。但是目前我还没有学要那么长。是否在不

同页面调用程序要切换程序存储器页面,还没研究过。但是在数据存储器间进行访问时,一定要这样切换页面。

一般的主要是若干个特殊的寄存器的频繁的使用问题。

这个问题解决了之后,在调试的过程还是不太理想。我跟本不知道我写入的控制字到底有没有写到PLL 的寄存

器中,因为我得频谱仪上一直有信号,让我我发判断输出的不正确是1。由于环路滤波器的失锁,还是由于我

得2。控制字写错了,还是我得3。控制字根本没写进去,后来我把控制字中的一项,使得芯片进入Power_ down

模式,马上输出没了,这样我排除了情况3的可能性,说明我写入的方式是正确的,已经被芯片所接受。接着

我采用AD公司关于ADF4360-7评估板的配套软件,通过设置我得选项,然后我发现他显示的寄存器的的值

和我设置的一样,所以我排除了情况2。在调试的时候我相应的改变了一些N的值,发现却是输出有变化,但

是这并没起我太多的注意。但是我发现这些值都比我设置的500M 的频率要小。后来我又反查了一下公司的资

料,发现有一个应用电路,输出50M,然而却采用的是13nH的电感对芯片的内部的VCO进行配置。而我使

用仿真软件算出来的是15nH的值。后来我发现资料上有一个曲线,就是每个频率段对应的电感值。后来发现

15nH应该是理想值。如果按照实际来算的话,VCO 的中心频率应该在430Mhz左右(不一定准确,读图得

到的值)。这样我就特意的把N的值减小,发现果然有效果。再这过程中,因为使用时忘记了按上了频谱仪的

MAKER跟踪功能,所以每次改变N的时候,我看到了信号频谱有一个抖动,但是最后还是在屏幕的正中,后

来才发现其实MAKER的值已经变了,只是被重新锁定到屏幕中央了。后来经过改动几次N值,发现基本上可

以,但是输出的信号还是比设定的频率要低一些。最后测试了以下晶振的频率,发现晶振并没有在25M,而是

24.1M的样子,这样基本上差不多了。输出频率也非常的稳定。

再有一个需要说的是,这次通过频谱仪观测晶振的时钟才发现晶振输出的方波又丰富的谐波分量,2,3,4次

谐波的功率并不比基频小多少,小差不多10dBm的样子。才知道通过取谐波来获得高频是可取的。

4. 电路需要进一步完成的工作:

首先,我要还一个13nH的电感,但是后来我没买到,这个只能自己来用线圈来绕,然后固定了。接着就是

PIC16F917的SPI 模式的调试工作,因为这个我以后还要用,所以肯定有一天要解决。在一个就是PIC 12XX

单片机的烧写问题,可能我上次没成功写入,原因是可能单片机已经坏了。这些工作以后要逐渐来完成。

5. 技术之外的事:

这次能够很快的调出电路,还有一个重要的原因,就是我厚着脸皮把频谱议搬到实验室,这样才能够和我得机

器一起来调试,从而才能发现以上的问题,进一步解决。想想这个事,我最多被说两句,但是电路调好了,谁

还会说那,况且我已经和老师打了招呼。反而问题解决不了,在乱处找借口,才是不应该的,也是老师和领导

最讨厌的。

6. 总结

执着的做一件事,总会有回报的。