6.3 锁相环路(PLL)电路设计实例

- 格式:ppt

- 大小:599.50 KB

- 文档页数:23

锁相环的原理2007-01-23 00:241.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

1摘 要随着通信及电子系统的飞速发展,促使集成锁相环和数字锁相环突飞猛进。

本次毕业设计的主要任务是,采用0.180.18μμm CMOS 工艺,设计实现一个基于改进的鉴频鉴相器,压控振荡器,环路滤波器的全集成的CMOS PLL 锁相环电路,设计重点为PLL 锁相环电路的版图设计,设计工具为Laker 。

本论文介绍了PLL 锁相环电路的基本原理以及其完整的版图设计结果。

本次设计表明,采用该方案实现的锁相环电路主要功能工作正常,初步达到设计要求。

求。

关键词:PLL 锁相环电路,鉴频鉴相器,压控振荡器,环路滤波器,版图设计,0.180.18μμm CMOS 工艺工艺AbstractWith the development of the communications and electronic systems, the technology of the integrated PLL and digital PLL develops rapidly.The main task of graduation is to design and realize a fully integrated CMOS PLL circuit which is based on an improved phase detector, VCO, loop filter using the 0.18μm CMOS technology 0.18μm CMOS technology. The design focus on the layout of the PLL circuit, and the . The design focus on the layout of the PLL circuit, and the design tools is the Laker.This paper introduces the basic principles of PLL phase locked loop circuit and its comprehensive layout results. This design shows that the program implemented by the main function of PLL circuit is working well, and it meets the design requirements.Key words:PLL phase locked loop circuits, popularly used phase detectors, discrimination, VCO loop filter, layout design, 0.18 μm CMOS process目 录 (11)摘 要.............................................................................................................................. (22)Abstract .......................................................................................................................... (44)第1章 绪论................................................................................................................ (44)1.1 锁相技术的发展.............................................................................................. (44)1.2 锁相环路的主要特性......................................................................................1.3 PLL锁相环的应用领域 (5)第2章 基于CMOS锁相环的电路设计 (7)2.1 锁相环的基本组成.......................................................................................... (77) (77)2.2 锁相环工作原理.............................................................................................. (88)2.3 鉴相器..............................................................................................................2.3.1 鉴频鉴相器(PFD) (9) (110)2.3.2 鉴频鉴相器设计.................................................................................. (110)2.4 环路滤波器....................................................................................................11 (11)2.5 压控振荡器....................................................................................................第3章 关于COMS锁相环的版图设计 (12) (112)3.1 电路设计........................................................................................................3.2 版图设计........................................................................................................ (112) (113)3.2.1 版图设计规则检查.............................................................................. (113)3.2.2 注意事项..............................................................................................3.3 锁相环的版图设计........................................................................................ (115) (117)第4章 结束语............................................................................................................ (118)参考文献...................................................................................................................... (119)致谢..............................................................................................................................第1章 绪论1.1锁相技术的发展 锁相技术起源于20世纪30年代,提出无线电调幅信号的锁相同步检波技术。

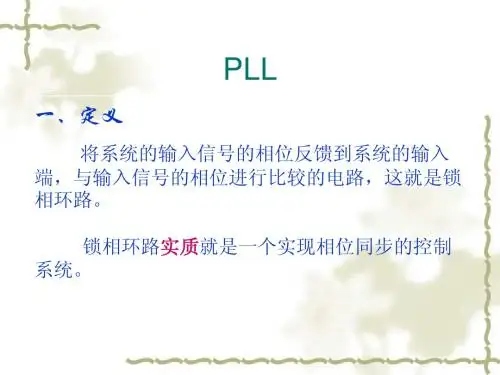

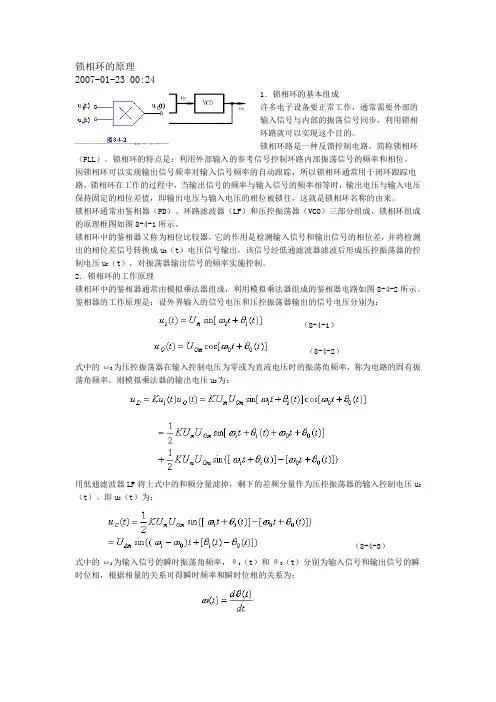

锁相环的原理2007-01-23 00:241.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

锁相环(PLL)详解

锁相环(PLL)详解锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

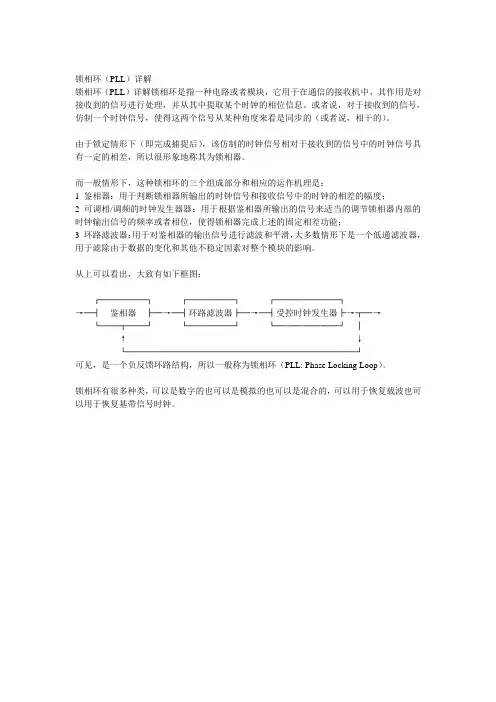

而一般情形下,这种锁相环的三个组成部分和相应的运作机理是:

1 鉴相器:用于判断锁相器所输出的时钟信号和接收信号中的时钟的相差的幅度;

2 可调相/调频的时钟发生器器:用于根据鉴相器所输出的信号来适当的调节锁相器内部的时钟输出信号的频率或者相位,使得锁相器完成上述的固定相差功能;

3 环路滤波器:用于对鉴相器的输出信号进行滤波和平滑,大多数情形下是一个低通滤波器,用于滤除由于数据的变化和其他不稳定因素对整个模块的影响。

从上可以看出,大致有如下框图:

┌─────┐┌─────┐┌───────┐

→─┤鉴相器├─→─┤环路滤波器├─→─┤受控时钟发生器├→┬─→└──┬──┘└─────┘└───────┘│

↑↓

└──────────────────────────┘

可见,是一个负反馈环路结构,所以一般称为锁相环(PLL: Phase Locking Loop)。

锁相环有很多种类,可以是数字的也可以是模拟的也可以是混合的,可以用于恢复载波也可以用于恢复基带信号时钟。

三相逆变器锁相环pll 工作原理三相逆变器是一种将直流电能转换为交流电能的设备。

它通常由逆变电路和控制电路两部分组成。

锁相环(Phase-Locked Loop,PLL)是三相逆变器中的一个重要组成部分,用于实现电网电压和逆变器输出电压之间的同步控制。

锁相环(PLL)是一种用于提取频率和相位信息的控制系统。

在三相逆变器中,PLL的主要功能是将电网电压的频率和相位信息提取出来,并与逆变器的输出电压进行比较,以实现同步控制。

具体来说,锁相环通过不断调整逆变器的输出频率和相位,使其与电网电压保持同步,从而实现电能的高效转换。

锁相环的工作原理可以简单地分为三个步骤:相频检测、滤波和控制。

首先,相频检测器会对电网电压和逆变器输出电压进行相频检测,得到它们之间的相位差和频率差。

然后,滤波器会对相位差和频率差进行滤波处理,以减小干扰和噪声的影响。

最后,控制器根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在具体实现中,锁相环通常由相频检测器、环路滤波器和控制器三部分组成。

相频检测器可以通过比较电网电压和逆变器输出电压的相位差和频率差来提取同步信息。

环路滤波器则用于对相位差和频率差进行滤波处理,以消除噪声和干扰的影响。

控制器则根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在三相逆变器中,锁相环的工作原理非常重要。

通过锁相环的同步控制,可以有效地实现逆变器输出电压与电网电压的同步,从而提高逆变器的转换效率和功率质量。

同时,锁相环还具有快速响应、高精度和抗干扰等特点,能够在电网电压波动或扰动的情况下保持逆变器的稳定运行。

总结起来,三相逆变器中的锁相环是一种用于实现电网电压和逆变器输出电压同步控制的重要组成部分。

它通过相频检测、滤波和控制等步骤,不断调整逆变器的输出频率和相位,使其与电网电压保持同步。

锁相环的工作原理能够有效提高逆变器的转换效率和功率质量,并具有快速响应、高精度和抗干扰等特点,能够保持逆变器的稳定运行。

硬件锁相环(Phase-Locked Loop,简称PLL)是一种常用的电路设计技术,主要用于实现频率合成、时钟恢复和数据同步等功能。

它由相位比较器、环路滤波器、控制电压源和振荡器等组成。

在硬件锁相环电路中,相位比较器用于比较输入信号与参考信号的相位差,并将差值输出给环路滤波器。

环路滤波器对相位差进行滤波处理,以产生一个控制电压。

控制电压源根据环路滤波器的输出来调节振荡器的频率或相位,使得输入信号与参考信号的相位差最小化。

通过不断调整振荡器的频率或相位,硬件锁相环电路可以将输入信号的频率合成到期望的频率,实现频率合成的功能。

同时,它还可以用于恢复时钟信号的稳定性,对于需要高精度时钟的应用非常有用。

此外,硬件锁相环电路还广泛应用于数据通信系统中的数据同步功能。

通过锁定接收端的本地时钟与发送端的时钟相位,可以确保数据传输的准确性和可靠性。

总结来说,硬件锁相环电路是一种基于相位比较和反馈控制原理的电路设计技术,可以实现频率合成、时钟恢复和数据同步等功能。

它在通信、计算机、测量和控制等领域有着广泛的应用。

基于MC145152+MC12022+MC1648L+LM358 的锁相环电路一、MC145152(鉴相器)MC145152-2 芯片是摩托罗拉公司生产的锁相环频率合成器专用芯片。

它是MC145152-1 芯片的改进型。

主要具有下列主要特征:(1)它与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出MC。

当MC 为低电平时,双模分频器用(P+1)去除;当MC 为高电平时,双模分频器用模数P 去除。

(2)它有 A 计数器和N 计数器两个计数器。

它们与双模(P/(P+1))分频器提供了总分频值(NP+A)。

其中,A、N 计数器可预置。

N 的取值范围为3~1023,A 的取值范围为0~63。

A 计数器计数期间,MC 为低电平;N 计数器计数(N-A)期间,MC 为高电平。

(3)它有一个参考振荡器,可外接晶体振荡器。

(4)它有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值范围:8,64,128,256,512,1024,1160,2048。

设置方法通过改变RA0、RA1、RA2的不同电平,接下来会讲到。

(5)它有两路鉴相信号输出,其中,ФR、ФV 用来输出鉴相误差信号,LD 用来输出相位锁定信号。

MC145152-2 的供电电压为3.0 V~9.0 V,采用28 脚双列封装形式。

MC145152-2的原理框图如图1 所示MC145152-2 的工作原理:参考振荡器信号经R 分频器分频后形成fR 信号。

压控振荡器信号经双模P/(P+1)分频器分频,再经A、N 计数器分频器后形成fV 信号,fV=fVCO/(NP+A)。

fR 信号和fV 信号在鉴相器中鉴相,输出的误差信号(φR、φV)经低通滤波器形成直流信号,直流信号再去控制压控振荡器的频率。

当整个环路锁定后,fV=fR 且同相,fVCO=(NP+A)fV=(NP+A)fR,便可产生和基准频率同样稳定度和准确度的任意频率。

原理框图如右图:管脚描述:Pin 1频率输入(fin) 输入到上升沿触发÷N和÷A计数器。

锁相环(PLL)电路设计摘要:本次课程设计的锁相环电路其原理就是先把电网三相交流电压合成一相正弦波,合成后其频率还是不变(50Hz),然后把正弦波转变成方波,由此将信号送入锁相环集成器件CD4046(由鉴相器,环路滤波器,VCO组成),通过将输入信号与VCO输出信号或VCO输出经分频器的信号相位或频率的比较,控制两个信号使其保持同相位,从而实现对输入信号的同步跟踪。

关键字:锁相环,鉴相器,环路滤波器,集成运算电路,比较器Abstract:This curriculum designs phase-locked loop electric circuit its principle is synthesizes first the electrical network three-phase AC voltage a sine wave, after the synthesis its frequency invariable (50Hz), then transforms the sine wave the square-wave, from this sends in the signal phase-locked loop integration component CD4046 (by discriminator, ring circuit filter, VCO is composed), through the input signal and the VCO output signal either the VCO output after the frequency divider signal phase or the frequency comparison, will control two signals to cause its maintenance with the phase, thus will realize to the input signal lock following.Keyword:PLL, phase detector and loop filter, integrated computing circuits, Comparators目录1.前言(绪论) (3)2.总体方案设计 (4)3.单元模块设计 (5)3.1 集成运算加法器.......................................................................... 错误!未定义书签。