第四章 触发器

- 格式:ppt

- 大小:1.04 MB

- 文档页数:34

第4章触发器教学目标●熟悉基本触发器的组成和功能●掌握基本RS触发器、同步RS触发器、边沿D和JK触发器功能●熟练掌握各种不同逻辑功能触发器之间的相互转换数字系统中除采用逻辑门外,还常用到另一类具有记忆功能的电路--触发器,它具有存储二进制信息的功能,是组成时序逻辑电路基本储存单元。

每个触发器能够记忆一位二进制数“0”或“1”。

4.1概述触发器是一种典型的具有双稳态暂时存储功能的器件。

在各种复杂的数字电路中不但需要对二进制信号进行运算,还需要将这些信号和运算结果保存起来。

为此需要使用具有记忆功能的基本逻辑单元。

能存储1位二进制的基本单元电路称为触发器。

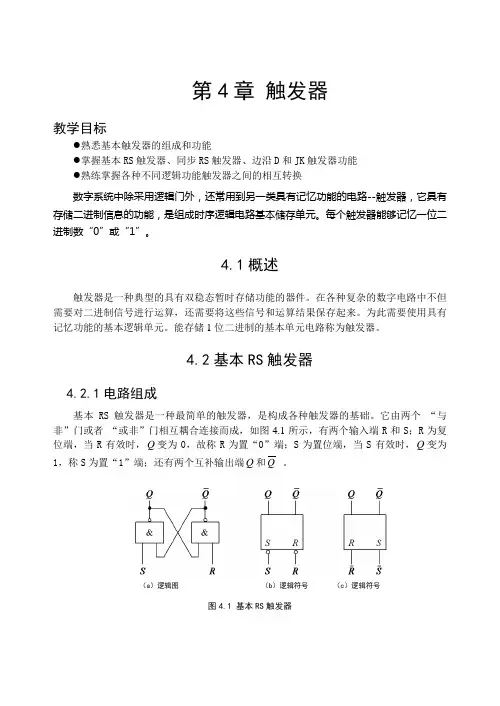

4.2基本RS触发器4.2.1电路组成基本RS触发器是一种最简单的触发器,是构成各种触发器的基础。

它由两个“与非”门或者“或非”门相互耦合连接而成,如图4.1所示,有两个输入端R和S;R为复位端,当R有效时,Q变为0,故称R为置“0”端;S为置位端,当S有效时,Q变为1,称S为置“1”端;还有两个互补输出端Q和Q。

(a)逻辑图(b)逻辑符号(c)逻辑符号图4.1 基本RS触发器4.2.2 功能分析触发器有两个稳定状态。

nQ 为触发器的原状态(初态),即触发信号输入前的状态;1n Q+为触发器的现态(次态),即触发信号输入后的状态。

其功能用状态表、特征方程式、逻辑符号图以及状态转换图、波形图描述。

1. 状态表如图4.1(a )可知: Q S Qn ⋅=+1,n n Q R Q ⋅=+1从表4.1中可知:该触发器有置“0”、置“1”功能。

R 与S 均为低电平有效,可使触发器的输出状态转换为相应的0或1。

RS 触发器逻辑符号如图4.1(b)、(c)所示,图中的两个小圆圈表示输入低电平有效。

当R 、S 均为低电平时有两种情况:当R=S=0,Q = Q =1,违犯了互补关系;当RS 由00同时变为11时,则Q (Q )输出不能确定。

表4.1 状态表2. 特性方程根据表4.1画出卡诺图如图4.2所示,化简得: n n RQ S Q+=+1(4-1)1=+S R (约束条件)图4.2 卡诺图3. 状态转换图如图4.3所示,图中圆圈表示状态的个数,箭头表示状态转换的方向,箭头线上标注表示状态转换的条件。

第四章触发器★主要内容1.基本触发器2.同步触发器3.边沿触发器4.时钟触发器的功能分类、功能表示方法及转换5.触发器的电气特性6.触发器的VHDL描述及其仿真★教学目的和要求1、熟练掌握基本RS触发器的电路组成和逻辑功能分析(会列真值表和画波形图);2、掌握时钟脉冲控制的同步RS触发器的电路组成和逻辑功能(会列真值表、特性方程和画波形图);3、熟练掌握D.JK边沿触发器的的工作特点及逻辑功能;正确区分电平触发和边沿触发的概念。

4、时钟触发器的功能分类、功能表示方法及转换;了解触发器的电气特性。

5、理解触发器的VHDL描述例子,会利用MAX+PLUS Ⅱ软件对触发器功能进行仿真,能根据仿真结果波形清楚各个触发器的功能。

★学时数:6学时★重难点重点:各种触发器的逻辑功能和触发方式。

难点:边沿JK、D触发器的结构。

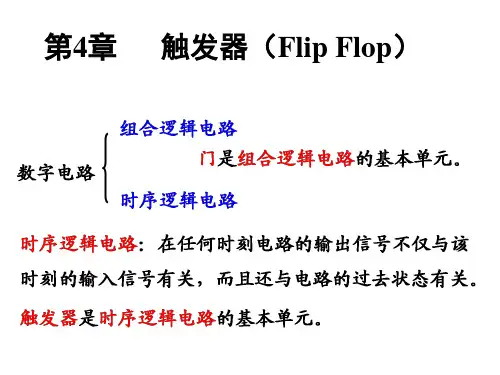

第四章 触发器上一章学习了组合逻辑电路:(1)SSI 构成;(2)中规模部件构成。

全加器、比较器、译码器、数据选择器、编码器。

组合电路和时序逻辑电路是数字电路的两大类,时序电路具有记忆功能,它的某一时刻输出信号,不仅取决于当时的输入信号,而且还与电路原来状态有关。

触发器是构成时序电路的基本单元,因此,在学习时序电路之前,必需先掌握触发器(了解电路结构,掌握其功能和触发方式、熟悉逻辑符号等),特别是D 触发器和JK 触发器。

概述:1、触发器的基本要求:每个触发器都有两个互非的输出端Q 和Q ,如SR 触发器。

①触发器应有两个稳定的状态“0”态:0=Q ,1=Q ;“1”态:1=Q ,0=Q 。

稳定:触发器在没有触发信号作用下,维持原来状态不变。

②能够接收,保存和输出一位二进制信息“1”和“0”。

2、触发器的现态和次态现态n Q —— 触发器接收输入信号之前的状态 次态1+n Q —— 触发器接收输入信号之后的状态。

3、触发器的分类:① 基本触发器(没有时钟输入端)。

② 时钟触发器(有时钟脉冲输入端,触发器按时钟节拍动作)。