第4章 触发器(总复习)

- 格式:doc

- 大小:188.00 KB

- 文档页数:6

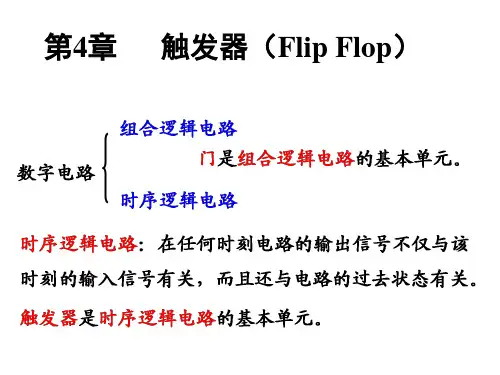

第4章触发器教学目标●熟悉基本触发器的组成和功能●掌握基本RS触发器、同步RS触发器、边沿D和JK触发器功能●熟练掌握各种不同逻辑功能触发器之间的相互转换数字系统中除采用逻辑门外,还常用到另一类具有记忆功能的电路--触发器,它具有存储二进制信息的功能,是组成时序逻辑电路基本储存单元。

每个触发器能够记忆一位二进制数“0”或“1”。

4.1概述触发器是一种典型的具有双稳态暂时存储功能的器件。

在各种复杂的数字电路中不但需要对二进制信号进行运算,还需要将这些信号和运算结果保存起来。

为此需要使用具有记忆功能的基本逻辑单元。

能存储1位二进制的基本单元电路称为触发器。

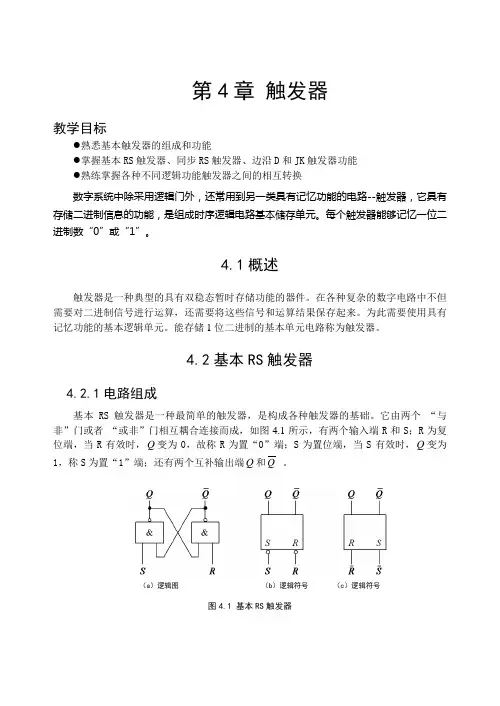

4.2基本RS触发器4.2.1电路组成基本RS触发器是一种最简单的触发器,是构成各种触发器的基础。

它由两个“与非”门或者“或非”门相互耦合连接而成,如图4.1所示,有两个输入端R和S;R为复位端,当R有效时,Q变为0,故称R为置“0”端;S为置位端,当S有效时,Q变为1,称S为置“1”端;还有两个互补输出端Q和Q。

(a)逻辑图(b)逻辑符号(c)逻辑符号图4.1 基本RS触发器4.2.2 功能分析触发器有两个稳定状态。

nQ 为触发器的原状态(初态),即触发信号输入前的状态;1n Q+为触发器的现态(次态),即触发信号输入后的状态。

其功能用状态表、特征方程式、逻辑符号图以及状态转换图、波形图描述。

1. 状态表如图4.1(a )可知: Q S Qn ⋅=+1,n n Q R Q ⋅=+1从表4.1中可知:该触发器有置“0”、置“1”功能。

R 与S 均为低电平有效,可使触发器的输出状态转换为相应的0或1。

RS 触发器逻辑符号如图4.1(b)、(c)所示,图中的两个小圆圈表示输入低电平有效。

当R 、S 均为低电平时有两种情况:当R=S=0,Q = Q =1,违犯了互补关系;当RS 由00同时变为11时,则Q (Q )输出不能确定。

表4.1 状态表2. 特性方程根据表4.1画出卡诺图如图4.2所示,化简得: n n RQ S Q+=+1(4-1)1=+S R (约束条件)图4.2 卡诺图3. 状态转换图如图4.3所示,图中圆圈表示状态的个数,箭头表示状态转换的方向,箭头线上标注表示状态转换的条件。

《数字逻辑与电路》复习题第一章数字逻辑基础(数制与编码)一、选择题1.以下代码中为无权码的为CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为AB 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.一位十六进制数可以用 C 位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD码表示为 B 。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是CD 。

A.(256)10B.(127)10C.(FF)16D.(255)106.与十进制数(53.5)10等值的数或代码为ABCD 。

A. (0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.与八进制数(47.3)8等值的数为:A B。

A.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)28.常用的BC D码有C D 。

A.奇偶校验码B.格雷码C.8421码D.余三码二、判断题(正确打√,错误的打×)1. 方波的占空比为0.5。

(√)2. 8421码1001比0001大。

(×)3. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

(√)4.格雷码具有任何相邻码只有一位码元不同的特性。

(√)5.八进制数(17)8比十进制数(17)10小。

(√)6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

(√)7.十进制数(9)10比十六进制数(9)16小。

(×)8.当8421奇校验码在传送十进制数(8)10时,在校验位上出现了1时,表明在传送过程中出现了错误。

(√)三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其高电平和低电平常用1和0来表示。

【总复习卷】第4章集成触发器触发器是数字电路中的一个基本逻辑单元,它与逻辑门电路一起组成各种各样的数字电路。

触发器具有记忆功能并且其状态在触发脉冲作用下迅速翻转。

【知识结构图】【本章重点】1. 触发器的基本性质。

2. RS触发器、JK触发器、D型触发器的逻辑功能,各类触发器逻辑符号。

3. 集成触发器外特性及其应用。

【本章难点】1. 各类触发器逻辑功能分析。

2. 主从型触发器工作波形画法。

3. 集成触发器简单应用。

4. 触发器的空翻。

【本章考点】1. 各类触发器逻辑符号及相应逻辑功能。

2. 触发器的工作波形。

3. 集成触发器类型识别及简单应用。

4. 触发器的空翻。

综合训练(第4章)一、填空题1.触发器具有________种稳定状态。

在输入信号消失后,能保持输出状态不变,也就是说它具有________功能。

在适当触发信号作用下,从一个稳态变为另一个稳态,,因此触发器可作为_______进制信息存贮单元。

2. 边沿型触发器可以避免现象的产生。

3. 通常规定触发器______端的状态作为触发器的状态。

4. 触发器按照逻辑功能分为:、、、等。

5. 主从触发器在时钟高电平时主触发器接收信,而__ __触发器状态不变。

在时钟脉冲下降沿时__主__触发器被封锁而__ ___触发器打开接收触发器信号。

6. 与非门构成的基本RS触发器的约束条件是R+S不能为。

7. 基本触发器电路中,S D端、R D端可以根据需要预先将触发器或,而不受的同步控制。

8. 在时钟脉冲控制下,JK触发器J端和K端输入不同组合的信号时,能够具有、、、的功能。

二、判断题(对的打”√”,错的打”Х”)1. 触发器属于组合逻辑电路系列,即没有记忆功能。

( )2. 同步RS触发器连成计数电路时,会产生空翻现象。

( )3. 主从RS触发器会出现状态不定的现象。

( )4. 主从型触发器接成计数电路时,不会产生空翻现象。

( )5. 当JK触发器的,它就转化为T触发器。

第四章 触发器【题4.1】 画出图P4.1由与非门组成的基本RS 触发器输出端Q 、Q 的电压波形,输入端D S 、D R 的电压波形如图中所示。

【解】 见图A4.1。

图A4.1S DRDS图P4.1【题 4.2】 画出图P4.2由或非门组成的基本RS 触发器输出端Q 、Q 的电压波形,输入端D S 、D R 的电压波形如图中所示。

【解】 见图A4.2。

S DRR D QQS D图P4.2S D图A4.2【题4.3】 试分析图P4.3所示电路的逻辑功能,列出真值表,写出逻辑函数式。

【解】 由真值表得10n n Q S RQ SRSR +⎧=+⎨=⎩化简后得到10n n Q S RQ SR +=+=RS图 P4.3【题4.4】 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接通瞬间发生振颤, D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

V CCD SD R图P4.4【解】 见图A4.4。

D RQQD S图A4.4【题4.5】 在图P4.5电路中,若CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q=0。

【解】 见图A4.5。

S RCP图P4.5【题4.6】 若将同步RS 触发器的Q 与R 、Q 与S 相连,如图P4.6所示, 试画出在CP 信号作用下的Q 和Q 端对应的电压波形。

已知CP 信号的宽度4w pd t t =。

pd t 为门电路的平均传输延迟时间,假定pd t ≈PHL t ≈PLH t 。

设触发器的初始状态为Q=0。

【解】 见图A4.6。

(参见第4.4.2节同步RS 触发器的动态特性。

)图A4.5CP图 P4.6Q Q图A4.6【题4.7】若主从结构RS触发器各输入端的电压波形如图P4.7中所给出, 试画出Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

RCPSR图P4.7【解】见图A4.7。

【总复习卷】

第4章集成触发器

触发器是数字电路中的一个基本逻辑单元,它与逻辑门电路一起组成各种各样的数字电路。

触发器具有记忆功能并且其状态在触发脉冲作用下迅速翻转。

【知识结构图】

【本章重点】

1. 触发器的基本性质。

2. RS触发器、JK触发器、D型触发器的逻辑功能,各类触发器逻辑符号。

3. 集成触发器外特性及其应用。

【本章难点】

1. 各类触发器逻辑功能分析。

2. 主从型触发器工作波形画法。

3. 集成触发器简单应用。

4. 触发器的空翻。

【本章考点】

1. 各类触发器逻辑符号及相应逻辑功能。

2. 触发器的工作波形。

3. 集成触发器类型识别及简单应用。

4. 触发器的空翻。

综合训练(第4章)

一、填空题

1.触发器具有________种稳定状态。

在输入信号消失后,能保持输出状态不变,也就是说它具有________功能。

在适当触发信号作用下,从一个稳态变为另一个稳态,,因此

触发器可作为_______进制信息存贮单元。

2. 边沿型触发器可以避免现象的产生。

3. 通常规定触发器______端的状态作为触发器的状态。

4. 触发器按照逻辑功能分为:、、、等。

5. 主从触发器在时钟高电平时主触发器接收信,而__ __触发器状态不变。

在时钟

脉冲下降沿时__主__触发器被封锁而__ ___触发器打开接收触发器信号。

6. 与非门构成的基本RS触发器的约束条件是R+S不能为。

7. 基本触发器电路中,S D端、R D端可以根据需要预先将触发器或,

而不受的同步控制。

8. 在时钟脉冲控制下,JK触发器J端和K端输入不同组合的信号时,能够具

有、、、的功能。

二、判断题(对的打”√”,错的打”Х”)

1. 触发器属于组合逻辑电路系列,即没有记忆功能。

( )

2. 同步RS触发器连成计数电路时,会产生空翻现象。

( )

3. 主从RS触发器会出现状态不定的现象。

( )

4. 主从型触发器接成计数电路时,不会产生空翻现象。

( )

5. 当JK触发器的,它就转化为T触发器。

( )

6. JK触发器的特性方程是。

( )

7. 当J=K=0时,JK触发器就具有计数的功能。

( )

8. 由触发器工作性质可看出触发器是一个双稳态电路。

( )

9. 触发器的抗干扰能力,与触发脉冲宽度无关。

( )

10. 同步RS触发器状态的改变是与时钟脉冲信号同步的。

( )

11. 与非门构成的基本RS触发器,当S=1,R=0时,其输出端状态是1。

( )

12. 同步RS触发器的约束条件是SR=0。

( )

三、单项选择题

1. 触发器是时序逻辑电路的基本单元,它能够存储一位二进制数码,当输入信号消失后,

状态保持不变,即:( )。

A.具有记忆功能

B.不具有记忆功能

2. 触发器连接成计数器时,不产生空翻的触发器是( )。

A. 主从JK触发器

B. 同步RS触发器

C. 边沿型JK触发器

D. 主从D触发器

3. 如下图触发器电路中,特性方程为Q n+1=Q n的电路是( )(多选题)

4、触发器和CP脉冲以及D端波形如图所示,设触发器初态为0,则Q端的波形是()。

5、图5所示的触发器电路,设触发器初态均为0,在第3个CP脉冲作用后,Q0Q1的状态为()。

A. Q0Q1=11

B. Q0Q1=10

C. Q0Q1=00

D. Q0Q1=01

6、图6所示触发器电路,设触发器初态均为0,在第3个CP脉冲作用后,Q0Q1的状态为()。

A. Q0Q1=11

B. Q0Q1=10

C. Q0Q1=00

D. Q0Q1=01

7、图6触发器电路中,若触发器初态为Q0=1,Q1=0,则在第3个CP脉冲作用后,Q0Q1

的状态为()。

A. Q0Q1=11

B. Q0Q1=10

C. Q0Q1=00

D. Q0Q1=01

8、图8触发器电路中,触发器初态Q1Q2=00,则第2个CP脉冲作用后,Q1Q2状态为()。

A. Q1Q2=11

B. Q1Q2=00

C. Q1Q2=10

D. Q1Q2=01

9、图9为CC4027型集成触发器的外引线排列图,从中可看出,该集成触发器含有()。

A.3个JK触发器

B. 2个D触发器

C.2个JK触发器 C. 4个D触发器

10、在上图9所示集成触发器,各触发器CP脉冲触发电压是()。

A. 低电平触发有效

B. 高电平触发有效

C. 高或低电平触发均有效

D. 无法判断

11、在上图9所示集成触发器的类型和电路电源电压是()。

A. TTL电路,+5

B. CMOS电路,+3~+18V

C. TTL电路,+3~18V

D. CMOS电路,1.5V

12、在上图9集成触发器中,各触发器置位端输入是()。

A. 低电平有效

B. 高电平有效

C. 无法判断

D. 高、低均有效

13、在上图9集成触发器,若将5 , 6 , 10 , 11 , 16脚外接电源+V DD;1脚与13脚连接;各

触发器置0后,将4 , 7 , 8 , 9 , 12脚接地。

若从3脚输入频率为160KH Z的脉冲信号,则15脚输出信号的频率为()。

A. 320 KH Z

B. 80 KH Z

C. 40KH Z

D. 20 KH Z

R=0,14、图14电路为CT74LS74型集成触发器某些逻辑功能的测试电路,当逻辑开关使1D

S=1时,在正常情况下,则无论3脚和2脚状态如何变化,显示器显示的逻辑电平1D

为( )。

A. 0

B. 1

C. 0和1依次出现

15、图15电路为CTT74LS112集成触发器某些逻辑功能的测试电路。

在每次测试前,触发

器先置0,当逻辑开关使得2,3脚逻辑电平均为1时,当按“0 ~ 1”按钮产生一个0→1脉冲时,正常情况下,“0 ~ 1”显示器显示的逻辑电平为( )。

A. 0

B. 1

C. 0与1依次出现

四、分析及画图(波形)

1、什么是同步式触发器的空翻现象?造成空翻的原因什么? (P102)

答:正常情况下,应来一个脉冲,触发器只翻转一次,若翻转多次,则为空翻现象,原因是CP=1的时间过长(﹥3t pd)。

2、JK型触发器有哪几种逻辑功能?并请根据其真值表推出其特性方程。

(P101)

3、下图所示各电路,初态为0,画出在时钟作用下Q端输出波形。

4、设主从T触发器初态Q=0,在下图所示波形作用下,画出Q的波形。

5、下图所示电路为一个双相时钟发生器。

试画出在输入时钟脉冲CP作用下的双相输出时

钟U01和U02波形

6、下图所示电路中,若CP脉冲频率为24MHz,则Q2端输出信号频率为多少?画出Q1、

Q2端波形?设触发器初态均为0。