4、《数字电子技术》黄瑞祥第四章习题答案.doc

- 格式:doc

- 大小:8.43 MB

- 文档页数:20

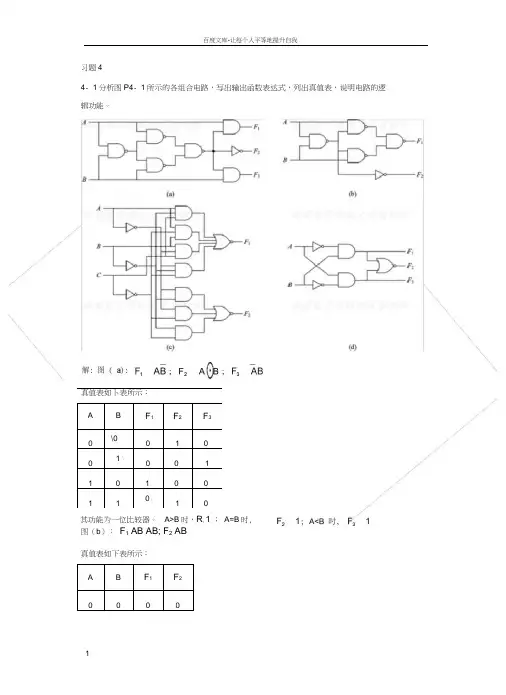

习题44- 1分析图P4- 1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻 辑功能。

图(b ): F 1 AB AB; F 2 AB 真值表如下表所示: ABF 1F 20 00 0真值表如卜表所示: AB F 1F 2F 30 \0 0 1 0 0 1 \ 0 0 1 10 1 0 0 110、1其功能为一位比较器。

A>B 时,R , 1 ; A=B 时,功能:一位半加器,1为本位和,F2为进位。

图(c):F i M (0,3,5,6) m(1,2,4,7)F2M(0,1,2,4) m(3,5,6,7)功能:一位全加器,F1为本位和,F2为本位向高位的进位。

图(d):F1AB;F2 A0B ;F3AB功能:为一位比较器,A<B时,F1= 1 ; A=B时,F2= 1; A>B时,F3= 14-2分析图P4- 2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

昇0解:该电路的输出逻辑函数表达式为:F A A J X。

AA)X i AA g X? A1A0X3因此该电路是一个四选一数据选择器,其真值表如下表所示:A、A o F0\ 0X001\X110\ X211X3 \4-3图P4- 3是一个受M控制的代码转换电路,当M = 1时,完成4为二进制码至格雷码的转换;当M = 0时,完成4为格雷码至二进制的转换。

试分别写出Y0,Y ,Y2,Y3的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

X3X2X1X0Y3Y2丫1丫0M=100000000000100010010001100110010 01000110 / 0 \10101110110010 /10110011/0M=010 \00111110\o11110101 \0/1100101\ 1 /110111001000Y J X 3Y 由此可得:当M 1时,2X 3 X2 / Y X 2 X /丫°X 1 X完成二进制至格雷码的转换。

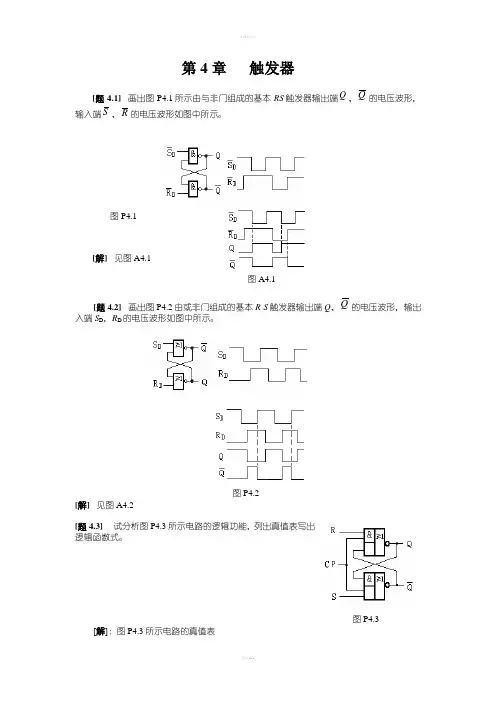

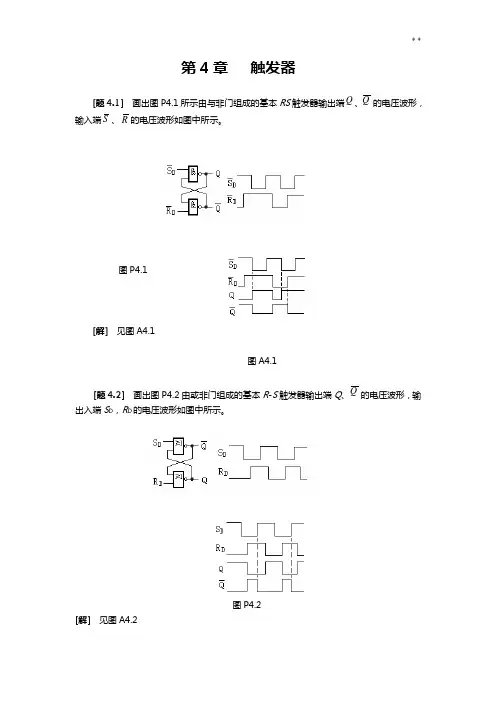

第4章触发器[题4.1]画出图P4.1所示由与非门组成的基本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的基本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3]试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3 [解]:图P4.3所示电路的真值表S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解] 见图A4.4图A4.4[题4.5] 在图P4.5电路中,若CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图P4.5[解]见图A4.5图A4.5[题4.6]若将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP信号作用下Q和Q端的电压波形。

己知CP信号的宽度tw= 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]若主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7R各输入端的电压波形如图P4.8所示,[题4.8]若主从结构RS触发器的CP、S、R、D1S。

试画出Q、Q端对应的电压波形。

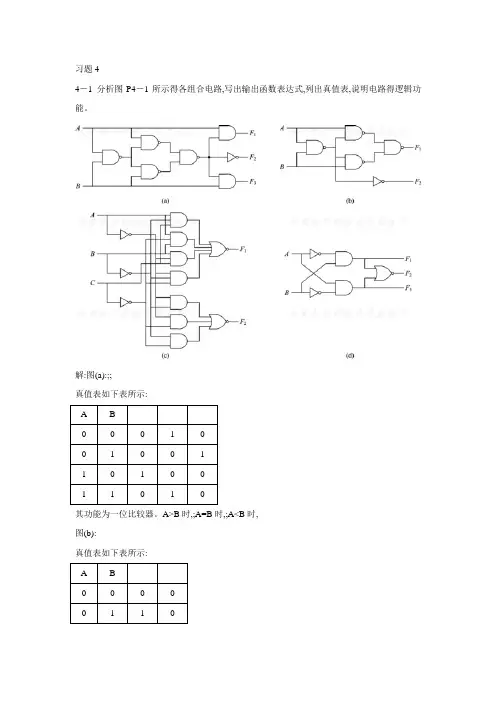

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:A B0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 0其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:A B0 0 0 00 1 1 0功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:0 00 11 01 14-3 图P4-3就是一个受M控制得代码转换电路,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:M=1 0 0 0 0 0 0 0 00 0 0 1 0 0 0 10 0 1 0 0 0 1 10 0 1 1 0 0 1 00 1 0 0 0 1 1 00 1 0 1 0 1 1 10 1 1 0 0 1 0 10 1 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 11 0 0 1 1 1 1 01 0 1 0 1 1 0 01 0 1 1 1 1 0 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 0 1 0 1 11 1 1 1 1 0 1 0由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

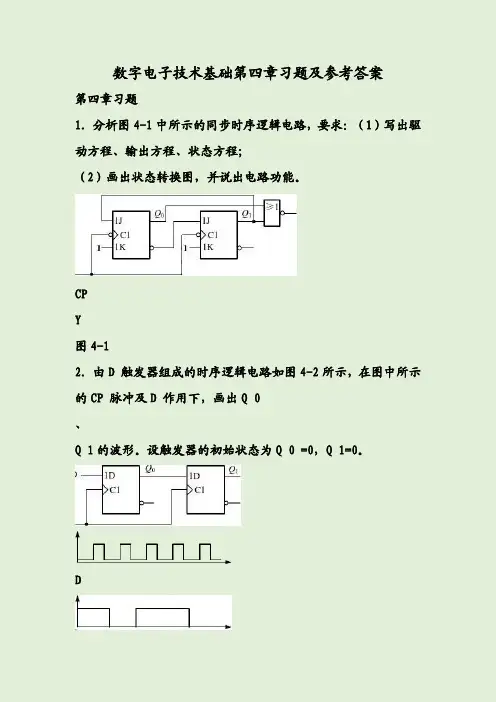

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

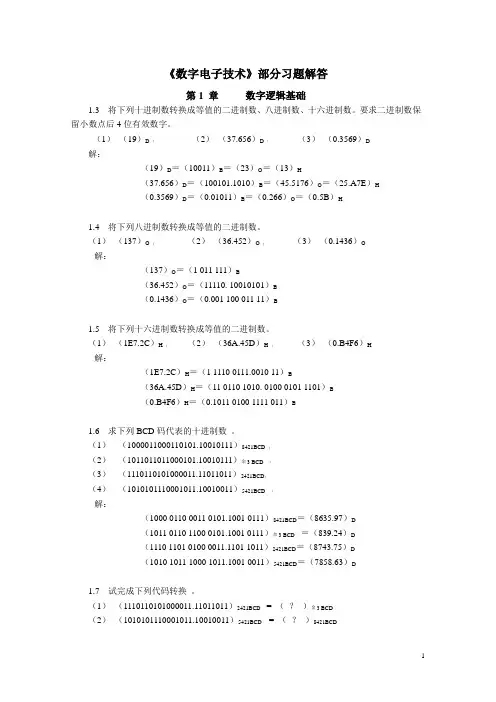

《数字电子技术》部分习题解答第1 章数字逻辑基础1.3 将下列十进制数转换成等值的二进制数、八进制数、十六进制数。

要求二进制数保留小数点后4位有效数字。

(1)(19)D ;(2)(37.656)D ;(3)(0.3569)D解:(19)D=(10011)B=(23)O=(13)H(37.656)D=(100101.1010)B=(45.5176)O=(25.A7E)H(0.3569)D=(0.01011)B=(0.266)O=(0.5B)H1.4 将下列八进制数转换成等值的二进制数。

(1)(137)O ;(2)(36.452)O ;(3)(0.1436)O解:(137)O=(1 011 111)B(36.452)O=(11110. 10010101)B(0.1436)O=(0.001 100 011 11)B1.5 将下列十六进制数转换成等值的二进制数。

(1)(1E7.2C)H ;(2)(36A.45D)H ;(3)(0.B4F6)H解:(1E7.2C)H=(1 1110 0111.0010 11)B(36A.45D)H=(11 0110 1010. 0100 0101 1101)B(0.B4F6)H=(0.1011 0100 1111 011)B1.6 求下列BCD码代表的十进制数。

(1)(1000011000110101.10010111)8421BCD ;(2)(1011011011000101.10010111)余3 BCD ;(3)(1110110101000011.11011011)2421BCD;(4)(1010101110001011.10010011)5421BCD ;解:(1000 0110 0011 0101.1001 0111)8421BCD=(8635.97)D(1011 0110 1100 0101.1001 0111)余3 BCD =(839.24)D(1110 1101 0100 0011.1101 1011)2421BCD=(8743.75)D(1010 1011 1000 1011.1001 0011)5421BCD=(7858.63)D1.7 试完成下列代码转换。

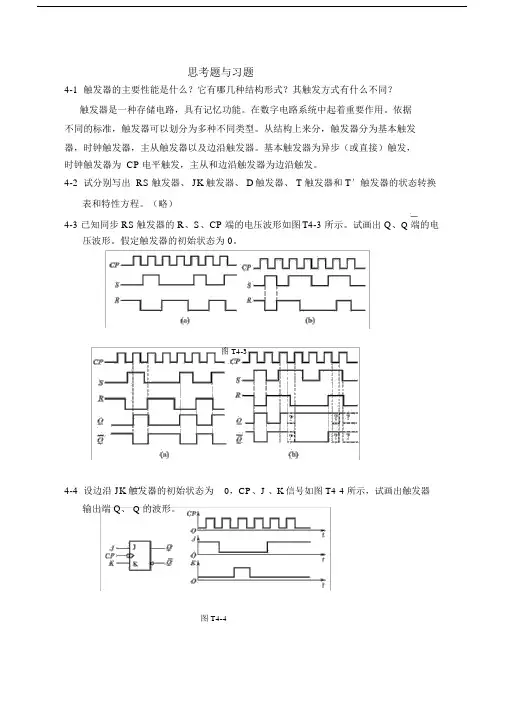

思考题与习题4-1 触发器的主要性能是什么?它有哪几种结构形式?其触发方式有什么不同?触发器是一种存储电路,具有记忆功能。

在数字电路系统中起着重要作用。

依据不同的标准,触发器可以划分为多种不同类型。

从结构上来分,触发器分为基本触发器,时钟触发器,主从触发器以及边沿触发器。

基本触发器为异步(或直接)触发,时钟触发器为 CP电平触发,主从和边沿触发器为边沿触发。

4-2 试分别写出 RS触发器、 JK 触发器、 D触发器、 T 触发器和 T′触发器的状态转换表和特性方程。

(略)4-3 已知同步 RS触发器的 R、S、CP端的电压波形如图T4-3 所示。

试画出 Q、Q端的电压波形。

假定触发器的初始状态为 0。

图 T4-34-4 设边沿 JK 触发器的初始状态为0,CP、J 、K 信号如图 T4-4 所示,试画出触发器输出端 Q、Q的波形。

图 T4-414-5 电路如图 T4-5(a) 所示,输入波形如图 T4-5(b) 所示,试画出该电路输出端G 的波形,设触发器的初始状态为0。

图 T5-24-6 试画出图 T4-6 所示波形加在以下两种触发器上时,触发器输出Q的波形:(1)下降沿触发的触发器(2)上升沿触发的触发器图 T4-64-7 已知 A、B 为输入信号,试写出图T4-7 所示各触发器的次态逻辑表达式。

2图 T4-7Q n 1D A B( a )n 1Q( b )J Q n KQ nAQ n BQ n Q nAQ n BQ n Q nB Q n B Q n4-8 设图 T4-8 所示中各 TTL 触发器的初始状态皆为0,试画出在 CP信号作用下各触发的输出端 Q1- Q6的波形。

图 T4-84-9 试对应画出图T4-9 所示电路中 Q1、 Q2波形。

(初始状态均为0)3图 T4-94-10一逻辑电路如图T4-10 所示,试画出在CP作用下 Y0、Y1、Y 2、Y 3的波形。

(CT74LS139为 2 线— 4 线译码器。

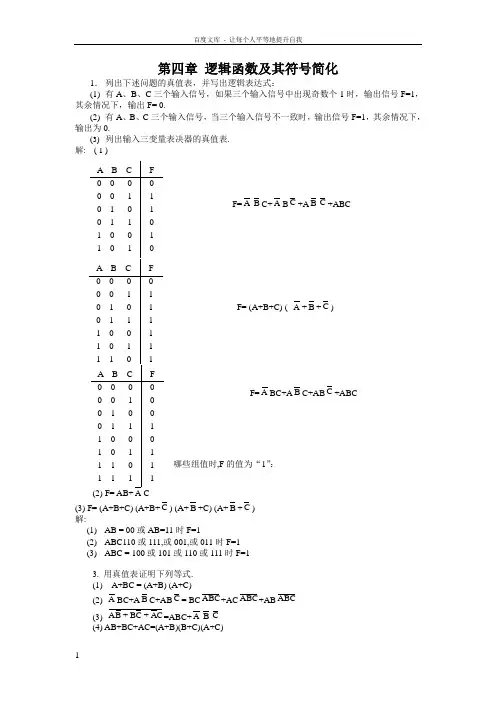

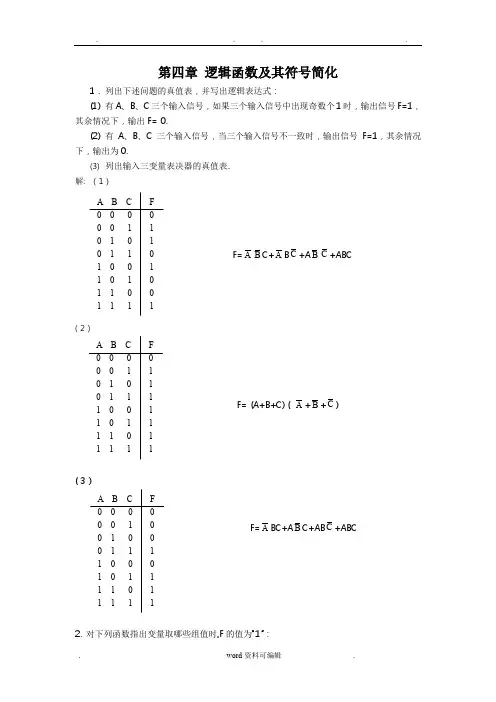

第四章逻辑函数及其符号简化1.列出下述问题的真值表,并写出逻辑表达式:(1)有A、B、C三个输入信号,如果三个输入信号中出现奇数个1时,输出信号F=1,其余情况下,输出F= 0.(2)有A、B、C三个输入信号,当三个输入信号不一致时,输出信号F=1,其余情况下,输出为0.(3)列出输入三变量表决器的真值表.解: ( 1 )F=A B C+A B C+A B C+ABC( 2 )F= (A+B+C) ( A+B+C)( 3 )F=A BC+A B C+AB C+ABC2. 对下列函数指出变量取哪些组值时,F的值为“1”:(1) F= AB+A B (2) F= AB+A C(3) F= (A+B+C) (A+B+C ) (A+B +C) (A+B +C ) 解:(1) AB = 00或AB=11时F=1(2) ABC110或111,或001,或011时F=1 (3) ABC = 100或101或110或111时F=13. 用真值表证明下列等式. (1) A+BC = (A+B) (A+C)(2) A BC+A B C+AB C = BC ABC +AC ABC +AB ABC (3) C A +C B +B A =ABC+A B C (4) AB+BC+AC=(A+B)(B+C)(A+C) (5) ABC+A +B +C =1 证: ( 1 ) ( 2 )( 3 )( 4 ) ( 5 )4. 直接写出下列函数的对偶式F ′及反演式F 的函数表达式. (1) F= [A B (C+D)][B C D +B (C +D)] (2) F= A BC + (A +B C ) (A+C) (3) F= AB+CD +E +D +E C +D +BC (4) F=D +B A •B A +C 解:(1) F`= [A +B+CD]+[(B+C +D )(•B+C D]]F = [A+B +C D ]+[(B +C+D)(•B +C D ]](2) F`= (A+C +B )]AC )C +B (•A [•F = (A +C +B )]C A +)C +B (•A [•(3) F`=)B +A (•C +D •)B +A (F =)B +A (•C +D •)B +A (5. 若已知x+y = x+z ,问y = z 吗?为什么? 解:y 不一定等于z,因为若x=1时,若y=0,z=1,或y=1,z=0,则x+y = x+z = 1,逻辑或的特点,有一个为1则为1。

习题答案第一章数制和码制1.数字信号和模拟信号各有什么特点?答:模拟信号——量值的大小随时间变化是连续的。

数字信号——量值的大小随时间变化是离散的、突变的(存在一个最小数量单位△)。

2.在数字系统中为什么要采用二进制?它有何优点?答:简单、状态数少,可以用二极管、三极管的开关状态来对应二进制的两个数。

3.二进制:0、1;四进制:0、1、2、3;八进制:0、1、2、3、4、5、6、7;十六进制:0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F。

4.(30.25)10=( 11110.01)2=( 1E.4)16。

(3AB6)16=( 0011101010110110)2=(35266)8。

(136.27)10=( 10001000.0100)2=( 88.4)16。

5. B E6.ABCD7.(432.B7)16=( 010*********. 10110111)2=(2062. 556)8。

8.二进制数的1和0代表一个事物的两种不同逻辑状态。

9.在二进制数的前面增加一位符号位。

符号位为0表示正数;符号位为1表示负数。

这种表示法称为原码。

10.正数的反码与原码相同,负数的反码即为它的正数原码连同符号位按位取反。

11.正数的补码与原码相同,负数的补码即为它的反码在最低位加1形成。

12.在二进制数的前面增加一位符号位。

符号位为0表示正数;符号位为1表示负数。

正数的反码、补码与原码相同,负数的反码即为它的正数原码连同符号位按位取反。

负数的补码即为它的反码在最低位加1形成。

补码再补是原码。

13.A:(+1011)2的反码、补码与原码均相同:01011;B: (-1101)2的原码为11101,反码为10010,补码为10011.14.A: (111011)2 的符号位为1,该数为负数,反码为100100,补码为100101. B: (001010)2的符号位为0,该数为正,故反码、补码与原码均相同:001010.15.两个用补码表示的二进制数相加时,和的符号位是将两个加数的符号位和来自最高有效数字位的进位相加,舍弃产生的进位得到的结果就是和的符号。

第4章触发器[题4.1]画出图P4.1所示由与非门组成的基本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的基本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3] 试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3[解]S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解]见图A4.4图A4.4[题4.5]在图P4.5电路中,若CP、S、R的电压波形如图中所示,试画出Q和Q端与之对应的电压波形。

假定触发器的初始状态为Q=0。

图P4.5[解]见图A4.5图A4.5[题4.6]若将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]若主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q 端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]若主从结构RS触发器的CP、S、R、D R各输入端的电压波形如图P4.8所S。

试画出Q、Q端对应的电压波形。

示,1D图P4.8[解] 见图A4.8图A4.8[题4.9]已知主从结构JK触发器输入端J、K和CP的电压波形如图P4.9所示,试画出Q、Q端对应的电压波形。

第4章习题解答4-1 写出图T4-1电路的输出函数式,证明a 、b 有相同的逻辑功能。

B(a)A(b)BA 图T4-1 习题4-1的图解4-1 Y 1= A B ' +A ' B ' ; Y 2=( A+B)(A ' +B ' )= AB ' +A ' B ' =Y 14-2 试写出图T4-2所示逻辑电路的输出函数式并化简,指出电路的逻辑功能。

A BMBA图T4-2习题4-2的图图T4-3习题4-3的图解4-2 由图T4-2写电路的输出函数式并化简得AB B A B A AB Y +''='''''=))()(( (JT4-2)由JT4-2式可知,电路实现的是二变量同或功能。

4-3 图T4-3是一个选通电路。

M 为控制信号,通过M 电平的高低来选择让A 还是让B 从输出端送出。

试写逻辑电路的输出函数式并化简,分析电路能否实现上述要求。

解4-3 由图T4-3写电路的输出函数式并化简得M B AM M B M A Y '+='''=)((( (JT4-3)由JT4-3式可知,电路能够实现选通要求,当M=1时,Y=A ;当M=0时,Y=B 。

4-4.用与非门设计一个四人表决逻辑电路,结果按“少数服从多数”的原则决定。

解4-4(1)列真值表设四个人的意见为变量A 、B 、C 、D ,表决结果为函数Y 。

按正逻辑给变量赋值:同意为“1”,不同意为“0”;提案通过为“1”,没通过为“0”,所列真值表如表JT4-4所示。

表JT4-4输 入输 出A B C D 0 0 0 0 0 00 0 0 1 0 1 0 1 0 10 0 0 1 1 0 1 1 0 0 0 1 1 01 1 Y000000001 0 1 0 1 0 1 01 1 1 1 1 11 1 0 0 0 1 1 0 1 1 0 00 1 1 0 1 100000000输 入输 出A B C D Y(2)写输出逻辑函数式由表JT4-4可写输出逻辑函数式ABCD D ABC D C AB CD B A BCD A Y +'+'+'+'= (JT4-4a)(3)化简填卡诺图,如图JT 4-4(a)所示合并最小项,得最简与—或式BCD ACD ABD ABC Y +++= (JT4-4b)(4)画逻辑电路图将式JT4-4(b)转换成与非—与非式)()()()(('''''=D BC ACD ABD ABC Y (JT4-4c)按式JT4-4(c)用与非门画逻辑电路图,如图JT4-4(b)所示。