优先编码器74LS148的应用

- 格式:pdf

- 大小:108.54 KB

- 文档页数:1

74ls148管脚图引脚功能表真值表逻辑图扩展资料有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉使能端OE(芯片是否启用)的逻辑方程:OE =I0·I1·I2·I3·I4·I5·I6·I7·IE当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。

当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。

输入输出EI I0I1I2I3I4I5I6I7A2A1AGSEO1x x x x x x x x11111 01111111111110 0x x x x x x x000001 0x x x x x x0100110 0x x x x x01101010 0x x x x011101110 0x x x0111110010 0x x01111110110 0x011111111010 00111111111110<优先编码器74ls148功能表>从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I 6,…,I0 。

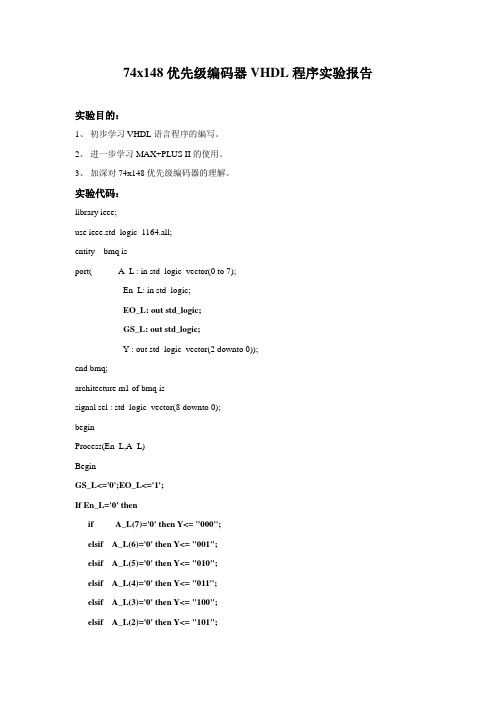

74x148优先级编码器VHDL程序实验报告实验目的:1、初步学习VHDL语言程序的编写。

2、进一步学习MAX+PLUS II的使用。

3、加深对74x148优先级编码器的理解。

实验代码:library ieee;use ieee.std_logic_1164.all;entity bmq isport( A_L : in std_logic_vector(0 to 7);En_L: in std_logic;EO_L: out std_logic;GS_L: out std_logic;Y : out std_logic_vector(2 downto 0));end bmq;architecture m1 of bmq issignal sel : std_logic_vector(8 downto 0);beginProcess(En_L,A_L)BeginGS_L<='0';EO_L<='1';If En_L='0' thenif A_L(7)='0' then Y<= "000";elsif A_L(6)='0' then Y<= "001";elsif A_L(5)='0' then Y<= "010";elsif A_L(4)='0' then Y<= "011";elsif A_L(3)='0' then Y<= "100";elsif A_L(2)='0' then Y<= "101";elsif A_L(1)='0' then Y<= "110";elsif A_L(0)='0' then Y<= "111";else Y<= "111";GS_L<='1';EO_L<='0'; end if;Else Y<= "000";GS_L<='1';EO_L<='1'; end if;end process;end m1;代码完成过程:由课件上的代码修改得来。

优先编码器设计辽宁⼯程技术⼤学数电项⽬设计题⽬74LS148编码器设计指导教师院(系、部)电⽓与控制⼯程学院专业班级电⽹13-1学号1305080116姓名苏⼩平⽇期2016/12/231.设计规则在优先编码器电路中,允许同时输⼊两个以上的编码信号。

不过在设计优先编码器时已经将所有的输⼊信号按照优先顺序依次排序,当⼏个输⼊信号同时出现时,只对其中优先级别最⾼的先进⾏编码。

2.设计原理编码器的逻辑功能是将输⼊的每⼀个信号编成⼀个对应的⼆进制代码。

优先编码器的特点是允许编码器同时输⼊两个以上编码信号但只对优先级别最⾼的信号进⾏编码。

8线-3线优先编码器74LS148有8个信号输⼊端输⼊端为低电平时表⽰请求编码为⾼电平时表⽰没有编码请求有3个编码输出端输出3位⼆进制代码编码器还有⼀个使能端EI当其为低电平时编码器才能正常⼯作还有两个输出端GS和E0⽤于扩展编码功能GS为0表⽰编码器处于⼯作状态且⾄少有⼀个信号请求编码E0为0表⽰编码器处于⼯作状态但没有信号请求编码。

74LS148芯⽚管脚:0-7 编码输⼊端(低电平有效) EI 选通输⼊端(低电平有效),A0、A1、A2 三位⼆进制编码输出信号即编码输出端(低电平有效),GS ⽚优先编码输出端即宽展端(低电平有效),EO 选通输出端,即使能输出端。

芯⽚管⾓使⽤⽅法:(1)0-7 EI 选通输⼊端(低电平有效)(2)编码输⼊端(低电平有效);(3)A0、A1、A2 三位⼆进制编码输出信号即编码输出端(低电平有效);(4)GS ⽚优先编码输出端即宽展端(低电平有效);(5)EO 选通输出端,即使能输出端;3.设计思路构建8-3线优先编码器的实验电路。

输⼊信号通过单⼑双掷开关接优先编码器的输⼊端开关通过键盘上的A⾄H键控制接⾼电平(VCC)或低电平(地)。

使能端通过空格键控制接⾼电平或低电平。

输出端接逻辑探测器的监测输出。

在本次优先编码器的设计规定优先级顺序,采⽤A—H之间代表输⼊,其中优先级别从A⾄H依次增⾼,进⽽H的优先级别最⾼。

编码器与译码器实验报告一、实验目的本次实验的主要目的是深入理解编码器和译码器的工作原理,通过实际操作和观察,掌握它们的功能和应用,并学会使用相关的实验设备进行电路搭建和测试。

二、实验原理(一)编码器编码器是一种将输入信号转换为特定编码输出的数字电路。

常见的编码器有二进制编码器和优先编码器。

二进制编码器将多个输入信号转换为对应的二进制编码输出。

优先编码器则在多个输入同时有效时,优先对优先级较高的输入进行编码。

(二)译码器译码器则是将输入的编码信号转换为对应的输出信号。

常见的译码器有二进制译码器和显示译码器。

二进制译码器将输入的二进制编码转换为多个输出信号,每个输出对应编码的一个可能值。

显示译码器则用于驱动数码管等显示器件,将输入的编码转换为适合显示的信号。

三、实验设备与器材本次实验使用的设备和器材包括:数字电路实验箱、74LS148 优先编码器芯片、74LS138 二进制译码器芯片、逻辑电平指示灯、导线若干。

四、实验步骤(一)74LS148 优先编码器实验1、按照实验电路图,在数字电路实验箱上正确连接 74LS148 优先编码器芯片和逻辑电平指示灯。

2、依次将输入引脚设置为不同的电平组合,观察输出引脚的编码值,并记录在实验表格中。

3、分析实验结果,验证优先编码器的工作原理和功能。

(二)74LS138 二进制译码器实验1、依照实验电路图,在数字电路实验箱上连接 74LS138 二进制译码器芯片和逻辑电平指示灯。

2、改变输入引脚的二进制编码值,观察输出引脚的电平状态,并记录下来。

3、对比理论预期结果,检验二进制译码器的正确性。

五、实验数据与结果(一)74LS148 优先编码器实验数据|输入引脚电平|输出编码值||||| I0=0, I1=0, I2=0, I3=0, I4=0, I5=0, I6=0, I7=0 | 000 || I0=1, I1=0, I2=0, I3=0, I4=0, I5=0, I6=0, I7=0 | 111 || I0=0, I1=1, I2=0, I3=0, I4=0, I5=0, I6=0, I7=0 | 110 ||||(二)74LS138 二进制译码器实验数据|输入编码值|输出引脚电平||||| 000 | Y0=1, Y1=0, Y2=0, Y3=0, Y4=0, Y5=0, Y6=0, Y7=0 || 001 | Y0=0, Y1=1, Y2=0, Y3=0, Y4=0, Y5=0, Y6=0, Y7=0 ||||六、实验结果分析(一)74LS148 优先编码器通过实验数据可以看出,当多个输入引脚同时为高电平时,编码器优先对优先级较高的输入进行编码。

编码器和译码器的应用实验报告一、实验目的本次实验的主要目的是深入了解编码器和译码器的工作原理及其在实际应用中的作用。

通过实际操作和观察,掌握编码器和译码器的逻辑功能和电路连接方法,提高对数字电路的理解和应用能力。

二、实验原理(一)编码器编码器是一种将输入的多个信号转换为特定编码输出的数字电路。

常见的编码器有二进制编码器和优先编码器。

二进制编码器将 2^n 个输入信号转换为 n 位二进制编码输出。

例如,8 线 3 线二进制编码器可以将 8 个输入信号转换为 3 位二进制编码输出。

优先编码器则在多个输入信号同时有效时,只对优先级最高的输入进行编码输出。

(二)译码器译码器是编码器的逆过程,它将输入的编码转换为对应的输出信号。

常见的译码器有二进制译码器和显示译码器。

二进制译码器将 n 位二进制输入编码转换为 2^n 个输出信号。

例如,3 线 8 线二进制译码器可以将 3 位二进制编码输入转换为 8 个输出信号。

显示译码器则专门用于驱动数码管等显示器件,将输入的编码转换为适合显示的信号。

三、实验设备与材料1、数字电路实验箱2、 74LS148 8 线 3 线优先编码器芯片3、 74LS138 3 线 8 线二进制译码器芯片4、逻辑电平指示灯5、导线若干四、实验步骤(一)8 线 3 线优先编码器实验1、按照实验箱的引脚图,将 74LS148 芯片正确插入插槽。

2、将 8 个输入引脚分别连接到逻辑电平开关,用于输入不同的电平信号。

3、将 3 个输出引脚连接到逻辑电平指示灯,观察编码输出结果。

4、依次改变输入电平状态,记录输出编码,并与理论值进行对比。

(二)3 线 8 线二进制译码器实验1、如同上述步骤,将 74LS138 芯片插入实验箱并连接好电路。

2、将 3 个输入引脚连接到逻辑电平开关,用于输入编码。

3、将 8 个输出引脚分别连接到逻辑电平指示灯。

4、改变输入编码,观察并记录输出电平状态。

五、实验结果与分析(一)8 线 3 线优先编码器实验结果表明,当多个输入信号同时有效时,优先编码器能够按照设定的优先级进行编码输出。