74ls148优先编码器

- 格式:pdf

- 大小:27.13 KB

- 文档页数:3

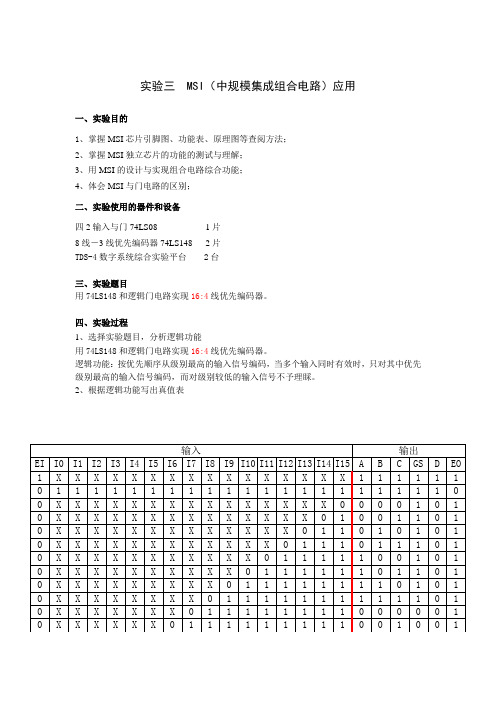

实验三 MSI(中规模集成组合电路)应用一、实验目的1、掌握MSI芯片引脚图、功能表、原理图等查阅方法;2、掌握MSI独立芯片的功能的测试与理解;3、用MSI的设计与实现组合电路综合功能;4、体会MSI与门电路的区别;二、实验使用的器件和设备四2输入与门74LS08 1片8线-3线优先编码器74LS148 2片TDS-4数字系统综合实验平台 2台三、实验题目用74LS148和逻辑门电路实现16:4线优先编码器。

四、实验过程1、选择实验题目,分析逻辑功能用74LS148和逻辑门电路实现16:4线优先编码器。

逻辑功能:按优先顺序从级别最高的输入信号编码,当多个输入同时有效时,只对其中优先级别最高的输入信号编码,而对级别较低的输入信号不予理睬。

2、根据逻辑功能写出真值表0 X X X X X 0 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 1 0 X X X X 0 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 1 0 X X X 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 1 0 X X 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 1 0 X 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 13.画出实际连线图4.连接电路,测试逻辑电路输出数据,并记录结果根据实际操作情况,实测值与理论值一致。

5.分析数据,是否实现所需的逻辑功能。

理论值与实测值一致,电路接线正确,成功实现所需逻辑功能。

五、实验体会。

74ls148管脚图引脚功能表真值表逻

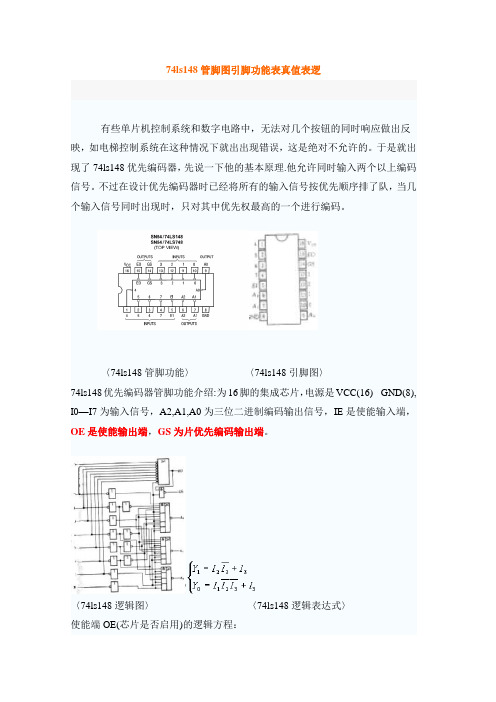

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉

74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉

使能端OE(芯片是否启用)的逻辑方程:

<74ls148真值表>

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

用两个74ls148优先编码器芯片扩展为十六线-四线优先编码器的电路连线图。

优先编码器74ls148引脚图管脚图内部功能表在优先编码器电路中,允许同时输入两个以上编码信号。

不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队。

在同时存在两个或两个以上输入信号时,优先编码器只按优先级高的输入信号编码,优先级低的信号则不起作用。

74148是一个八线-三线优先级编码器。

如图所示的是八线-三线编码器74148的惯用符号及管脚图引脚图。

74148优先编码器为16脚的集成芯片,除电源脚VC C(16)和GND(8)外,其余输入、输出脚的作用和脚号如图中所标。

其中I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE 是使能输出端,GS为片优先编码输出端。

由74148真值表可列输出逻辑方程为:A2 = (I4+I5+I6+I7)IEA1 = (I2I4I5+I3I4I5+I6+7)·IEA0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE使能输出端O E的逻辑方程为:OE =I0·I1·I2·I3·I4·I5·67·IE当使能输入I E=1时,禁止编码、输出(反码):A2,A1,A0为全1。

(如表5.1.2第一行所示。

)当使能输入I E=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。

OE为使能输出端,它只在允许编码(IE=0),而本片又没有编码输入时为0。

如表5.1.2中第二行所示)。

扩展片优先编码输出端G S的逻辑方程为:GS = (I0+I1+I2+I3+I4+I5+I6+I7)·IEGS为片优先编码输出端,它在允许编码(IE=0),且有编码输入信号时为0(如表5.1.2中第三至第十行);若允许编码而无编码输入信号时为1(如表5.1.2第二行);在不允许编码(IE=1)时,它也为1(如表5.1.2第一行)。

实验三 MSI(中规模集成组合电路)应用一、实验目的1、掌握MSI芯片引脚图、功能表、原理图等查阅方法;2、掌握MSI独立芯片的功能的测试与理解;3、用MSI的设计与实现组合电路综合功能;4、体会MSI与门电路的区别;二、实验使用的器件和设备四2输入与门74LS08 1片8线-3线优先编码器74LS148 2片TDS-4数字系统综合实验平台 2台三、实验题目用74LS148和逻辑门电路实现16:4线优先编码器。

四、实验过程1、选择实验题目,分析逻辑功能用74LS148和逻辑门电路实现16:4线优先编码器。

逻辑功能:按优先顺序从级别最高的输入信号编码,当多个输入同时有效时,只对其中优先级别最高的输入信号编码,而对级别较低的输入信号不予理睬。

2、根据逻辑功能写出真值表输入输出EI I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 I14 I15 A B C GS D EO 1 X X X X X X X X X X X X X X X X 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 X X X X X X X X X X X X X X X 0 0 0 0 1 0 1 0 X X X X X X X X X X X X X X 0 1 0 0 1 1 0 1 0 X X X X X X X X X X X X X 0 1 1 0 1 0 1 0 1 0 X X X X X X X X X X X X 0 1 1 1 0 1 1 1 0 1 0 X X X X X X X X X X X 0 1 1 1 1 1 0 0 1 0 1 0 X X X X X X X X X X 0 1 1 1 1 1 1 0 1 1 0 1 0 X X X X X X X X X 0 1 1 1 1 1 1 1 1 0 1 0 1 0 X X X X X X X X 0 1 1 1 1 1 1 1 1 1 1 1 0 1 0 X X X X X X X 0 1 1 1 1 1 1 1 1 0 0 0 0 0 1 0 X X X X X X 0 1 1 1 1 1 1 1 1 1 0 0 1 0 0 13.画出实际连线图4.连接电路,测试逻辑电路输出数据,并记录结果 根据实际操作情况,实测值与理论值一致。

Verilog⼋线-三线优先编码器设计(74LS148)if语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83 (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平26else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; end27else if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; end28else if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; end29else if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; end30else if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; end31else if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; end32else if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; end33else if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; end34else if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end//芯⽚⼯作,但⽆编码输⼊35else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)36endmodule3738//EI = 0 表⽰允许编码,否则所有输出端被封锁在⾼电平(控制芯⽚⼯作)39//EO = 0 表⽰电路⼯作,但⽆编码输⼊(⽤于级联)40//GS = 0 表⽰电路⼯作,且有编码输⼊(判断输⼊端是否有输⼊)testbench:1 `timescale 1 ps/ 1 ps2module encoder_83_vlg_tst();3reg EI;4reg [7:0] din;5wire EO;6wire GS;7wire [2:0] dout;8 encoder_83 i1 (.EI(EI), .EO(EO), .GS(GS), .din(din), .dout(dout));9initial10begin11 EI = 1;12 din = 8'b11111111;13 #10 EI = 0;14 #10 din = 8'b01010101;15 #10 din = 8'b10101010;16 #10 din = 8'b11010101;17 #10 din = 8'b11101010;18 #10 din = 8'b11110101;19 #10 din = 8'b11111010;20 #10 din = 8'b11111101;21 #10 din = 8'b11111110;22 #10 din = 8'b11111111;23end24endmoduleView Codecase语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83_case (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI)26begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平27else28casez (din) //建议⽤casez语句,casez把z/?匹配成任意。

74ls148管脚图引脚功能表真值表逻辑图扩展资料

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉

74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉

使能端OE(芯片是否启用)的逻辑方程:

<74ls148真值表>

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

用两个74ls148优先编码器芯片扩展为十六线-四线优先编码器的电路连线图。

优先编码器设计辽宁⼯程技术⼤学数电项⽬设计题⽬74LS148编码器设计指导教师院(系、部)电⽓与控制⼯程学院专业班级电⽹13-1学号1305080116姓名苏⼩平⽇期2016/12/231.设计规则在优先编码器电路中,允许同时输⼊两个以上的编码信号。

不过在设计优先编码器时已经将所有的输⼊信号按照优先顺序依次排序,当⼏个输⼊信号同时出现时,只对其中优先级别最⾼的先进⾏编码。

2.设计原理编码器的逻辑功能是将输⼊的每⼀个信号编成⼀个对应的⼆进制代码。

优先编码器的特点是允许编码器同时输⼊两个以上编码信号但只对优先级别最⾼的信号进⾏编码。

8线-3线优先编码器74LS148有8个信号输⼊端输⼊端为低电平时表⽰请求编码为⾼电平时表⽰没有编码请求有3个编码输出端输出3位⼆进制代码编码器还有⼀个使能端EI当其为低电平时编码器才能正常⼯作还有两个输出端GS和E0⽤于扩展编码功能GS为0表⽰编码器处于⼯作状态且⾄少有⼀个信号请求编码E0为0表⽰编码器处于⼯作状态但没有信号请求编码。

74LS148芯⽚管脚:0-7 编码输⼊端(低电平有效) EI 选通输⼊端(低电平有效),A0、A1、A2 三位⼆进制编码输出信号即编码输出端(低电平有效),GS ⽚优先编码输出端即宽展端(低电平有效),EO 选通输出端,即使能输出端。

芯⽚管⾓使⽤⽅法:(1)0-7 EI 选通输⼊端(低电平有效)(2)编码输⼊端(低电平有效);(3)A0、A1、A2 三位⼆进制编码输出信号即编码输出端(低电平有效);(4)GS ⽚优先编码输出端即宽展端(低电平有效);(5)EO 选通输出端,即使能输出端;3.设计思路构建8-3线优先编码器的实验电路。

输⼊信号通过单⼑双掷开关接优先编码器的输⼊端开关通过键盘上的A⾄H键控制接⾼电平(VCC)或低电平(地)。

使能端通过空格键控制接⾼电平或低电平。

输出端接逻辑探测器的监测输出。

在本次优先编码器的设计规定优先级顺序,采⽤A—H之间代表输⼊,其中优先级别从A⾄H依次增⾼,进⽽H的优先级别最⾼。

74LS148优先编码器1.编码的概念下图是医院病房中常见的一种请求显示电路n个开关K1K2┈K n接至n张病床n个指示灯接至护士办公室病员可以通过按动开关呼叫护士(因疼痛或树叶即将结束等原因),某一开关一旦合上,相应的安装在护士办公室的指示灯亮,护士马上就会过来处理。

该电路的优点是简单、可靠,缺点是用线太多。

如某病区有200张病床,那就会有200根线接到护士办公室。

用编码的办法就可大大减少用线的根数。

下图是由四个与非门,15个开关组成的16-4线编码带电路。

如果加一个与非门可得到32-5线编码电路。

当15个开关全部断开时,四个与非门的输入为全为1,当仅有闭合时当仅有闭合时当仅有闭合时该电路的主要缺点是:任何时候只允许一个开关合上,才能得到正确的编码,如果两个或更多的开关合上,如和合上与单独合上时得到同一个0011的编码。

所以上图电路没有实用价值。

2.优先的概念例:某医院有、、、号病室四间,是重症监护病房需特别护理,其余依次为重点病房、普通护理病房和康复护理病房,设计一个优先请求显示电路,其优先级别依次为最高、次高、较低和最低。

在四个病房各安一个开关、、、,0表示有请求,1表示没有请求;在护士病房安四个指示灯,1表示灯亮,0表示灯暗。

当时(),亮(),其余三个灯暗,无论这三个病房有无请求。

当无请求时(),如果则才会亮,此时都不会亮列出真值表如下:该真值表只有五行,是一个简化的真值表,其实四变量真值表从0000到1111应该有16行。

表中第2行其实包含8行,这8行其余三个变量从000、001111即0000、00010111(这八行最小项之和为)从简化的真值表上我们直接写出读者可自行列出完整的真值表(16行)并写出的最简与或表达式,看与上述表达式是否一致。

实现上述逻辑功能的逻辑图如下:3. 74LS148优先编码器在优先编码器电路中,允许同时输入两个以上的编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

优先级编码器74LS148的电路结构、工作原理及使用方法在实际生活中经常会遇到同时输入两个或两个以上编码信号的情况。

例如,同时按下计算机键盘上的两个按键。

如果计算机键盘内的编码器是前面所讲的普通编码器,当同时按下两个按键时,键盘内的编码器将不能对这种输入状态进行编码,会出现错误的信息。

这种错误信息有时会出现致命的后果。

为了使这种输入状态出现时编码企业有确定的输出信号输出,便出现了优先编码器。

优先编码器允许同时输入两个以上的编码信号,编码器对所有输入的信号规定了优先顺序,当多个输入信号同时出现时,只对其中优先级最高的一个进行编码。

74LS148是集成8-3线优先编码器产品,下面对该优先级编码器的电路结构、工作原理及使用方法进行介绍。

图1给出了8-3线优先编码器74LS148的逻辑图。

图 1 8.3线优先编码器74LS148的逻辑图根据逻辑电路可以写出输出与输入变量之间的逻辑函数式为(1)从式(1)可以看出,当=1时,编码输出端、、均被锁定在高电平状态,只有在=0的条件下,编码器才能正常工作。

故为控制端,又称选通输入端,且为低电平有效。

根据式(1)可以列出优先那编码器74LS148的逻辑功能,如表1所示。

表1 74LS148逻辑功能表输入输出I0I1I2I3I4I5I6I7Y2Y1Y01××××××××10111011111111101010×××××××0000100××××××01001100×××××011110100××××0111111100×××01111010100××011111011100×01111111001000111111110110在表1中,符号“×”表示任意状态(0或1,即输入端有无信号)。

实验六编码、译码显示电路一、实验目的1.熟悉七段发光二极管显示器的结构及工作原理。

2.掌握分段式显示译码电路的设计方法及调试方法。

3.掌握编码器的逻辑功能及其应用。

4.掌握中规模显示译码器74LS48和优先编码器74LS148的功能和使用方法。

二、手动实验预习要求及思考题1.复习8/3线优先编码器74LS148的工作原理及逻辑功能。

2.复习中规模译码器74LS48的工作原理及逻辑功能。

3.用发光二极管组成的七段显示器按结构分为共阴极和共阳极两种,中规模译码器74LS48应采用哪种结构形式?为什么?4.译码电路输出与笔画段之间是否要加限流电阻器。

5.设计一个能显示0、一、二、三,四个字形的译码逻辑电路,输入两变量A、B。

三、仿真实验要求采用EWB或者PSpice软件仿真电路,以便将仿真结果与实验结果进行比较。

四、实验仪器及器件1.TTL集成芯片若干2.万用表一块3.电子学综合实验装置一台五、实验内容与步骤1.七段显示译码器的设计和调试选用共阴极数码管、与非门74LS00、反相器74LS04和510Ω限流电阻,根据预习中设计出的能显示0、一、二、三,四个字形的译码逻辑电路连好,调试电路,到数码管能显示0、一、二、三,四个字形为止。

要求写出设计过程,列出真值表,写出逻辑表达式,画出逻辑图。

选做:设计一个译码器,输入为两个变量,输出能显示出数字0~9和字母AbCdEFHP 中任四个字形。

2.测试74LS48译码逻辑功能74LS48的各管脚的功能为:(1)试灯输入:当将LT置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。

(2)灭灯输入:当将BI置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。

(3)灭零输入:在A、B、C、D均为低电平时,把_____RBI端分别接高电平、低电平,观察数码管显示情况。

(4)动态灭灯:按图1接好电路,在A 、B 、C 、D 均为低电平时,观察数码管显示情况。

实验六编码、译码显示电路

一、实验目的

1.熟悉七段发光二极管显示器的结构及工作原理。

2.掌握分段式显示译码电路的设计方法及调试方法。

3.掌握编码器的逻辑功能及其应用。

4.掌握中规模显示译码器74LS48和优先编码器74LS148的功能和使用方法。

二、手动实验预习要求及思考题

1.复习8/3线优先编码器74LS148的工作原理及逻辑功能。

2.复习中规模译码器74LS48的工作原理及逻辑功能。

3.用发光二极管组成的七段显示器按结构分为共阴极和共阳极两种,中规模译码器74LS48应采用哪种结构形式?为什么?

4.译码电路输出与笔画段之间是否要加限流电阻器。

5.设计一个能显示0、一、二、三,四个字形的译码逻辑电路,输入两变量A、B。

三、仿真实验要求

采用EWB或者PSpice软件仿真电路,以便将仿真结果与实验结果进行比较。

四、实验仪器及器件

1.TTL集成芯片若干

2.万用表一块

3.电子学综合实验装置一台

五、实验内容与步骤

1.七段显示译码器的设计和调试

选用共阴极数码管、与非门74LS00、反相器74LS04和510Ω限流电阻,根据预习中设计出的能显示0、一、二、三,四个字形的译码逻辑电路连好,调试电路,到数码管能显示0、一、二、三,四个字形为止。

要求写出设计过程,列出真值表,写出逻辑表达式,画出逻辑图。

选做:设计一个译码器,输入为两个变量,输出能显示出数字0~9和字母AbCdEFHP 中任四个字形。

2.测试74LS48译码逻辑功能

74LS48的各管脚的功能为:

(1)试灯输入:当将LT置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。

(2)灭灯输入:当将BI置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。

(3)灭零输入:在A、B、C、D均为低电平时,把_____

RBI端分别接高电平、低电平,观

察数码管显示情况。

(4)动态灭灯:按图1接好电路,在A 、B 、C 、D 均为低电平时,观察数码管显示情况。

(5)当LT =1,BI =1时,由输入端A 、B 、C 、D 送入二进制码,记下显示器的对应字形填入表1中。

表1

十进制 输入二进制码DCBA 显示字形

0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1 10 1 0 1 0 11 1 0 1 1 12 1 1 0 0 13 1 1 0 1 14 1 1 1 0 15

1 1 1 1

3.测试8/3线优先编码器74LS148的逻辑功能

74LS148是典型的8/3线优先编码器,它的管脚见图2,测试它的逻辑真值表。

从而了解优先编码器的正确使用。

I 4I 5I 6I 7Y 1Y 2E i GND

图2 74LS148

的管脚图 图 1 动态灭灯电路图

1.设计

对74LS138译码器的功能进行测试,并用两片74LS 138组成4-16译码器。

要求画出逻辑图,连好电路,测试并填好逻辑状态表。

六、实验报告

1.将测试的内容填入表格。

2.写出设计过程,画出设计的逻辑图,并将测试结果填入逻辑状态表中。

3. 交仿真报告(包括仿真电路、设计过程、仿真结果、数据分析)。