74ls148管脚图引脚功能表真值表逻辑图扩展·优选.

- 格式:doc

- 大小:108.00 KB

- 文档页数:3

优先编码器74LS148有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

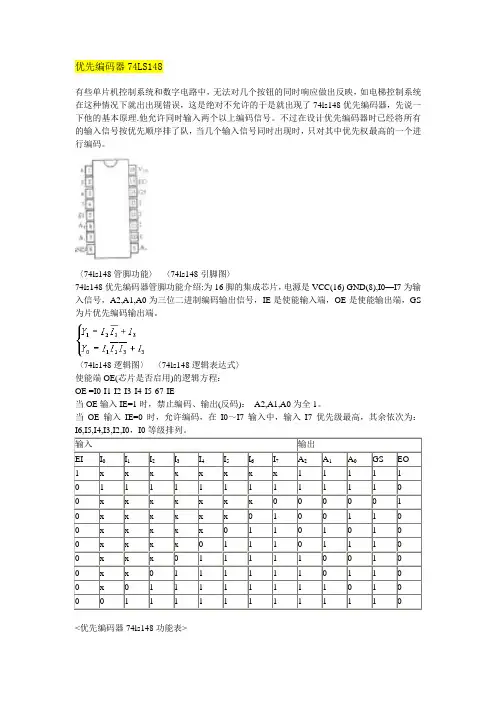

〈74ls148管脚功能〉〈74ls148引脚图〉74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8),I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS 为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉使能端OE(芯片是否启用)的逻辑方程:OE =I0·I1·I2·I3·I4·I5·67·IE当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。

当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。

输入输出EI I0I1I2I3I4I5I6I7A2A1A0GS EO1 x x x x x x x x 1 1 1 1 10 1 1 1 1 1 1 1 1 1 1 1 1 00 x x x x x x x 0 0 0 0 0 10 x x x x x x 0 1 0 0 1 1 00 x x x x x 0 1 1 0 1 0 1 00 x x x x 0 1 1 1 0 1 1 1 00 x x x 0 1 1 1 1 1 0 0 1 00 x x 0 1 1 1 1 1 1 0 1 1 00 x 0 1 1 1 1 1 1 1 1 0 1 00 0 1 1 1 1 1 1 1 1 1 1 1 0<优先编码器74ls148功能表>从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I6,…,I0 。

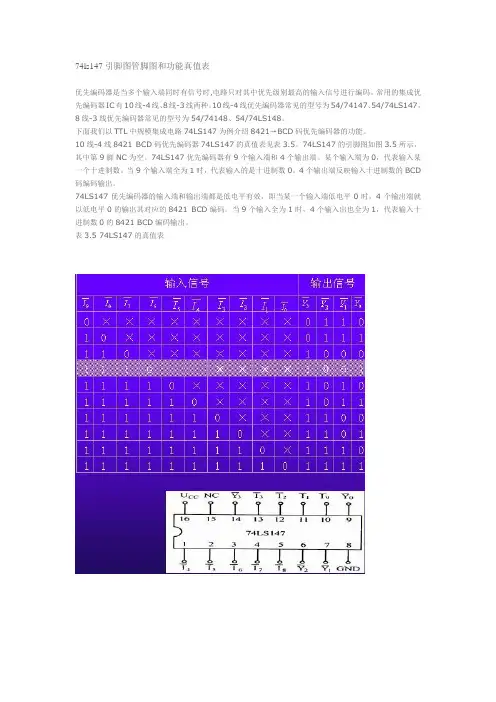

74ls147引脚图管脚图和功能真值表优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入信号进行编码。

常用的集成优先编码器IC有10线-4线、8线-3线两种。

10线-4线优先编码器常见的型号为54/74147、54/74LS147,8线-3线优先编码器常见的型号为54/74148、54/74LS148。

下面我们以TTL中规模集成电路74LS147为例介绍8421→BCD码优先编码器的功能。

10线-4线8421 BCD码优先编码器74LS147的真值表见表3.5。

74LS147的引脚图如图3.5所示,其中第9脚NC为空。

74LS147优先编码器有9个输入端和4个输出端。

某个输入端为0,代表输入某一个十进制数。

当9个输入端全为1时,代表输入的是十进制数0。

4个输出端反映输入十进制数的BCD 码编码输出。

74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421 BCD编码。

当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421 BCD编码输出。

表3.5 74LS147的真值表数字电路CD4511的原理(引脚及功能)CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。

可直接驱动LED显示器。

CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,引脚排列如图 2 所示。

其中a b c d 为 BCD 码输入,a为最低位。

LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。

BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时, B1端应加高电平。

另外 CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。

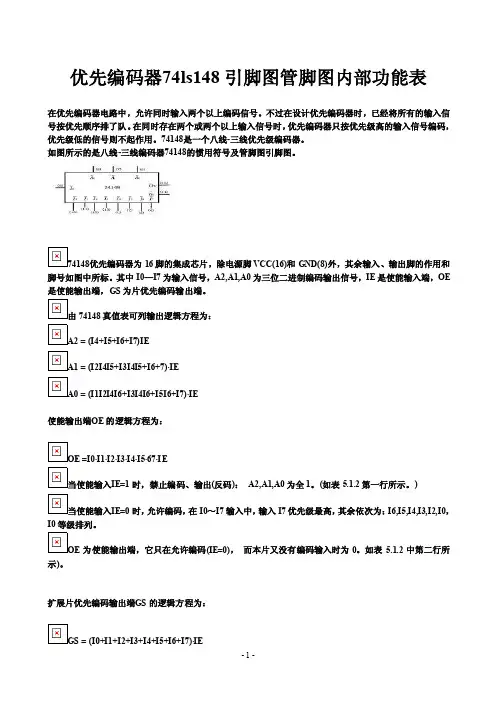

优先编码器74ls148引脚图管脚图内部功能表在优先编码器电路中,允许同时输入两个以上编码信号。

不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队。

在同时存在两个或两个以上输入信号时,优先编码器只按优先级高的输入信号编码,优先级低的信号则不起作用。

74148是一个八线-三线优先级编码器。

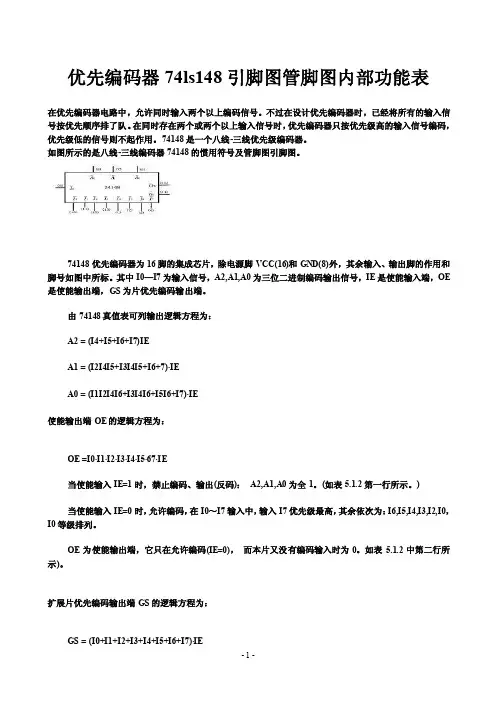

如图所示的是八线-三线编码器74148的惯用符号及管脚图引脚图。

74148优先编码器为16脚的集成芯片,除电源脚VC C(16)和GND(8)外,其余输入、输出脚的作用和脚号如图中所标。

其中I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE 是使能输出端,GS为片优先编码输出端。

由74148真值表可列输出逻辑方程为:A2 = (I4+I5+I6+I7)IEA1 = (I2I4I5+I3I4I5+I6+7)·IEA0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE使能输出端O E的逻辑方程为:OE =I0·I1·I2·I3·I4·I5·67·IE当使能输入I E=1时,禁止编码、输出(反码):A2,A1,A0为全1。

(如表5.1.2第一行所示。

)当使能输入I E=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。

OE为使能输出端,它只在允许编码(IE=0),而本片又没有编码输入时为0。

如表5.1.2中第二行所示)。

扩展片优先编码输出端G S的逻辑方程为:GS = (I0+I1+I2+I3+I4+I5+I6+I7)·IEGS为片优先编码输出端,它在允许编码(IE=0),且有编码输入信号时为0(如表5.1.2中第三至第十行);若允许编码而无编码输入信号时为1(如表5.1.2第二行);在不允许编码(IE=1)时,它也为1(如表5.1.2第一行)。

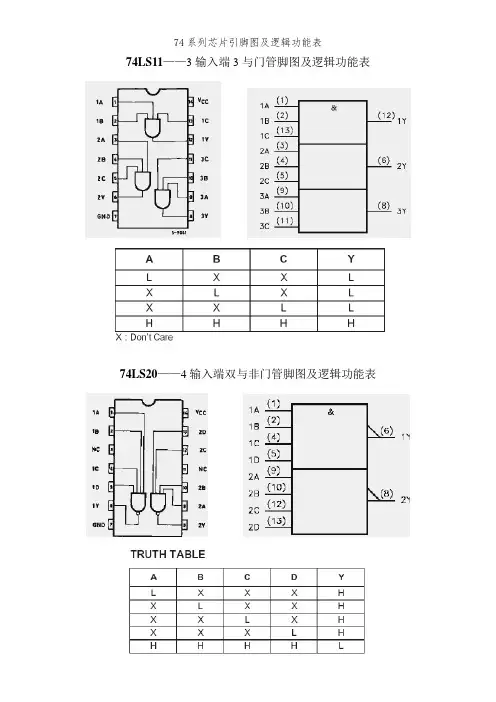

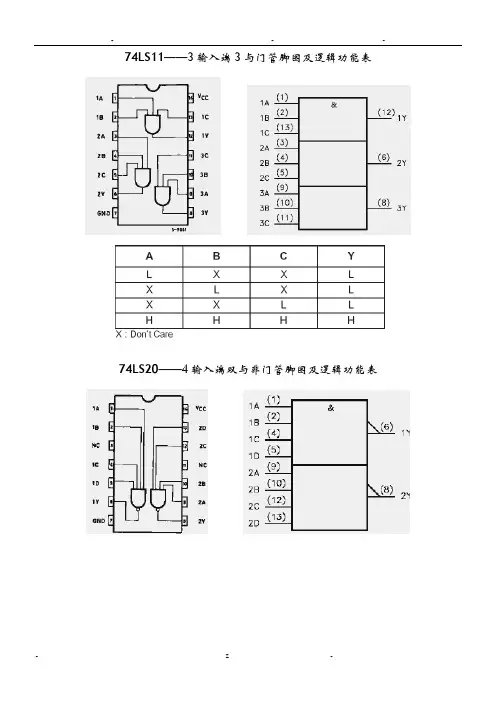

74LS11——3输入端3与门管脚图及逻辑功能表

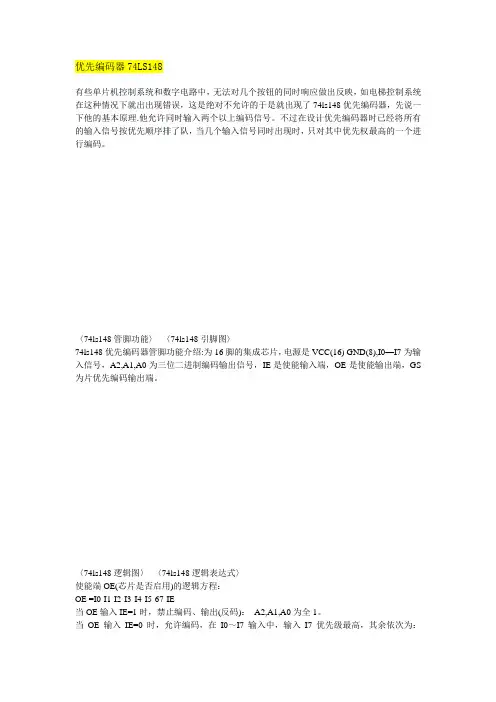

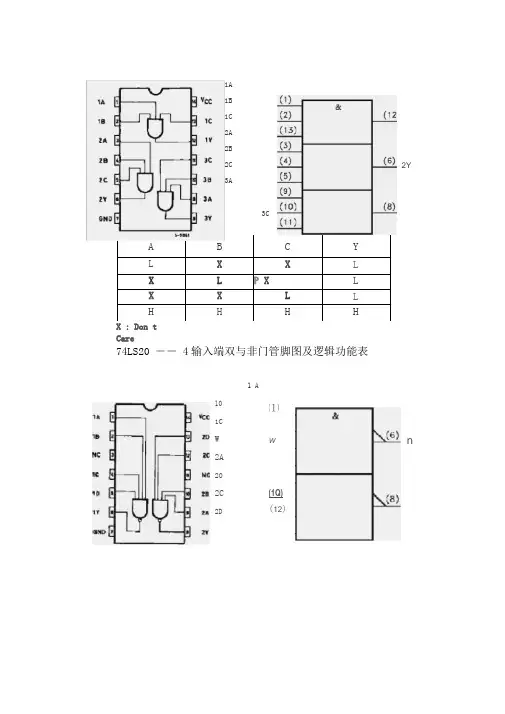

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3

与或非门

74LS08——2输入4与门。

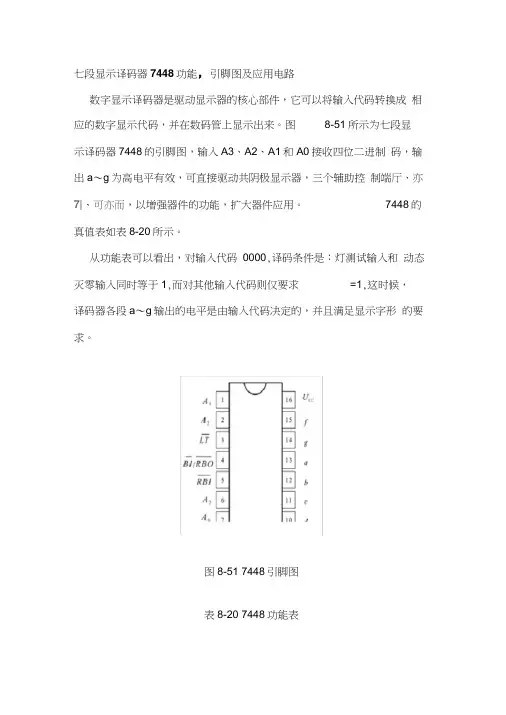

七段显示译码器7448功能,引脚图及应用电路数字显示译码器是驱动显示器的核心部件,它可以将输入代码转换成相应的数字显示代码,并在数码管上显示出来。

图8-51所示为七段显示译码器7448的引脚图,输入A3、A2、A1和A0接收四位二进制码,输出a〜g为高电平有效,可直接驱动共阴极显示器,三个辅助控制端厅、亦7|、可亦而,以增强器件的功能,扩大器件应用。

7448的真值表如表8-20所示。

从功能表可以看出,对输入代码0000,译码条件是:灯测试输入和动态灭零输入同时等于1,而对其他输入代码则仅要求=1,这时候,译码器各段a〜g输出的电平是由输入代码决定的,并且满足显示字形的要求。

图8-51 7448引脚图表8-20 7448功能表十轆数输入输出17A A A他。

住b d/s 01100u0I L11111011K00011011000021K00101110110131K D0111111100141K Q10010110011 1乂010]11011011«1011010011111710111111]0000>110001111111191*1001111110111011D1d100A1101111K101110n11001121K11D010i0D0]113111D111001011H1K111010001111151111]1D000000消隐:X00000000垃X X X K动态灭零1V00D000Q00000 0丈M艾11111111灯测试输入厅I低电平有效。

当厅=0时,无论其他输入端是什么状态,所有输出a〜g均为1,显示字形&该输入端常用于检查7448本身及显示器的好坏。

动态灭零输入亟低电平有效。

当厅=1,画川,且输入代码_ 1时,输出a〜g均为低电平,即与0000码相应的字形0 不显示,故称灭零”利用盯=1与画=0,可以实现某一位数码的消隐”时,厨亦而,其他情况下阪帀而=1。

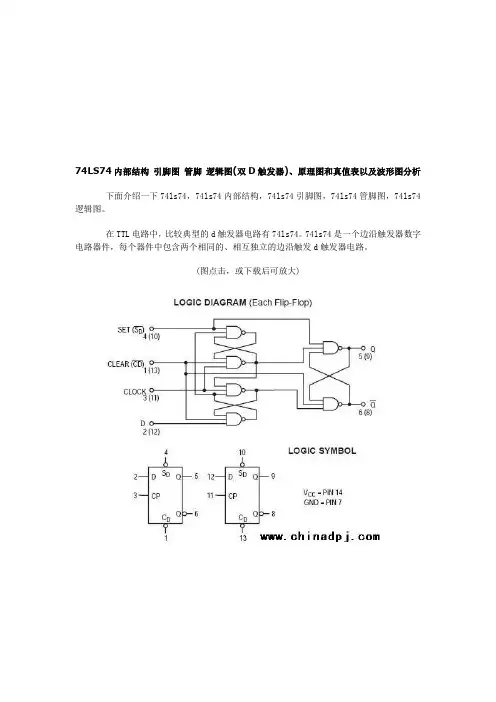

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

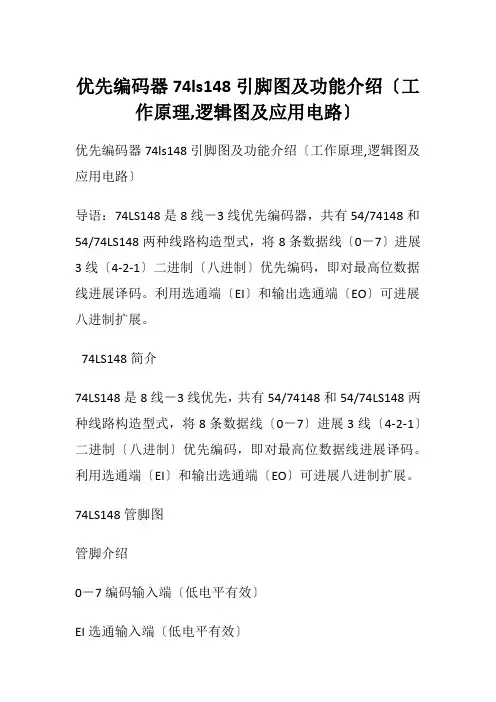

优先编码器74ls148引脚图及功能介绍〔工作原理,逻辑图及应用电路〕优先编码器74ls148引脚图及功能介绍〔工作原理,逻辑图及应用电路〕导语:74LS148是8线-3线优先编码器,共有54/74148和54/74LS148两种线路构造型式,将8条数据线〔0-7〕进展3线〔4-2-1〕二进制〔八进制〕优先编码,即对最高位数据线进展译码。

利用选通端〔EI〕和输出选通端〔EO〕可进展八进制扩展。

74LS148简介74LS148是8线-3线优先,共有54/74148和54/74LS148两种线路构造型式,将8条数据线〔0-7〕进展3线〔4-2-1〕二进制〔八进制〕优先编码,即对最高位数据线进展译码。

利用选通端〔EI〕和输出选通端〔EO〕可进展八进制扩展。

74LS148管脚图管脚介绍0-7编码输入端〔低电平有效〕EI选通输入端〔低电平有效〕A0、A1、A2三位二进制编码输出信号即编码输出端〔低电平有效〕GS片优先编码输出端即宽展端〔低电平有效〕EO选通输出端,即使能输出端74ls148逻辑图74ls148真值表由74ls148真值表可列输出逻辑方程为:A2=〔I4+I5+I6+I7〕IEA1=〔I2I4I5+I3I4I5+I6+7〕·IEA0=〔I1I2I4I6+I3I4I6+I5I6+I7〕·IE74LS148工作原理该有8个信号输入端,3个二进制码输出端。

此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。

当EI=0时,编码器工作;而当EI=1时,那么不管8个输入端为何种状态,3个输出端均为高电平,且优先标志端和输出使能端均为高电平,编码器处于非工作状态。

这种情况被称为输入低电平有效,输出也为低电来有效的情况。

当EI为0,且至少有一个输入端有编码恳求信号〔逻辑0〕时,优先编码工作状态标志GS为0。

说明编码器处于工作状态,否那么为1。

74ls148工作参数电源电压:min4.75Vtype5.0Vmax5.25V输入电压:min2V发射极间电压:±5.5V工作环境温度:0~70℃贮存温度:-65~150℃74ls148应用电路1.74ls148定时电路74LS48的7,6,2,3引脚承受来自74LS192的输出信号并把它译码显示在数码管上。

优先编码器74LS148有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8),I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS 为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉使能端OE(芯片是否启用)的逻辑方程:OE =I0·I1·I2·I3·I4·I5·67·IE当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。

当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:输入输出EI I0I1I2I3I4I5I6I7A2A1A0GS EO1 x x x x x x x x 1 1 1 1 10 1 1 1 1 1 1 1 1 1 1 1 1 00 x x x x x x x 0 0 0 0 0 10 x x x x x x 0 1 0 0 1 1 00 x x x x x 0 1 1 0 1 0 1 00 x x x x 0 1 1 1 0 1 1 1 00 x x x 0 1 1 1 1 1 0 0 1 00 x x 0 1 1 1 1 1 1 0 1 1 00 x 0 1 1 1 1 1 1 1 1 0 1 00 0 1 1 1 1 1 1 1 1 1 1 1 0<优先编码器74ls148功能表>从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I6,…,I0 。

1A 1B 1C 2A 2B 2C 3A74LS20 ―― 4输入端双与非门管脚图及逻辑功能表1 A101CW 2A202C2DABCY L X X L X L P XL XXLL HH HH3CCare2Y⑴W(1Q)(12)nTRUTH TABLEABCD Y LX XXH P XL X x : H X X L XH X X X L H HHHHL74LS21 —— 4输入端双与门管脚图及逻辑功能表1 A 1日 1C 1 D 2AA B C D YLX XXL XLX X LXXLXLX P XX L L HHHHH2C 2D1Y2¥(6)TRUTH TABLEA BcYL L L H HXXL X HX L XX HLx : Dorn cars74LS42 —— BCD/十进制译码器管脚图及逻辑功能表BCD/DEC1A !B ?A2320 2Y GHD1C1YSB3T^CCA B C D 9 9<16) B-IM.NOBCD INPUT DECIMAL OUTPUT DC B A 0 1 2 3 4 B 6 7 89I L L L LH H H H H H H H H ! L L I H HL H H H H H H H H 2LL H L H HL H H H H H HH 3LL H H H H H L HH H H HH 斗 1 L H L L HHH H L H H H H H 51 L H L H :H H H H HL HH HH 6L H H L H HH H HH IH HH7L H H H H H H H H H H L HH8 H L L L H HH H H H H H LH9H L L H H H H H H H H H H LHL H LH H H H H H HH H HHL H HH H H H H H HH H H H H L L H HH H H H H H H HHH L H H H H H H H H HH H zH H H L H HH H H H H HH HHHHHH H HHHHHHHH74LS138 ―― 3-8线译码器管脚图及逻辑功能表INPUTSOUTPUTSENABLESELECTQZBO2AG1 C B A Y0 Y1 Y2 Y3Y4 Y5 ra Y? X X L X X X H H H HH H H H X H X X X X H H H H H H H H H X X X X X H HH H H HI H H L L H L L L L HH H H H H H L L H L L H H L 11 H H H H H L L H L H L H H L H H H H H LLHL H H HHH LHHH HLLH:H L L HHH HLHH HLL H HLH H HH H H L H HI1 H HHL H HH H H H L HL LHHHHHHHHHHHLY0Y ?3)■⑴)Y6—*cc *0TRUTH TABLEINPUTSOUTPUTSSELECTED OUTPUTENABLE SELECTYo*2 £GB AHX X HH H H NONELL L LHHHLLH HLHHY1LH LH H L HL HH "HHHL74LS148 ―― 8-3线优先编码器管脚图及逻辑功能表1A 13 1G2A 23 2G{£)_ (3)_⑴、⑴)1YQ 1Y1 1~22Y02F1 2Y2 2Y3GSJ2INPUTS 1 D ,CU1PUTS凹b⑴、⑵rs ⑶zD-/Z*C1/Z1 12/2123/2*3 4/Z145 G/J J E 7/2仃INPUTSOUTPUTSE1 0 1 23 45 6 7 A2 A1 AO GS EO HX X X X X X X X HH H H H ―LHH H H H H H H H H H H L LX X X X X X X L LL L LH L XX XXX XL H LL H LH L P X -XX 1X 「XP L H H L HL 1 L H L XX X X LHH H L HH L H F LXXX L HHH H H L L L H L r x P X L 1H 1Hr HH H H L H 1L H LX L "HH HP H H H H H L L H L LP H H「 H「Hn HHHHHHLHX: Don't CareV18 EN d74LS151 ――八选一数据选择器管脚图及逻辑功能表DATA i X INPUTS 1 D fOJTFUISSTROBEJK J皿】E 工i- 【占5 th门1 〔古 叮[甲i«] '7w ] [,*]vccDJ 卞"TACcINP-T5g.A 1DATA B ? 5FLFCIC -INPUTSOUTPUTSSELECTSTROBE¥w C B A S X X X H LH L L L LDoL L H L Di Di L H L L S D? L H HLo 3 D3H L PL PLD 41刁H LH LD S H H L L DeD&HHHL巧574LS153 ――双4选1数据选择器管脚图及逻辑功能表TRUTH TABLESELECT INPUTS DATA INPUTS STROBEOUTPUT YB A W Cl Cj c 3 GX X X X X X HL LLLX X ~PXLLLLHX XXLHL H X L X X LL n L H X H X X LH H L X X L X LL H L X X H「PX T L JH 'HH X X XL LL 「L HHXXXHLH —ADaclmal cr Function InputsOutputsLTRBIA3A2Al AO Bl/RBQ a b Gd 0 7gH n L LL LH L L L L L L n 1 H X L L LHH HL L HH H H2 H X L L HL H LL H L _H L □HXLLHHHLLLLHHL4 H X L H L LH H L LHH L L5 H K L H L HH L H LL H L L5 H X L H H LH H H LL -L L7 H X LH HH H L LLHHHH flHXH LLLHLLLLLLLB H X H L L H H LL L H HL L 10H X HLH L H H HH LH L tl H X HLH n n H HL LHH L12 H X HI- L L H H L H HHL L13HXHHLHHLHHLHLL14 H X H H H LH HHHL- L L15H X H H H HH HHHHH H HBl X X XX X XL H H H H H HHRSI H L LLL L L HH H H H HLTLXX岛XXHLLLLLLL码管13 12 n 1D 9 15 1* 4示译码 平有 共阳数74LS55——双4输入与或非门4-2-3与或非门74LS54z--3[LPLSCDI1ED Vlewi74LS08——2输入4与门AAQcDUIF1JHFEN¥口口口nriri r】-…-一,'.bQ-L:-1Bl-1R4I? 12 i* io j« la*丄1牛 REja、pY-ABQ C。

优先编码器74ls148引脚图管脚图内部功能表在优先编码器电路中,允许同时输入两个以上编码信号。

不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队。

在同时存在两个或两个以上输入信号时,优先编码器只按优先级高的输入信号编码,优先级低的信号则不起作用。

74148是一个八线-三线优先级编码器。

如图所示的是八线-三线编码器74148的惯用符号及管脚图引脚图。

74148优先编码器为16脚的集成芯片,除电源脚VCC(16)和GND(8)外,其余输入、输出脚的作用和脚号如图中所标。

其中I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE 是使能输出端,GS为片优先编码输出端。

由74148真值表可列输出逻辑方程为:A2 = (I4+I5+I6+I7)IEA1 = (I2I4I5+I3I4I5+I6+7)·IEA0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE使能输出端OE的逻辑方程为:OE =I0·I1·I2·I3·I4·I5·67·IE当使能输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。

(如表5.1.2第一行所示。

)当使能输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。

OE为使能输出端,它只在允许编码(IE=0),而本片又没有编码输入时为0。

如表5.1.2中第二行所示)。

扩展片优先编码输出端GS的逻辑方程为:GS = (I0+I1+I2+I3+I4+I5+I6+I7)·IEGS为片优先编码输出端,它在允许编码(IE=0),且有编码输入信号时为0(如表5.1.2中第三至第十行);若允许编码而无编码输入信号时为1(如表5.1.2第二行);在不允许编码(IE=1)时,它也为1(如表5.1.2第一行)。

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门74LS54——4-2-3与或非门

74LS08——2输入4与门。

74LS74 内部结构引脚图管脚逻辑图(双 D 触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74 ,74ls74 内部结构,74ls74 引脚图,74ls74 管脚图,74ls74 逻辑图。

在TTL 电路中,比较典型的 d 触发器电路有74ls74 。

74ls74 是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发 d 触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)原理图和真值表以及波形图分析边沿 D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿 D 触发器也称为维持- 阻塞边沿 D 触发器。

电路结构: 该触发器由 6 个与非门组成,其中G1 和G2 构成基本RS 触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0 且RD=1 时,不论输入端 D 为何种状态,都会使Q=1 ,Q=0 ,即触发器置 1 ;当SD=1 且RD=0 时,触发器的状态为0,SD 和RD 通常又称为直接置 1 和置0 端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1. CP=0 时,与非门G3 和G4 封锁,其输出Q3=Q4=1 ,触发器的状态不变。

同时,由于Q3 至Q5 和Q4 至Q6 的反馈信号将这两个门打开,因此可接收输入信号 D ,Q5=D ,Q6=Q5=D 。

2. 当CP由0变1时触发器翻转。

这时G3 和G4 打开,它们的输入Q3 和Q4 的状态由G5 和G6 的输出状态决定。

Q3=Q5=D ,Q4=Q6=D 。

由基本RS 触发器的逻辑功能可知,Q =D 。

3. 触发器翻转后,在CP=1 时输入信号被封锁。

74ls42 二-十进制(4线-10线)译码器(bcd输入)

74ls48 bcd-七段显示译码器/驱动器

CC14585 4位数值比较器

(1)只比较两个4位二进制数时

用一片CC14585即可,扩展端I(A<B)接低电平,I(A>B)和I(A=B) 接高电平。

(2)当比较两个4位以上8位以下的二进制数时

CC14585 4位数值比较器

用两片74LS138接成的4线-16线译码器

74ls138 3-8线译码器/多路转换器

74ls147 二-十进制(10线-4线)优先编码器

74ls148 8线-3线八进制优先编码器

74ls151 8选1数据选择器(互补输出)

74ls160 可预置同步十进制加法计数器(异步清除) 74ls161 可预置四位同步二进制计数器(并清除异步)

74ls190 同步十进制可逆计数器

74ls191 单时钟同步二进制加/减计数器

74ls194 四位移位寄存器

74ls283 4位超前进位加法器

74ls290 二-五-十进制异步计数器。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6 =Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q =D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q 3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门74LS54——4-2-3与或非门

74LS08——2输入4与门

如有侵权请联系告知删除,感谢你们的配合!。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

74ls148管脚图引脚功能表真值表逻辑图扩展资料

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉

74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉

使能端OE(芯片是否启用)的逻辑方程:

<74ls148真值表>

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

用两个74ls148优先编码器芯片扩展为十六线-四线优先编码器的电路连线图

最新文件---------------- 仅供参考--------------------已改成word文本--------------------- 方便更改。