实验4组合逻辑器件的应用(I)-译码器及其应用—74LS138、74LS148

- 格式:ppt

- 大小:5.38 MB

- 文档页数:24

实验五译码器及其应用一、实验目的1、掌握中规模集成译码器的逻辑功能和使用方法2、熟悉数码管的使用二、实验设备与器件1、+5V直流电源2、逻辑电平开关3、逻辑电平显示器4、拨码开关组5、译码显示器6、 74LS138×2 CC4511三、实验内容1、74LS138译码器逻辑功能测试将译码器使能端S1、2S、3S及地址端A2、A1、A0分别接至逻辑电平开关输出口,八个Y⋅⋅⋅依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表6-输出端07Y1逐项测试74LS138的逻辑功能。

图6-1(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

当S1=1,2S+3S=0时,器件正常工作,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

图6-1 3-8线译码器 74LS138逻辑图及引脚排列表6-12、二进制译码器还能方便地实现逻辑函数,如图6-3所示,实现的逻辑函数是 Z =C B A C B A C B A +++ABC图6-2 作数据分配器 图6-3 实现逻辑函数3、码显示译码器及译码显示电路数据拨码开关的使用。

将实验装置上的四组拨码开关的输出A i、B i、C i、D i分别接至4组显示译码/驱动器CC4511的对应输入口,LE、BI、LT接至三个逻辑开关的输出插口,接上+5V显示器的电源,然后按功能表6-2输入的要求揿动四个数码的增减键(“+”与“-”键)和操作与LE、BI、LT对应的三个逻辑开关,观测拨码盘上的四位数与LED数码管显示的对应数字是否一致,及译码显示是否正常。

a、七段发光二极管(LED)数码管LED数码管是目前最常用的数字显示器,图6-5(a)、(b)为共阴管和共阳管的电路,(c)为两种不同出线形式的引出脚功能图。

试验四 译码器、 编码器及其应用试验人员: 班号: 学号:一、 试验目(1) 掌握中规模集成译码器逻辑功效和使用方法; (2) 熟悉掌握集成译码器和编码器应用; (3) 掌握集成译码器扩展方法。

二、 试验设备数字电路试验箱, 74LS20, 74LS138。

三、 试验内容(1) 74LS138译码器逻辑功效测试。

将74LS138输出Y 0̅~Y 7̅接数字试验箱LED 管, 地址A 2A 1A 0输入接试验箱开关, 使能端接固定电平(V CC 或GND )。

电路图如Figure 1所表示:Figure 2EN 1EN 2A ̅̅̅̅̅̅̅ EN 2A ̅̅̅̅̅̅̅≠100时, 任意拨动开关, 观察LED 显示状态, 统计观察结果。

EN 1EN 2A ̅̅̅̅̅̅̅ EN 2A ̅̅̅̅̅̅̅=100时, 按二进制次序拨动开关, 观察LED 显示状态, 并与功效表对照, 统计观察结果。

用Multisim进行仿真, 电路如Figure 3所表示。

将结果与上面试验结果对照。

Figure 4(2) 利用3-8译码器74LS138和与非门74LS20实现函数:Y=A B̅+B̅C+ABC四输入与非门74LS20管脚图以下:对函数表示式进行化简:Y=A B̅+B̅C+ABC=A B̅C+A B̅C+AB̅C+ABC̅̅̅̅̅̅̅̅̅̅̅=Y0+Y1+Y4+Y7=Y0̅Y1̅Y4̅Y7̅按Figure 5所表示电路连接。

并用Multisim进行仿真, 将结果对比。

Figure 6(3) 用两片74LS138组成4-16线译码器。

因为要用两片3-8实现4-16译码器, 输出端子数目8×2=16刚好够用。

而输入端只有 A、 B、 C三个, 故要另用使能端进行片选使两片138译码器进行分时工作。

而试验台上小灯泡不够用, 故只用一个灯泡, 而用连接灯泡导线测试Y x̅, 在各端子上移动即可。

在multisim中仿真电路连接如Figure 7所表示(试验台上电路没有接下面两个8灯LED):Figure 8四、试验结果(1) 74LS138译码器逻辑功效测试。

译码器及其应用试验汇报范文5试验三译码器及其应用一、试验目旳1、掌握译码器旳测试措施。

2、理解中规模集成译码器旳功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路旳措施。

、学习译码器旳扩展。

4二、试验设备及器件1、数字逻辑电路试验板 1块2、74HC138 3-8线译码器 2片3、74HC20 双4输入与非门 1片三、试验原理1、中规模集成译码器74HC13874HC138是集成3线,8线译码器,在数字系统中应用比较广泛。

图3,1是其引脚排列。

其中 A2 、A1 、A0为地址输入端, 0Y, 7Y为译码输出端,S1、2S、3S为使能端。

表3-1为74HC138真值表。

74HC138工作原理为:当S1=1,S2+S3=0时,电路完毕译码功能,输出低电平有效。

其中:2、译码器应用由于74HC138 三-八线译码器旳输出包括了三变量数字信号旳所有八种组合,每一种输出端表达一种最小项,因此可以运用八条输出线组合构成三变量旳任意组合电路。

四、试验内容1、译码器74HC138 逻辑功能测试(1)控制端功能测试测试电路如图3-2所示。

按表3-2所示条件输入开关状态。

观测并记录译码器输出状态。

LED指示灯亮为0,灯不亮为1。

测试成果如下:输入输出 S1 ,S2 ,S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 1 x x x x x 1 1 1 1 1 1 1 1 1 1 0 x x x 1 1 1 1 1 1 1 1 1 0 1 x x x 1 1 1 1 1 1 1 11 1 1 x x x 1 1 1 1 1 1 1 1(2)逻辑功能测试将译码器使能端 S1、,S2、,S3地址端A2、A1、A0 分别接至逻辑电平开关输出口,八个输出端依次连接在逻辑电平显示屏旳八个输入口上,拨动逻辑电平开关,按表3, 3逐项测试74HC138旳逻辑功能。

逻辑功能测试,成果如下:输入输出 S1 ,S2+,S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 x x x x 1 1 1 1 11 1 1 x 1 x x x 1 1 1 1 1 1 1 1 当时我A2A1A0旳状态是111,老师问我在发光二极管应对应哪个灯亮,我回答是八。

实验4 译码器74LS138应用电路一、实验内容1. 实现逻辑函数的基本原理。

2. 验证用最小项译码器产生一组多输出逻辑函数:C B A Z ACBC AB Z C B A C B A C B A Z +=++=++=321组合电路如图1所示。

二、演示电路图1的组合逻辑电路能否产生上式逻辑函数,我们可按该电路的要求创建EWB 电路予以验证。

首先在数字电路功能库中拖选DEC (多路译码器),再从其器件列表框里点选74138。

器件74138与国产T4138完全一样。

用数字信号发生器提供8个二进制数,如图1所示;单击逻辑门电路库图标,拽出与非门三只作为逻辑函数输出门;最后从指示器件库里拖出三个彩色指示探头,用做输出指示。

验证图1电路的虚拟实验电路图如图2所示图2 验证图1电路的虚拟实验电路图图3 数字信号发生器面板图4 逻辑转换器面板三、验证原理与步骤 1. 原理采用单步运行方式,数字信号发生器逐一输出8个三位二进制数据(000,001,010,011,100,101,110,111),与此同时,如在Z 1、Z 2、Z 3的输出端上为高电平即“1”时,彩色指示探头灯亮。

记录此刻的输入信号,它所对应的最小项就是输出函数表达式中的一项。

对应关系为:C B A m ==0000,C B A m ==1001,C B A m ==2010,BC A m ==3011,C B A m ==4100,C B A m ==5101,C AB m ==6110,ABC m ==7111。

2. 步骤单击数字信号发生器面板上的控制按钮Step ,采用单步运行方式。

观测结果是:接在Z 1输出端上的红灯亮了三次(m 1、m 2、m 4);接在Z 2输出端上的绿灯亮了四次(m 7、m 6、m 3 、m 5);接在Z 3输出端上的蓝灯亮了五次(m 0、m 1、m 4 、m 2、m 6)。

根据以上观测结果,写出输出函数Z 1、Z 2、Z 3的最小项表达式,它们是C AB C B A C B A C B A C B A m m m m m Z CB A BC A C AB ABC m m m m Z CB AC B A C B A m m m Z ++++=++++=+++=+++=++=++=642103765324211 化简后得C B A Z ACBC AB Z C B A C B A C B A Z +=++=++=321于是,验证了图1所示电路。

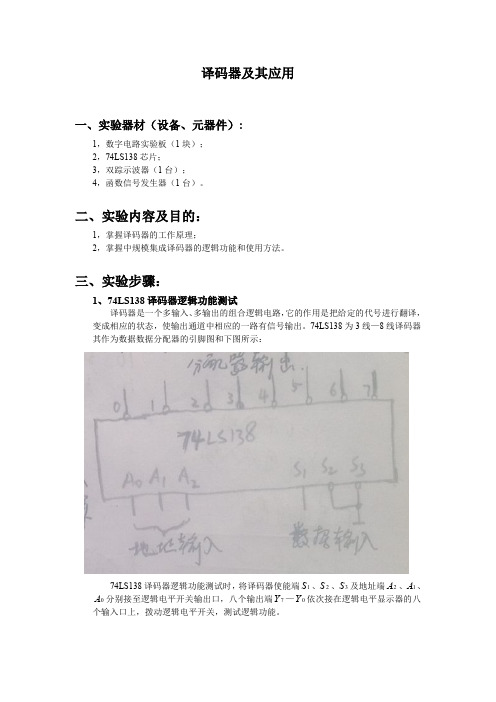

译码器及其应用实验一、实验目的1、掌握中规模集成译码器的逻辑功能和使用方法2、熟悉数码管的使用二、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器可分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1、变量译码器(又称二进制译码器)以3线-8线译码器74LS138为例进行分析,图3-1(a)、(b)分别为其逻辑图及引脚排列。

表3-1为74LS138功能表(a) (b)图3-1 3-8线译码器74LS138逻辑图及引脚排列表3-1一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图3-2所示。

二进制译码器还能方便地实现逻辑函数,如图3-3所示,实现的逻辑函数是Z=CBACBACBA+++ABC图3-2 作数据分配器图3-3 实现逻辑函数利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如图3-4所示。

图3-4 用两片74LS138组合成4/16译码器三、实验设备与器件1、数字电路实验箱2、 74LS138×2四、实验内容1、74LS138译码器逻辑功能测试将译码器使能端S 1、2S 、3S 及地址端A 2、A 1、A 0 分别接至逻辑电平开关输出口,八个输出端07Y Y ⋅⋅⋅依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表3-1逐项测试74LS138的逻辑功能。

2、用74LS138构成时序脉冲分配器参照图3-2和实验原理说明,时钟脉冲CP 频率约为10KHz ,要求分配器输出端70Y Y ⋅⋅⋅的信号与CP 输入信号同相,用示波器观察和记录在地址端A 2、A 1、A 0分别取000~111 8种不同状态时70Y Y ⋅⋅⋅端的输出波形,注意输出波形与CP 输入波形之间的相位关系。

3、用两片74LS138组合成一个4线—16线译码器,并进行实验。

实验四用译码器实现组合逻辑电路一、 实验目的:学会用译码器实现组合逻辑电路 二、 实验原理:用译码器加上门电路的方法,来实现较复杂的组合逻辑电路,简 单方便。

本实验主要使用的译码器是74LS138。

对门电路的选择以与 非门居多。

72LS138译码器的功能特点: 1、译码器的工作条件: 译码器必须在STa=1时,STb = STc = O 才能正常工作2、译码器实现函数所用门电路的特点:三、 实验仪器及器材:集成块:74LS138 74LS42 74LS20 74LS08 四、 实验内容与步骤:(要求写出各电路的设计步骤,并画出实验电 路图。

)1、设计一个三变量,判断奇数个“ 1”的电路(要求用译码器和 与非门实现)。

1真值表1±£ 垃二山「_£. c D C 匚 EA F Q p- N 2 & E VABC 匚D Y ]NDS1J hp1J 1J- r~~12逻辑表达式Y=ABC+ABC+ABC+ABC= ---------------------3仿真图为2、某工厂有A、B、C三台设备,A、B的功率均为10W, C的功率为20W,这些设备由和两台发电机供电,两台发电机的最大输出功率分别为10W和30W,要求设计一个逻辑电路以最节约能源的方式启、停发电机,来控制三台设备的运转、停止(要求用译码器和与非门、与门实现)。

1真值表 A BC D E0 0 0 0 01 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 1112由卡诺图得到逻辑表达式为 D=A/B/C+/AB/C+ABC (247) E=C+AB (13567)3仿真图为1列真值表2函数逻辑表达式Si 二/Ai./Bi.Ci-1+/Ai.Bi./Ci-1+Ai./Bi./Ci-1 + Ci=Ai.Bi+Ai.Ci-1+Bi.Ci-1 3仿真电路图为五、实验体会:通过与“实验三”实现组合逻辑电路的方法的比较, 写出使用自己的体会。

实验五译码器及其应用一、实验目的1、掌握中规模集成译码器的逻辑功能和使用方法2、熟悉数码管的使用二、 实验设备与器件1 、+ 5V 直流电源23 、逻辑电平显示器45 、译码显示器6三、 实验内容1、74LS138译码器逻辑功能测试将译码器使能端 S 、S 2、S 3及地址端A 2、A 1、A 分别接至逻辑电平开关输出口,八个输出端Y 7 Y 0依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表 6- 1逐项测试74LS138的逻辑功能。

图6- 1(a )、(b )分别为其逻辑图及引脚排列。

其中A 2、A 、A o 为地址输入端, Y o 〜丫7为译码输出端,Si 、S 2、S 3为使能端。

表输入输 出sS 2 + S 3A A 1 AY 0 Y 1 Y 2 Y 3 Y 4 Y Y 6 Y 7当S = 1, S 2 + S 3 = 0时,器件正常工作,地址码所指定的输出端有信号(为 0)输出,其它所有输出端均无信号(全为 1) 输出。

当 S = o , S 2 + S 3 = X 时,或 S 1 = X , S 2 + S 3 =1时,译码器被禁止,所有输出同时为 1。

1图6 - 1 3 - 8线译码器(b)ho As74LS138AaV GGYoAlY LA J¥2Y JY I:Y=Yft SiGNDJ5工1377一0一逻辑图及引脚排列、逻辑电平开关 、拨码开关组 、74LS138 X2CC45112= ABC ABC ABC + ABC图6- 2 作数据分配器图6-3实现逻辑函数3、码显示译码器及译码显示电路数据拨码开关的使用。

将实验装置上的四组拨码开关的输出A 、B 、C 、D 分别接至4组显示译码/驱动器CC4511的对应输入口, LE 、BI 、LT 接至三个逻辑开关的输出插口,接上+5V 显示器的电源,然后按功能表 6 — 2输入的要求揿动四个数码的增减键(“ + ”与“―”键)和操作与LE 、BI 、LT 对应的三个逻辑开关,观测拨码盘上的四位数与LED 数码管显示的对应数字是否一致,及译码显示是否正常。