自动布局布线

- 格式:pptx

- 大小:1.78 MB

- 文档页数:82

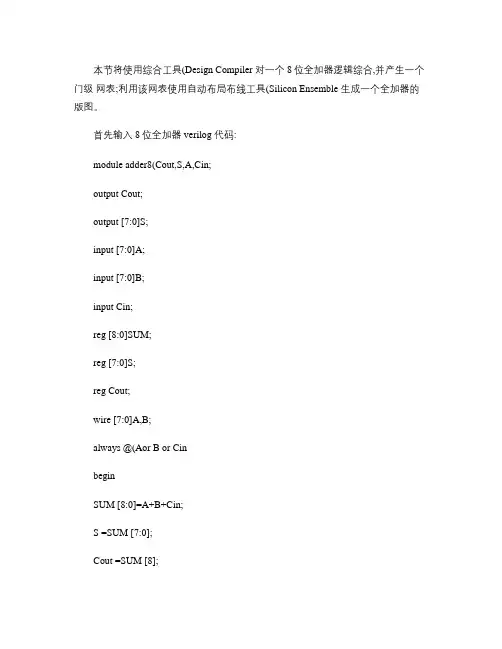

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。

首先输入 8位全加器 verilog 代码:module adder8(Cout,S,A,Cin;output Cout;output [7:0]S;input [7:0]A;input [7:0]B;input Cin;reg [8:0]SUM;reg [7:0]S;reg Cout;wire [7:0]A,B;always @(Aor B or CinbeginSUM [8:0]=A+B+Cin;S =SUM [7:0];Cout =SUM [8];endendmodule打开综合工具 DC (psyn_gui&File->Read..读入代码File->Setup..设置 3个相关工艺库将带红色 *号的 3个库设置如下图 Design->CompileDesign.. 编译Schematic->NewDesign Schematic View..可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。

在 psyn_gui-xg-t>后输入如下命令下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm&File->Import->LEF… 导入库的转换格式注意此文件的路径!File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息这里去掉后面的!继续 File->Import->Verilog… 导入网表 adder8_nl.v(此处要先删掉第一个工艺库这里要加上顶层模块名 adder8Floorplan->InitializeFloorplan…准备工作完成开始布局布线点击 Variables 将里面的 PLAN.LOWERLEFT.ORIGIN 由 FALSE 改为 TUREEdit ->Add ->Row… Area 的区域可以直接点击 Area 并在图上拖拽,并使其大小与芯片核一致File->Saveas… 保存为 fplanRoute->PlanPower… 设置电源环在 Plan Power 窗口中点击 AddRings…Place->Ios…放置输入输出Place->Cells…放置单元Place->FillerCells->AddCells…Route->RoutePower->FollowPins… 添加管脚(金属线宽设为 1.8 Route->Wroute…布线View->DisplayOptions… 检查管脚名设置 Pin 为 ONFile->Export->DEF… 命名为adder8_wrouted.def打开 icfb &再导入 DEF文件之前要确保你有如下图中的一些库文件File->Import->DEF…Enter “ tutorial ” for Library Name, “ adder8” for Cell Name, and “ autoRouted ”for View Name.打开 View 中的autoRoutedDesign->Save..Tool->Layout..将提取图转换为版图,这里需要改变几个参数 Edit->Search..点击Add Criteria然后做如下图的几个改动Apply Replace AllDesign->SaveAs..现在就可以打开 layout 了DRC… 熟悉吧! !。

自动化设备电气布线规范幻灯片课件一、引言随着工业自动化的不断发展,电气布线的重要性日益凸显。

为了保证自动化设备的稳定运行和安全性,我们必须遵循一定的电气布线规范。

今天,我将以幻灯片课件的形式,为大家讲解自动化设备电气布线的规范。

二、电气布线的基本原则1、安全性:在任何情况下,安全应该是首要考虑。

所有的电气线路和设备都应该安装在安全的环境中,以防止可能的电击、火灾等危险。

2、效率:布线应尽可能简洁、明了,避免线路交叉或冗余,以减少潜在的故障点和维护难度。

3、可维护性:线路应易于检查和维护。

任何故障都应能够方便地检测和修复。

4、兼容性:应确保所使用的线路和设备与自动化设备的其它部分兼容。

三、电气布线的具体规范1、线路颜色编码:根据国际电工委员会的规定,不同颜色的电线应连接到不同的线路上。

例如,红色电线应连接到电源正极,蓝色或黑色电线应连接到电源负极。

2、线路保护:所有电线都应有适当的保护,以防止机械损伤或过载。

例如,可以使用金属套管或塑料护套来保护电线。

3、线路标记:每条线路都应有清晰的标记,以方便识别和维护。

4、接地与屏蔽:所有金属部件和线路都应接地,以防止电磁干扰。

同时,对于可能受到电磁干扰的线路,应使用屏蔽线或光纤传输。

5、电源与信号布线:电源线和信号线应分开布线,以防止电磁干扰。

高电压和低电压的线路也应分开布线。

6、接线端子:所有接线端子都应牢固固定,以防止松动或接触不良。

同时,端子上的螺丝和螺母都应有适当的扭矩。

7、线路弯曲:线路应避免过度的弯曲或扭曲,以防止机械损伤或过载。

8、线路长度:在可能的情况下,应尽量减少线路的长度,以减少电阻和电感的影响。

9、防雷与过电压保护:对于可能受到雷电或过电压影响的线路和设备,应安装适当的保护装置。

10、环保:在设计和安装过程中,应尽量减少对环境的影响。

例如,应使用可回收的包装材料,减少废弃物的产生。

四、结论自动化设备的电气布线是一项重要而复杂的工作。

只有遵循一定的规范和标准,我们才能确保自动化设备的稳定运行和安全性。

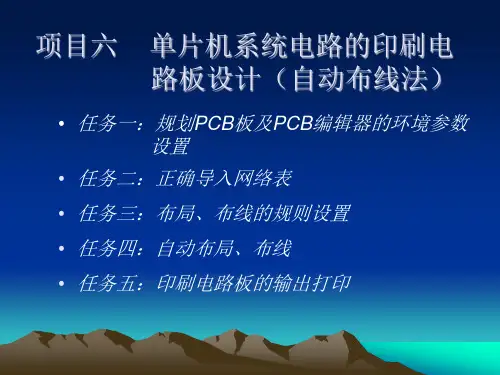

PCB辅助设计第9讲自动布线主要内容一、自动布线步骤二、自动装载网络表与元件三、元件布局四、自动布线设计规则设置五、自动布线六、手工调整七、设计规则检查八、元件重新编号及原理图更新一、自动布线步骤PCB自动布线就是通过计算机自动将原理图中元件间的逻辑连接转换为PCB铜箔连接,PCB的自动化设计实际上是一种半自动化的设计过程,还需要人工的干预才能设计出合格的PCB。

PCB自动布线的流程如下。

⑴绘制电路原理图,生成网络表。

⑵在PCB99SE中,规划印制板。

⑶装载原理图的网络表。

⑷自动布局及手工布局调整。

⑸自动布线参数设置。

⑹自动布线。

⑺手工布线调整及标注文字调整。

⑻输出PCB图。

采用打印机或绘图仪输出电路板图。

二、自动装载网络表与元件规划PCB后,执行Design→Load Nets载入网络表,屏幕弹出一个对话框,单击Browse按钮选择网络表文件(*.net),载入网络表,单击Execute按钮,将网络表文件中的元件调到当前印制板中,如图7-17所示。

图7-17中,载入的元件都散开排列在禁止布线边框之外(Protel99SE SP6之前的版本中,元件堆积在光标处),在布线前还必须进行自动布局。

三、元件布局1.元件布局前的处理⑴元件布局栅格设置执行Design→Options,在弹出的对话框中选择Options选项卡,设置捕获栅格和元件栅格X、Y方向的间距大小。

⑵字符串显示设置执行Tools→Preferences,在弹出的对话框中选择Display选项卡,在Draft thresholds选项区域中,减小Strings中的字符串阀值,完整显示字符串内容。

⑶元件布局参数设置执行Design→Rules,在对话框中选中Placement选项卡,屏幕出现元件布局参数设置对话框。

一般选择默认。

2.元件自动布局进行自动布局前,必须在Keep out Layer上先规划电路板的电气边界,然后载入网络表文件,否则屏幕会提示错误信息。

对于PCB 的设计,Altium Designer .0提供了详尽的10 种不同的设计规则,这些设计规则则包括导线放置、导线布线方法、元件放置、布线规则、元件移动和信号完整性等规则。

根据这些规则,Protel DXP 进行自动布局和自动布线。

很大程度上,布线是否成功和布线的质量的高低取决于设计规则的合理性,也依赖于用户的设计经验。

对于具体的电路可以采用不同的设计规则,如果是设计双面板,很多规则可以采用系统默认值,系统默认值就是对双面板进行布线的设置。

本章将对Altium Designer .0的布线规则进行讲解。

.1 设计规则设置进入设计规则设置对话框的方法是在PCB 电路板编辑环境下,从Protel DXP 的主菜单中执行菜单命令Desing/Rules ……,系统将弹出如图— 1 所示的PCB Rules and Constraints Editor(PCB 设计规则和约束) 对话框。

该对话框左侧显示的是设计规则的类型,共分10 类。

左边列出的是Desing Rules( 设计规则) ,其中包括Electrical (电气类型)、Routing (布线类型)、SMT (表面粘着元件类型)规则等等,右边则显示对应设计规则的设置属性。

该对话框左下角有按钮Priorities ,单击该按钮,可以对同时存在的多个设计规则设置优先权的大小。

对这些设计规则的基本操作有:新建规则、删除规则、导出和导入规则等。

可以在左边任一类规则上右击鼠标,将会弹出如图— 2 所示的菜单。

在该设计规则菜单中,New Rule 是新建规则;Delete Rule 是删除规则;Export Rules 是将规则导出,将以 .rul 为后缀名导出到文件中;Import Rules 是从文件中导入规则;Report ……选项,将当前规则以报告文件的方式给出。

图— 2 设计规则菜单下面,将分别介绍各类设计规则的设置和使用方法。

.2 电气设计规则Electrical (电气设计)规则是设置电路板在布线时必须遵守,包括安全距离、短路允许等4 个小方面设置。

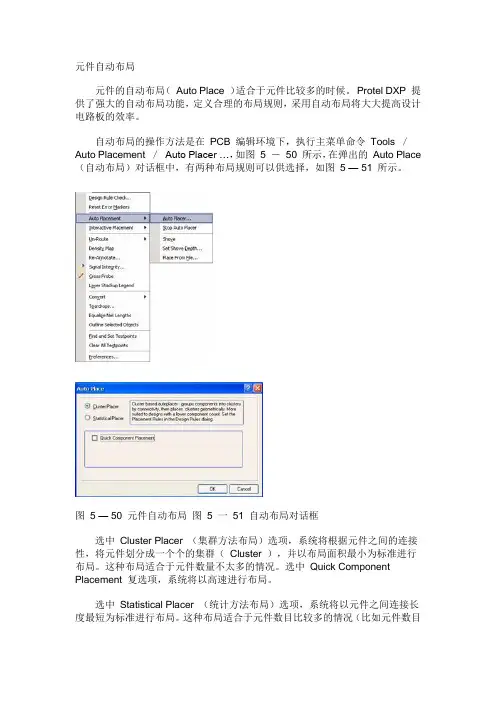

元件自动布局元件的自动布局(Auto Place )适合于元件比较多的时候。

Protel DXP 提供了强大的自动布局功能,定义合理的布局规则,采用自动布局将大大提高设计电路板的效率。

自动布局的操作方法是在PCB 编辑环境下,执行主菜单命令Tools /Auto Placement /Auto Placer …,如图5 -50 所示,在弹出的Auto Place (自动布局)对话框中,有两种布局规则可以供选择,如图 5 — 51 所示。

图5 — 50 元件自动布局图 5 一51 自动布局对话框选中Cluster Placer (集群方法布局)选项,系统将根据元件之间的连接性,将元件划分成一个个的集群(Cluster ),并以布局面积最小为标准进行布局。

这种布局适合于元件数量不太多的情况。

选中Quick Component Placement 复选项,系统将以高速进行布局。

选中Statistical Placer (统计方法布局)选项,系统将以元件之间连接长度最短为标准进行布局。

这种布局适合于元件数目比较多的情况(比如元件数目大于100 )。

选择该选项后,对话框中的说明及设置将随之变化,如图 5 — 52 所示。

图5 -52 统计方法布局对话框统计方法布局对话框中的设置及功能如下:● Group Components 复选项:用于将当前布局中连接密切的元件组成一组,即布局时将这些元件作为整体来考虑。

● Rotate Components 复选项:用于布局时对元件进行旋转调整。

● A u tomatic PCB Update 复选项:用于在布局中自动更新PCB 板。

● Power Nets 文本框:用于定义电源网络名称。

● Ground Nets 文本框:用于定义接地网络名称。

● Grid Size 文本框:用于设置格点大小。

如果选择Statistical Placer 单选项的同时,选中Automatic PCB Update 复选项,将在布局结束后对PCB 板进行自动元件布局更新。

VLSI自动布局布线(APR)设计实验教材大规模集成电路设计教学实验室前言在电子技术高速发展的今天,电子产品的应用领域日益广泛,小巧灵活的集成电路芯片以其体积小、成本低等特点普遍受到商家和消费者的宠爱,而这也给芯片设计者提出了更高的要求。

客户们希望IC芯片的功耗更低、速度更快、体积更小、性能更稳定、价格更便宜,更重要的是开发周期更短。

在微电子工艺技术不断推陈出新的同时,IC芯片的复杂程度也随之增加。

目前一些先进的处理器芯片已达到了8层金属立体布线,最小线宽也达到了深亚微米以下,可以说如果用手工布线的方式完成这么复杂的芯片几乎是不可能的。

另外,有许多工艺线厂家都提供经过验证的IP核和标准单元库,作为设计者没有必要每一个模块都亲历亲为,直接选用适当的IP来搭建自己的设计可以大大的缩短芯片面世的时间。

现在有许多EDA软件公司都开发了相应的EDA软件,借助快速的算法、简洁的操作来辅助IC设计师完成设计中繁重复杂的工作。

一个项目的成功与否与设计者对EDA软件的熟悉程度息息相关。

本书结合EDA软件的使用,讲述数字IC项目从设计到流片的整个过程,力求学员通过对本书的学习能够对数字IC设计的项目流程有一个清晰的认识、掌握一些常用EDA软件的使用方法。

鉴于作者的水平,书中若有不妥之处,请广大读者批评指正。

目 录第一章Sun Solaris操作系统的基本操作以及EDA软件Cadence 的基本结构1.1 硬件平台Sun工作站系统 (4)1.1.1 工作站登陆 (5)1.1.2 Solaris系统常用命令 (5)1.2 Cadence EDA产品简介 (7)第二章TOP-DOWN设计流程 (9)第三章 RTL级硬件描述语言源程序的Ambit综合 (12)3.1Ambit启动和文件输入 (12)3.2时序约束 (14)3.3 层次化与设计优化 (16)第四章 数字系统的自动布局布线流程 (18)4.1 SE环境启动及文件输入 (18)4.2 整体布局 (21)4.3 电源、地的布线 (24)4.4 单元放置 (25)4.5 布线 (27)附录 实验报告模板 (30)第一章Sun Solaris操作系统的基本操作以及EDA软件Cadence的基本结构随着集成电子技术的发展,数字系统的设计朝着容量大、功能强、体积小、重量轻的方向发展,在TOP-DOWN的设计流程里,除了系统的行为描述外,其余设计几乎都可以在人为控制下由EDA软件自动完成,从而大大的缩短系统的设计周期,提高竞争力。