数字电路技术时序逻辑电路分析(正式)总结

- 格式:ppt

- 大小:3.06 MB

- 文档页数:56

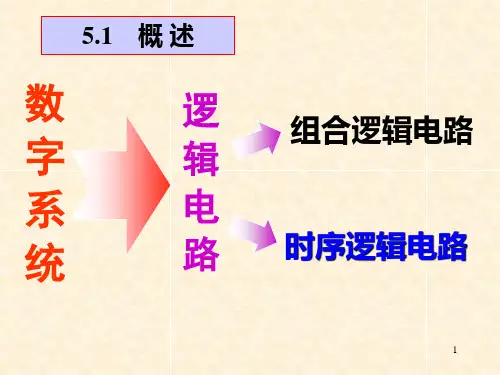

数电基础:时序逻辑电路虽然每个数字电路系统可能包含有,但是在实际应⽤中绝⼤多数的系统还包括,我们将这样的系统描述为时序电路。

时序电路是由最基本的加上反馈逻辑回路(输出到输⼊)或器件组合⽽成的电路,与最本质的区别在于时序电路具有记忆功能。

1. 简介是数字逻辑电路的重要组成部分,时序逻辑电路⼜称,主要由 存储电路 和 组合逻辑电路 两部分组成。

它和我们熟悉的其他电路不同,其在任何⼀个时刻的输出状态由当时的输⼊信号和电路原来的状态共同决定,⽽它的状态主要是由存储电路来记忆和表⽰的。

同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路⽽⾔,往往具有难度⼤、电路复杂并且应⽤范围⼴的特点 。

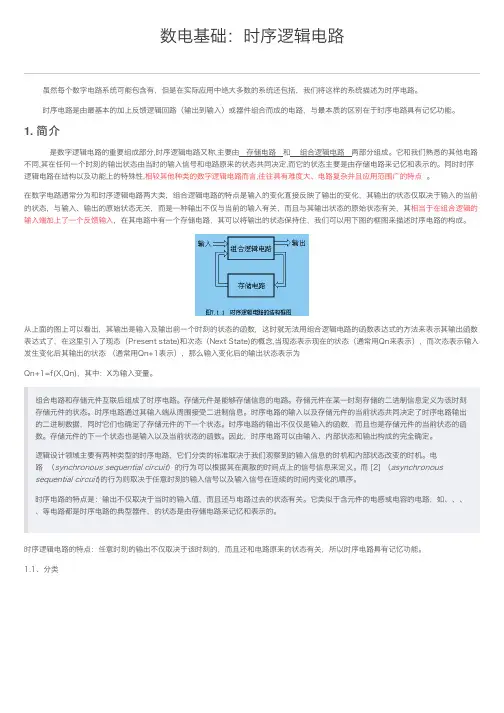

在数字电路通常分为和时序逻辑电路两⼤类,组合逻辑电路的特点是输⼊的变化直接反映了输出的变化,其输出的状态仅取决于输⼊的当前的状态,与输⼊、输出的原始状态⽆关,⽽是⼀种输出不仅与当前的输⼊有关,⽽且与其输出状态的原始状态有关,其相当于在组合逻辑的输⼊端加上了⼀个反馈输⼊,在其电路中有⼀个存储电路,其可以将输出的状态保持住,我们可以⽤下图的框图来描述时序电路的构成。

从上⾯的图上可以看出,其输出是输⼊及输出前⼀个时刻的状态的函数,这时就⽆法⽤组合逻辑电路的函数表达式的⽅法来表⽰其输出函数表达式了,在这⾥引⼊了现态(Present state)和次态(Next State)的概念,当现态表⽰现在的状态(通常⽤Qn来表⽰),⽽次态表⽰输⼊发⽣变化后其输出的状态 (通常⽤Qn+1表⽰),那么输⼊变化后的输出状态表⽰为Qn+1=f(X,Qn),其中:X为输⼊变量。

组合电路和存储元件互联后组成了时序电路。

存储元件是能够存储信息的电路。

存储元件在某⼀时刻存储的⼆进制信息定义为该时刻存储元件的状态。

时序电路通过其输⼊端从周围接受⼆进制信息。

时序电路的输⼊以及存储元件的当前状态共同决定了时序电路输出的⼆进制数据,同时它们也确定了存储元件的下⼀个状态。

时序逻辑电路实验报告总结

时序逻辑电路实验对于学习数字电路和计算机系统设计非常重要。

本次实验包括了基础的时序逻辑电路设计、时钟的设计、计数器和状态机等实验。

在实验过程中,我学习了如何使用Verilog进行时序逻辑电路设计,掌握了时序逻辑电路的思维方法和设计技巧。

本次实验需要我们使用FPGA进行验证,这为我们提供了设计的实时反馈。

在实验中,我学习了如何使用FPGA工具链进行开发和编程,了解了FPGA的工作原理和应用场景。

同时,我还了解到了不同类型的FPGA,如基于SRAM和基于FLASH的FPGA,并了解了它们的特点和应用。

总的来说,时序逻辑电路实验是一个非常重要的实验课程,它深入了解数字电路和计算机系统设计的基础原理和方法。

通过本次实验,我不仅掌握了基本的时序逻辑电路设计方法,还学会了使用FPGA开发工具进行电路开发和调试。

这对我今后的学习和工作都有很大的帮助。

时序逻辑电路报告心得体会时序逻辑电路是一种重要的逻辑电路设计方法,它能够对数字信号的状态和时序进行精确的控制和处理。

通过学习和实践,我对时序逻辑电路有了更深刻的理解,并且在报告中总结了以下的心得体会。

首先,时序逻辑电路能够实现复杂的功能。

通过组合逻辑门和时钟信号的组合,我们可以设计出各种各样的功能电路,如计数器、状态机等。

这些电路可以完成复杂的运算和控制任务,大大提高了电路的灵活性和可扩展性。

掌握时序逻辑电路设计的基本原理和方法,是电子工程师必不可少的能力之一。

其次,时序逻辑电路的设计需要考虑时序和时钟信号。

时序逻辑电路的设计是基于时钟信号的,时钟信号决定了电路的时序、稳定性和正确性。

在设计过程中,我们需要考虑时钟信号的频率、占空比和延时等因素,以确保电路的正确运行。

此外,时序逻辑电路还需要考虑时序逻辑的正确性,即确保电路在特定的时钟脉冲到来时,能够按照所需的时序进行操作。

再次,时序逻辑电路设计需要分析和优化。

在设计时序逻辑电路时,我们需要对电路的逻辑功能进行分析和优化,以提高电路的性能和效率。

通过使用适当的逻辑门、触发器和组合逻辑器件,我们可以减少电路的延时和功耗,提高电路的速度和稳定性。

此外,我们还可以通过优化时序逻辑电路的布局和连接方式,进一步提高电路的可靠性和可维护性。

最后,时序逻辑电路设计需要进行验证和测试。

设计好的时序逻辑电路需要进行验证和测试,以确保其功能和性能符合设计要求。

我们可以使用仿真软件进行电路的仿真和验证,检查电路的运行状态和波形,以及探索电路的健壮性和稳定性。

此外,我们还可以使用实际的硬件进行电路的测试,验证电路的实际运行情况和优化空间。

通过对时序逻辑电路的学习和实践,我深刻认识到了时序逻辑电路在数字电路设计中的重要性和应用广泛性。

掌握时序逻辑电路设计的基本原理和方法,对于电子工程师来说是非常重要的。

在今后的学习和工作中,我将继续深入学习时序逻辑电路的相关知识,不断提高自己的设计能力,以应对更为复杂的电路设计和工程问题。

实验五时序逻辑电路(计数器和寄存器)-实验报告一、实验目的1.掌握同步计数器设计方法与测试方法。

2.掌握常用中规模集成计数器的逻辑功能和使用方法。

二、实验设备设备:THHD-2型数字电子计数实验箱、示波器、信号源器件:74LS163、74LS00、74LS20等。

三、实验原理和实验电路1.计数器计数器不仅可用来计数,也可用于分频、定时和数字运算。

在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。

2.(1) 四位二进制(十六进制)计数器74LS161(74LS163)74LSl61是同步置数、异步清零的4位二进制加法计数器,其功能表见表5.1。

74LSl63是同步置数、同步清零的4位二进制加法计数器。

除清零为同步外,其他功能与74LSl61相同。

二者的外部引脚图也相同,如图5.1所示。

表5.1 74LSl61(74LS163)的功能表清零预置使能时钟预置数据输入输出工作模式R D LD EP ET CP A B C D Q A Q B Q C Q D0 ××××()××××0 0 0 0 异步清零1 0 ××D A D B D C D D D A D B D C D D同步置数1 1 0 ××××××保持数据保持1 1 ×0 ×××××保持数据保持1 1 1 1 ××××计数加1计数3.集成计数器的应用——实现任意M进制计数器一般情况任意M进制计数器的结构分为3类,第一类是由触发器构成的简单计数器。

第二类是由集成二进制计数器构成计数器。

第三类是由移位寄存器构成的移位寄存型计数器。

第一类,可利用时序逻辑电路的设计方法步骤进行设计。