时序逻辑电路的分析(二)

- 格式:ppt

- 大小:664.00 KB

- 文档页数:7

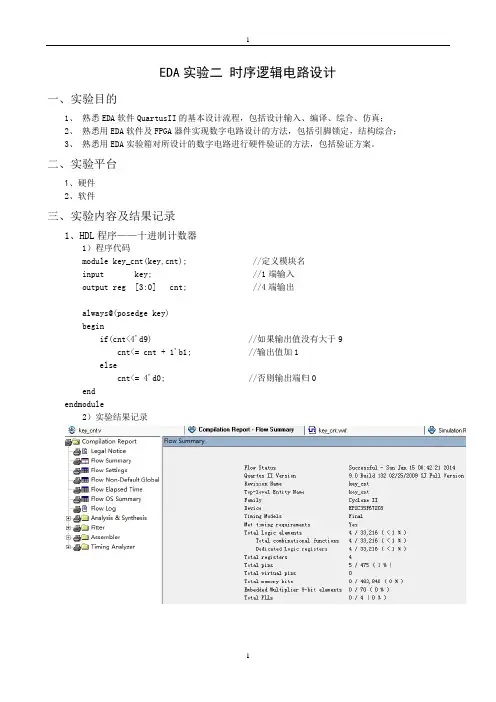

EDA实验二时序逻辑电路设计一、实验目的1、熟悉EDA软件QuartusII的基本设计流程,包括设计输入、编译、综合、仿真;2、熟悉用EDA软件及FPGA器件实现数字电路设计的方法,包括引脚锁定,结构综合;3、熟悉用EDA实验箱对所设计的数字电路进行硬件验证的方法,包括验证方案。

二、实验平台1、硬件2、软件三、实验内容及结果记录1、HDL程序——十进制计数器1)程序代码module key_cnt(key,cnt); //定义模块名input key; //1端输入output reg [3:0] cnt; //4端输出always@(posedge key)beginif(cnt<4'd9) //如果输出值没有大于9cnt<= cnt + 1'b1; //输出值加1elsecnt<= 4'd0; //否则输出端归0endendmodule2)实验结果记录表2.1输入输出A0 Q3 Q2 Q1 Q02、HDL程序——0-9的计数器1)程序代码module number(in,reset,data_out, dig); //模块定义input in,reset; //输入输出定义output [7:0] data_out;output [7:0] dig = 8'b11111110;reg [7:0] data_out;reg [3:0]count ;always @ (posedge in or negedge reset)beginif (!reset) //异步清零begindata_out <= 8'b1111111;count <= 0;endelsebegin count <=count + 1; //计数case (count) //七段译码器4'b0000: data_out = 8'b11000000; // 显示0 4'b0001: data_out = 8'b11111001; // 显示1 4'b0010: data_out = 8'b10100100; // 显示2 4'b0011: data_out = 8'b10110000; // 显示3 4'b0100: data_out = 8'b10011001; // 显示4 4'b0101: data_out = 8'b10010010; // 显示5 4'b0110: data_out = 8'b10000011; // 显示6 4'b0111: data_out = 8'b11111000; // 显示7 4'b1000: data_out = 8'b10000000; // 显示8 4'b1001: data_out = 8'b10011000; // 显示9 default:data_out <= 8'b11000000;endcaseendendendmodule2)实验结果记录表2.2输入输出A1 A0 数码管显示。

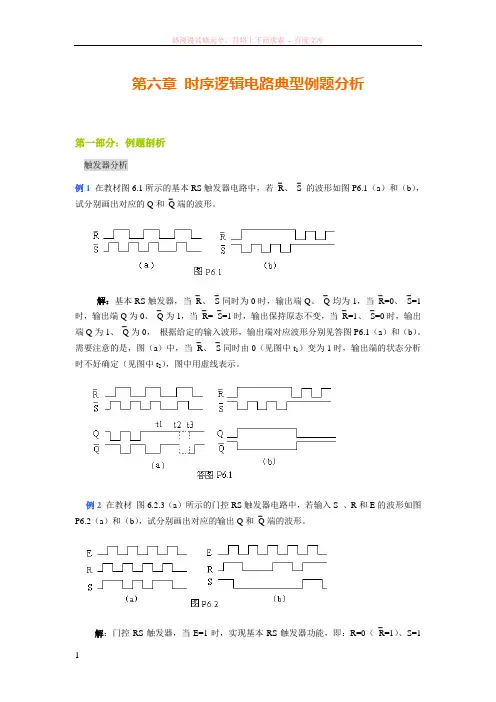

第六章时序逻辑电路典型例题分析第一部分:例题剖析触发器分析例1在教材图6.1所示的基本RS触发器电路中,若⎺R、⎺S 的波形如图P6.1(a)和(b),试分别画出对应的Q和⎺Q端的波形。

解:基本RS触发器,当⎺R、⎺S同时为0时,输出端Q、⎺Q均为1,当⎺R=0、⎺S=1时,输出端Q为0、⎺Q为1,当⎺R=⎺S=1时,输出保持原态不变,当⎺R=1、⎺S=0时,输出端Q为1、⎺Q为0,根据给定的输入波形,输出端对应波形分别见答图P6.1(a)和(b)。

需要注意的是,图(a)中,当⎺R、⎺S同时由0(见图中t1)变为1时,输出端的状态分析时不好确定(见图中t2),图中用虚线表示。

例2 在教材图6.2.3(a)所示的门控RS触发器电路中,若输入S 、R和E的波形如图P6.2(a)和(b),试分别画出对应的输出Q和⎺Q端的波形。

解:门控RS触发器,当E=1时,实现基本RS触发器功能,即:R=0(⎺R=1)、S=1(⎺S=0),输出端Q为1、⎺Q为0;R=1(⎺R=0)、S=0(⎺S=1)输出端Q为0、⎺Q为1;当E=0时,输出保持原态不变。

输出端波形见答图P6.2。

例3在教材图6.2.5所示的D锁存器电路中,若输入D、E的波形如图P6.3(a)和(b)所示,试分别对应地画出输出Q和Q端的波形。

解:D锁存器,当E=1时,实现D锁存器功能,即:Q n+1=D,当E=0时,输出保持原态不变。

输出端波形见答图P6.3。

例4在图P6.4(a)所示的四个边沿触发器中,若已知CP、A、B的波形如图(b)所示,试对应画出其输出Q端的波形。

设触发器的初始状态均为0。

解:图中各电路为具有异步控制信号的边沿触发器。

图(a)为边沿D触发器,CP上升沿触发,Q1n+1= A,异步控制端S D接信号C(R D=0),当C=1时,触发器被异步置位,输出Q n+1=1 ;图(b)为边沿JK触发器,CP上升沿触发,Q2n+1= A⎺Q2n +⎺BQ2n,异步控制端⎺R D接信号C(⎺S D =1),当C=0时,触发器被异步复位,输出Q n+1=0;图(c)为边沿D触发器,CP下降沿触发,Q3n+1= A,异步控制端⎺S D接信号C(⎺R D =1),当C=0时,触发器被异步置位,输出Q n+1=1;图(d)为边沿JK触发器,CP下降沿触发,Q4n+1= A⎺Q4n +⎺BQ4n,异步控制端R D接信号C(S D =0),当C=1时,触发器被异步复位,输出Q n+1=0。

时序逻辑和组合逻辑的详解

时序逻辑电路与组合逻辑电路是数字电路设计中的两种基本类型。

组合逻辑电路的输出仅取决于当前输入信号的状态,不依赖于过去或将来任何时刻的信号,其输出在输入变化后立即稳定。

例如,多路选择器、加法器等都属于组合逻辑电路。

而时序逻辑电路除了考虑当前输入外,还依赖于电路内部存储元件(如触发器)保持的历史状态信息,具有记忆功能。

它能够根据时钟信号控制数据的流入和流出,实现对信息的存储和延时处理。

如寄存器、计数器、移位寄存器等都是时序逻辑电路的例子。

通过时钟脉冲,这类电路能够在不同的时间点存储并更新数据,形成具有一定时间序列的操作流程。

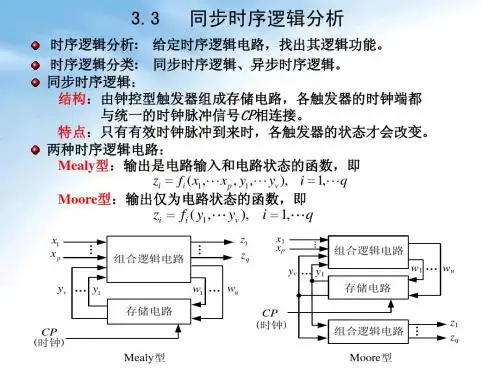

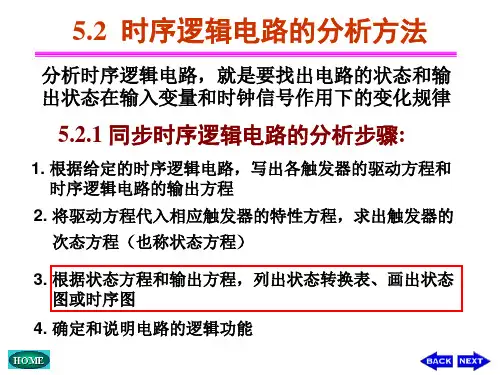

时序逻辑电路的分析方法1.时序图分析时序图是描述时序逻辑电路中不同信号随时间变化的图形表示。

时序图分析方法是通过绘制输入输出信号随时间变化的波形图,来观察信号之间的时序关系。

时序图分析的步骤如下:1)根据电路的逻辑功能,确定所需的时钟信号和输入信号。

2)根据电路的逻辑关系,建立出波形图的坐标系,确定时间轴和信号轴。

3)按照时钟信号的不同变化情况(上升沿、下降沿),在波形图中绘制相应的路径。

4)观察各个信号之间的时序关系,分析电路的逻辑功能和输出结果。

时序图分析方法的优点是直观、简单,可以清楚地显示信号的时序关系。

但它对于复杂的电路设计来说,图形绘制和分析过程相对繁琐,需要一定的经验和技巧。

2.状态表分析状态表分析方法是通过定义不同输入信号下的状态转移关系,来描述时序逻辑电路的行为。

状态表可以用表格的形式表示,其中包含了输入信号、当前状态、下一个状态和输出信号等信息。

状态表分析的步骤如下:1)根据电路的逻辑功能和输入信号,列出电路的状态转移关系。

2)构建状态表,定义不同输入信号下的状态转移关系和输出信号。

3)根据状态表,逐步推导出电路的状态转移路径和输出结果。

状态表分析方法的优点是逻辑严谨、结构清晰,适用于对于复杂的状态转移关系进行分析和设计。

但它对于大规模的电路设计来说,状态表会非常庞大,而且容易出现错误,需要仔细的计算和推导。

3.状态图分析状态图分析方法是通过绘制状态转移图,来描述时序逻辑电路中状态之间的转移关系。

状态图是由状态、输入信号、输出信号和状态转移路径等构成。

状态图分析的步骤如下:1)根据电路的逻辑功能和输入信号,确定电路的状态和状态转移关系。

2)构建状态图,按照状态的转移路径和输入信号绘制状态图。

3)根据状态图,分析电路的逻辑功能和输出结果。

状态图分析方法的优点是直观、清晰,可以清楚地描述状态之间的转移关系。

它可以帮助设计者对于电路的状态转移关系进行分析和调试。

但状态图也会随着电路规模的增大而变得复杂,需要仔细分析和理解。

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。