CPLD模块及接口说明

- 格式:doc

- 大小:644.50 KB

- 文档页数:9

基于CPLD的DSP系统接口设计中文摘要本论文详细介绍了基于CPLD的DSP系统接口设计的方案与实现方法。

在本次设计过程中,主要是以模块思想来设计整个DSP系统。

在整个硬件系统设计中,以DSP芯片为核心,用CPLD来实现控制数据中转、与外围设备的通信。

本论文介绍了如何利用CPLD设计并实现TMS320C5416芯片与SRAM、FLASH、串并转换器等外围设备之间的接口,即利用了CPLD 实现TMS320C5416系统接口的扩展。

关键词:DSP;系统接口; CPLDDesign DSP system connection with CPLDAbstractThe present paper in detail introduced the DSP system connection of based on the CPLD designs plan and the realization method. In this design process, mainly designs the entire DSP system by the module of thought.In the entire hardware system design process, takes the DSP chip as the core, realizes the control data relay by the CPLD decoding, and the auxiliary equipment correspondence. This introduced how switching using CPLD connection designs the between TMS320C5416 chip and SRAM, FLASH, string and auxiliary equipment and so on, namely used CPLD to design the TMS320C5416 system connection the expansion.Key words: DSP ; The interface of system ;CPLD第一章:绪论§1.1 课题的提出及意义随着信息化技术的飞速发展,各种便携式电子产品和个人助理不断涌现,但是,许多消费电子的采集处理系统有着自身的不足,采集装置的复杂化,图像实时处理对处理器的依赖,图像处理系统的造价、速度及体积都成为限制图像技术应用的瓶颈。

实验一 CPLD 可编程数字信号发生器实训一、实验目的1、熟悉各种时钟信号的特点及波形;2、熟悉各种数字信号的特点及波形。

二、实验设备与器件1、通信原理实验箱一台;2、模拟示波器一台。

三、实验原理1、CPLD 可编程模块电路的功能及电路组成CPLD可编程模块(芯片位号:U101)用来产生实验系统所需要的各种时钟信号和数字信号。

它由 CPLD可编程器件 ALTERA公司的 EPM7128(或者是Xilinx 公司的 XC95108)、编程下载接口电路(J104)和一块晶振(OSC1)组成。

晶振用来产生系统内的16.384MHz 主时钟。

本实验要求参加实验者了解这些信号的产生方法、工作原理以及测量方法,才可通过CPLD可编程器件的二次开发生成这些信号,理论联系实践,提高实际操作能力,实验原理图如图1-1 所示。

2、各种信号的功用及波形CPLD 型号为 EPM7128 由计算机编好程序从 J104 下载写入芯片,OSC1 为晶体,频率为 16.384MHz,经 8 分频得到 2.048MHz 主时钟,面板测量点与EPM7128 各引脚信号对应关系如下:SP101 2048KHz 主时钟方波对应 U101EPM7128 11 脚SP102 1024KHz 方波对应 U101EPM7128 10 脚SP103 512KHz 方波对应 U101EPM7128 9 脚SP104 256KHz 方波对应 U101EPM7128 8 脚SP105 128KHz 方波对应 U101EPM7128 6 脚SP106 64KHz 方波对应 U101EPM7128 5 脚SP107 32KHz 方波对应 U101EPM7128 4 脚SP108 16KHz 方波对应 U101EPM7128 81 脚SP109 8KHz 方波对应 U101EPM7128 80脚SP110 4KHz 方波对应 U101EPM7128 79脚SP111 2KHz 方波对应 U101EPM7128 77脚SP112 1KHz 方波对应 U101EPM7128 76脚SP113 PN32KHz 32KHz伪随机码对应U101EPM7128 75脚SP114 PN2KHz 2KHz伪随机码对应U101EPM7128 74脚SP115 自编码自编码波形,波形由对应 U101EPM7128 73 脚J106 开关位置决定SP116 长 0 长 1 码码形为1、0 连“1”对应 U101EPM7128 70脚、0 连“0”码SP117 X 绝对码输入对应 U101EPM7128 69 脚SP118 Y 相对码输出对应 U101EPM7128 68 脚SP119 F80 8KHz0 时隙取样脉冲对应 U101EPM7128 12 脚此外,取样时钟、编码时钟、同步时钟、时序信号还将被接到需要的单元电路中。

CPLD的基本结构1.基于乘积项的CPLDCPLD (Complex Programmable Logic Device)直译的话称为复杂可编程逻辑芯片。

它也属于大规模集成电路LSI (Large Scale Integrated Circuit)里的专用集成电路ASIC (Application Specific Integrated Circuit)。

适合控制密集型数字型数字系统设计,其时延控制方便.CPLD是目前集成电路中发展最快的器件之一。

结构C PLDPLD即programmable logic device,译为可编程逻辑器件,是一个可以产生任意逻辑输出的通用型数字逻辑电路器件。

PLD有很高的集成度,足以满足设计一般的数字系统的需要,与门、或门、非门是PLD最基本的构成。

的结构是基于乘积项(Product-te rm)的,现在以Xilinx公司的XC9500XL 系列芯片为例介绍CPLD的基本结构,如图1所示,其他型号CPLD的结构与此非常类似。

CPLD可分为3部分:功能模块(Functi ON Block)、快速互连矩阵(FastCON NEC T ⅡSwitch Matrix)和I/O控制模块.每个功能模块包括可编程与阵列、乘积项分配器分配器是有线电视传输系统中分配网络里最常用的部件,用来分配信号的部件.它的功能是将一路输入信号均等地分成几路输出,通常有二分配、三分配、四分配、六分配等。

有线电视网的频率不断提升,功能不断加强,因此对分配器的要求不断提高。

在接口设备上分配器是将音视频信号分配至多个显示设备或投影显示系统上的一种控制设备。

它是专门分配信号的接口形式的设备。

[全文]和18个宏单元,功能模块的结构如图2所示。

快速互连矩阵负责信号传递,连接所有的功能模块.I/O控制模块负责输人输出的电气特性控制,比如可以设定集电极开路输出、三态输出等。

图1中的I/O/GCK,I/O/GSR,1/0/GTS 是全局时钟、全局复位和全局输出使能信号,这几个信号有专用连线与CPLD中每个功能模块相连,信号到每个功能模块的延时相同并且延时最短。

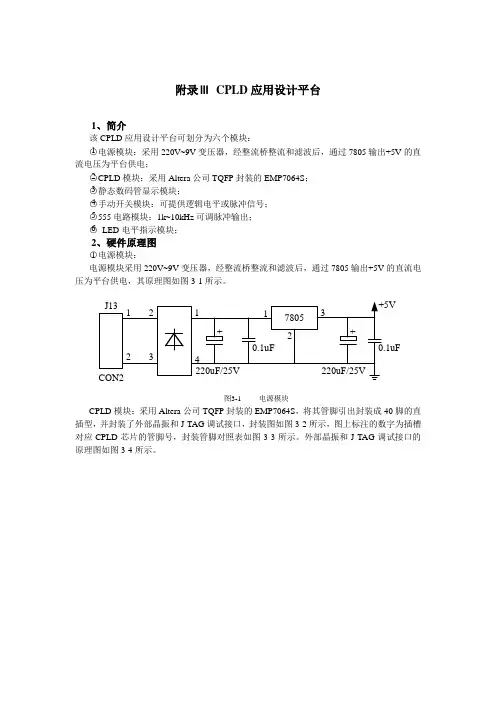

附录ⅢCPLD应用设计平台1、简介该CPLD应用设计平台可划分为六个模块:○1电源模块:采用220V~9V变压器,经整流桥整流和滤波后,通过7805输出+5V的直流电压为平台供电;○2CPLD模块:采用Altera公司TQFP封装的EMP7064S;○3静态数码管显示模块;○4手动开关模块:可提供逻辑电平或脉冲信号;○5555电路模块:1k~10kHz可调脉冲输出;○6LED电平指示模块;2、硬件原理图○1电源模块:电源模块采用220V~9V变压器,经整流桥整流和滤波后,通过7805输出+5V的直流电压为平台供电,其原理图如图3-1所示。

图3-1电源模块CPLD模块:采用Altera公司TQFP封装的EMP7064S,将其管脚引出封装成40脚的直插型,并封装了外部晶振和J-TAG调试接口,封装图如图3-2所示,图上标注的数字为插槽对应CPLD芯片的管脚号,封装管脚对照表如图3-3所示。

外部晶振和J-TAG调试接口的原理图如图3-4所示。

图3-2封装图图3-3封装管脚对照表图3-4外部晶振和J-TAG调试接口○3数码管显示模块,采用共阳极数码管静态显示,用74LS47译码和驱动参阅第4章。

在图3-5中,将最高位的74LS47的/RBI接地,/BI/RBO接到低一位的/RBI引脚,最低位/BI/RBO接高电平,这样级联即可实现灭零显示。

图3-5数码管显示模块○4逻辑开关模块:采用RS触发器74LS279从而消抖并提供逻辑电平或脉冲信号,如图3-6所示,逻辑开关模块如图3-7所示。

图3-6 74LS279管脚图图3-7逻辑开关模块○5555电路模块:555电路模块可实现1k~10kHz 可调脉冲输出,其原理图如图3-8所示。

图中,R A =10k,R B =50k(可调电位器),输出频率范围1k~10kHz 可调脉冲输出。

+V CCR BC 17U +5VU +5V U +5V U +5V 图3-8 555电路模块图3-9 LED 模块○6LED 模块,低电平时点亮,如图3-9所示。

博创科技经典平台CPLD接口说明2011-1-10经典平台上有两片CPLD,第1片控制网卡、IDE的逻辑、串口选择、CF卡逻辑等。

第2片控制音频和触摸屏选择、LED矩阵和数码管等。

对软件而言,两片CPLD可以看作同一外设,有的寄存器分开放在两片CPLD内的。

如无特别说明,S3C2440核心板所对应的地址分配和S3C2410核心板完全相同。

一、网卡、IDE、复位等逻辑和原来经典平台一样,对软件透明,无需设置。

1、网卡1和网卡2,对于270和2410核心板,都在Bank2上。

当nGCS2为0时,A2为0则选中网卡1,A2为1则选中网卡2。

对于每个网卡芯片,A1为0访问INDEX端口,A1为1访问DATA端口。

物理地址:2410核心板:网卡1:INDEX:0x1000 0000 DATA::0x1000 0002网卡2:INDEX:0x1000 0004 DATA::0x1000 0006 270核心板:网卡1:INDEX:0x0800 0000 DATA::0x0800 0002网卡2:INDEX:0x0800 0004 DATA::0x0800 00062、IDE接口和其他一些资源占用同一个Bank,2410核心板是Bank1,270核心板是Bank4。

当A8为0时选中IDE接口,A8为1时选中其他资源,后面逐步说明。

物理地址范围:2410核心板:IDE接口:0x0800 0000---0x0800 00FF其他设备:0x0800 0100---0x0800 011E270核心板: IDE接口:0x1000 0000---0x1000 00FF其他设备:0x1000 0100---0x1000 011E3、复位逻辑仅提供各复位电平之间的逻辑与关系。

二、CPLD内部包括核心板选择寄存器,并据此对音频和触摸屏等资源进行选择,以及控制串口选择的寄存器,数码管和矩阵LED寄存器,还有270核心板下的CF卡相关寄存器。

CPLD和FPGA内部结构和原理1.CPLD的内部结构和原理:CPLD中的主要组件是可编程逻辑单元(PLU),每个PLU中包含了多个可编程逻辑阵列(PLA),以及用于配置逻辑功能的多个存储器单元。

每个PLA都包含了输入寄存器、多个AND门和一个OR门。

当CPLD需要实现一些逻辑功能时,相关的逻辑门将被编程为特定的功能,并在PLU中通过可编程互连的方式连接起来。

此外,CPLD通常还包含时钟管理单元、输入/输出单元和可编程的信号延迟单元。

CPLD的工作原理如下:1) 配置:在设计过程中,使用者将所需逻辑功能转换为硬件描述语言(如VHDL或Verilog),然后通过设计工具将其编译为CPLD可接受的配置文件。

配置文件将存储在CPLD的非易失性存储器中(通常是闪存或EEPROM)。

2)启动:当CPLD上电时,其中的配置文件会被加载到可编程逻辑单元中,使CPLD实现所需的逻辑功能。

3)运行:一旦CPLD成功配置,它将按照配置文件中定义的逻辑功能来处理输入信号,并在输出端口提供相应的输出信号。

CPLD还可以通过重配置来支持动态更新设计,以满足不同的应用需求。

2.FPGA的内部结构和原理:FPGA由海量的可编程逻辑单元和可编程互连网络组成。

可编程逻辑单元由可编程逻辑阵列(Look-Up Table,LUT)和触发器组成,用于实现具体的逻辑功能。

可编程互连网络通过配置跨可编程逻辑单元的信号路径实现不同模块之间的连接。

FPGA的工作原理如下:1)配置:同样,设计者使用硬件描述语言编写逻辑功能描述,并通过设计工具将其编译为FPGA可接受的配置文件。

配置文件存储在FPGA的非易失性存储器中。

2)启动:当FPGA上电时,配置文件会被加载到FPGA的可编程逻辑单元和可编程互连网络中,以实现所需的逻辑功能。

3)运行:一旦FPGA成功配置,它将按照配置文件中定义的逻辑功能来处理输入信号,并在输出端口提供相应的输出信号。

FPGA还可以支持动态重配置,即在运行时重新配置FPGA以改变逻辑功能。

CPLD 实现SPI 接口1 实现原理CPLD 实现SPI 接口模块,通过对寄存器的操作,实现SPI 接口功能,对外部SPI 设备进行访问。

CPLD 内部SPI 模块逻辑框图如下所示。

CLK_DIVRX_SHIFT_REGSTATUS LOGICspi_clkspi_cs spi_dospi_tx_data_we_pulsereset_n spi_tx_data spi_rx_data spi_clk_div spi_rx_data_rd_pulsespi_dispi_tx_data_we_busy spi_rx_data_rd_ready spi_data_tx_we_overflow spi_data_rx_rd_nop spi_data_rx_rd_overtime cpld_clkCONTROL LOGICCOUNT LOGIC通过对主时钟分频,得到的SPI 接口时钟,其分频值可通过spi_clk_div 值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI 接口的片选信号spi_cs 在写数据传输寄存器spi_tx_data 时,通过自动产生写脉冲spi_tx_data_we_pulse ,逻辑综合生成。

spi_rx_data_rd_pulse 在读取接收数据spi_rx_data 的数据时自动产生。

spi_di 和spi_do 分别由数据移位寄存器通过数据移位产生和接收。

spi_clk 由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy 信号分别表示数据正在传输,无法写入spi_tx_data 寄存器; spi_rx_data_rd_ready 信号表示数据接收完成,可读取spi_rx_data 寄存器的值。

错误状态逻辑spi_data_tx_we_overflow 信号表示在spi_tx_data 寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

CPLD的基本结构1.基于乘积项的CPLDCPLD (Complex Programmable Logic Device)直译的话称为复杂可编程逻辑芯片。

它也属于大规模集成电路LSI (Large Scale Integrated Circuit)里的专用集成电路ASIC (Application Specific Integrated Circuit)。

适合控制密集型数字型数字系统设计,其时延控制方便。

CPLD是目前集成电路中发展最快的器件之一。

结构C PLDPLD即programmable logic device,译为可编程逻辑器件,是一个可以产生任意逻辑输出的通用型数字逻辑电路器件。

PLD有很高的集成度,足以满足设计一般的数字系统的需要,与门、或门、非门是PLD最基本的构成。

的结构是基于乘积项(Product-te rm)的,现在以Xilinx公司的XC9500XL 系列芯片为例介绍CPLD的基本结构,如图1所示,其他型号CPLD的结构与此非常类似。

CPLD可分为3部分:功能模块(Functi ON Block)、快速互连矩阵(FastCON NEC T ⅡSwitch Matrix)和I/O控制模块。

每个功能模块包括可编程与阵列、乘积项分配器分配器是有线电视传输系统中分配网络里最常用的部件,用来分配信号的部件。

它的功能是将一路输入信号均等地分成几路输出,通常有二分配、三分配、四分配、六分配等。

有线电视网的频率不断提升,功能不断加强,因此对分配器的要求不断提高。

在接口设备上分配器是将音视频信号分配至多个显示设备或投影显示系统上的一种控制设备。

它是专门分配信号的接口形式的设备。

[全文]和18个宏单元,功能模块的结构如图2所示。

快速互连矩阵负责信号传递,连接所有的功能模块。

I/O控制模块负责输人输出的电气特性控制,比如可以设定集电极开路输出、三态输出等。

图1中的I/O/GCK,I/O/GSR,1/0/GTS 是全局时钟、全局复位和全局输出使能信号,这几个信号有专用连线与CPLD 中每个功能模块相连,信号到每个功能模块的延时相同并且延时最短。

第二章CPLD硬件系统介绍

2.1 系统总体介绍

本课程设计所采用的CPLD硬件开发板分为六个功能模块:LED发光二极管阵列、8*8LED阵列、步进电机驱动电路、串口、数码管以及指拨开关。

这几种功能模块单独使用或结合在一起使用可实现多种功能。

其硬件实物图如图2-1所示。

图2-1 CPLD开发板硬件实物图

2.2 功能模块介绍

1、LED发光二极管阵列

发光二极管阵列由红、黄、绿三种不同颜色的发光二极管组成,可实现流水灯功能,结合数码管可实现交通灯功能,其硬件实物图如图2-2所示:

图2-2 发光二极管阵列硬件实物图。

信源和AMI/HDB3编译码模块中的CPLD功能说明TX-6B型实验设备中,信源模块的分频器、三选一、倒相器、抽样等单元以及AMI/HDB3编译码模块的编译码单元的功能由一片CPLD(复杂可编程逻辑器件)完成。

硬件上选用了Altera公司的EPM7064芯片(或其全兼容芯片-ATMEL公司的ATF1504AS),该芯片是ALTERA 公司MAX7000系列的产品,内有64个宏单元,具有速率高、可多次擦写等特点,设计上采用VHDL语言编写源程序。

其引脚设定如图附1.1所示,其引脚封装图如图附1.2所示。

图附1.1 信源部分CPLD引脚设定图AMI/HDB3编译码子单元完成AMI/HDB3编译码功能,其设定的引脚有:· NRZ-IN 编码器NRZ信号输入端,接信源模块的输出信号NRZ-OUT,已在印刷电路板上连好· BS-IN 编码时钟(位时钟信号)输入端,接信源模块的位时钟输出信号BS-OUT,已在印刷电路板上连好· HDB3/AMI 码型选择端,接高电平时选择HDB3码;接低电平时选择AMI码(由拨动开关K4控制)· +HDB3-OUT HDB3编码器正码输出端,接到AMI/HDB3模块中单双极性变换器单元的输入端,已在印刷电路板上连好· -HDB3-OUT HDB3编码器负码输出端,接到AMI/HDB3模块中单双极性变换器单元的输入端,已在印刷电路板上连好· +HDB3-IN HDB3译码器正码输入端,接AMI/HDB3模块中单双极性变换器单元的输出信号,已在印刷电路板上连好· -HDB3-IN HDB3译码器负码输入端,接AMI/HDB3模块中单双极性变换器单元的输出信号,已在印刷电路板上连好· BS-R 译码时钟(位同步信号)输入端,接AMI/HDB3模块中锁相环单元的输出信号BS,已在印刷电路板上连好· NRZ AMI/HDB3译码后信息码输出端信源子单元完成图1.1所示信源模块的分频器、三选一、倒相器及抽样电路等单元的功能,其设定的引脚有:· CLK 信源子单元时钟输入端· S1、S2、S3 3个选通信号的输入端,这三个信号的频率分别为位时钟信号的1/2、1/4和1/8· Z0、Z1、Z2 三选一单元的三个输入信号的输入端,这三个输入信号分别接三个八选一单元的输出信号,已在印刷电路板上连好· NRZ1 NRZ信号输出端· FS1帧时钟信号输出端· BS 位时钟信号输出端CPLD除了完成上述功能外,还包含一个M序列子单元,其输出的伪随机码M序列送给数字调制模块,以便在2DPSK解调实验中观察到眼图。

5分钟学会使用CPLD当今社会,随着电子行业的发展,大规模集成电路的运用越来越普遍,用CPLD/FPGA 来开发新产品是当前很多实际情况的需求。

在此本人结合到自己的所学,利用业余时间草写了一个简单的使用说明,不要求有丰富经验的大虾来驻足观望,只希望对吾辈刚入门的菜鸟们起到一个抛砖引玉的作用。

由于水平有限,文中错误在所难免,望各位提出宝贵的意见。

1.首先请准备一套简单的CPLD原理图。

在此我们准备了如下所示的简单一个系统图。

晶体用10M的有源晶体,可以在线下载的JTAG接口。

电源用5转3.3V的电源模块AS1117。

1个1K的排阻。

8个发光管在程序运行时轮流点亮。

2.安装XILINX的集成编译软件ISE5.0或6.0。

因为ISE在运行时比较消耗计算机的内存,所以要求计算机配置符合相关的要求,高一点的配置,不至于在运行时死机。

3.准备一小段verilog hdl编写一段小代码,主要用来验证系统板的正确。

其中也可以用VHDL来编写,考虑到verilog hdl比较接近C语言,对初级学者来说,相对所花时间较短,上手较快。

在此我推荐学verilog hdl。

具体的参考书可以看下面的提示:4.此我们用下面的一小段代码作为范例:其功能是驱动8个发光管轮流点亮,因为是采用了10M频率晶体的边沿触发,所以速度很快,为了使我们肉眼能够看的清楚其工作的流程,我们在里面安放了一个计数器,计数器计每次满一次就点亮一个发光管,依次类推。

其源程序如下:/* 流水灯的Verilog-HDL描述*/module LEDWATER(reset,CLK,LED);input reset, CLK;output [7:0] LED;reg [7:0] LED;//=8'b11111111;reg [17:0] buffer;//=0;reg exchange;always@(posedge CLK)if(reset==0) //如果复位了就熄灭全部的灯beginLED=8'b1111_1111;buffer=0;exchange=0;endelsebeginif (exchange==0)beginbuffer=(buffer +1);if ( buffer == 17'b111111111111111111111111)beginbuffer=0;LED=(LED-1);if(LED==8'b0000_0000)beginLED=8'b1111_1111;exchange=1;endendendif(exchange==1)beginbuffer=(buffer +1);if ( buffer == 17'b111111111111111111111111)beginbuffer=0;LED=(LED>>1);if(LED==8'b00000000)beginLED=8'b1111_1111;exchange=0;endendendendendmodule注意:VERILOG HDL的代码编写风格,begin end 代替了C语言中的大括号{}。

CPLD系统模块及接口说明

F.1 概述

模块结构框图如图F.1-1所示。

CPLD采用Altera新一代的MAXII器件EPM570T100C5,配合QuartusII可以很容易实现CPLD的开发,模块具有4位键盘输入、4位开关量输入,8个动态LED显示,1个静态LED显示,8个发光管,1个蜂鸣器,用于完成实验,同时引出了3.3V的IO口,方便模块的扩展。

程序下载方法采用ByteBlaster,本模块下载时,插上跳线帽JP214~JP217;其他模块下载时拔下跳线帽JP214~JP217。

图F.1-1 CPLD系统模块框图

F.2 电路说明

F.2.1 ByteBlasterⅡ下载电路

本模块的ByteblasterII下载电路图如图F.2-1,通过25针计算机并口进行。

整个实验箱系统共有3块FPGA/CPLD模块,均通过本模块ByteblasterII 口进行程序下载。

注意:本模块下载程序时,插上JP214~JP217跳线帽。

其他模块通过本ByteblasterII口下载程序时,拔下JP214~JP217跳线帽。

图F.2-1 ByteblasterII下载电路图

F.2.2 数码管驱动缓冲电路

MAXII器件为低电压器件采用3.3V供电,一般采用一级缓冲和5V的外设相连接。

图F.2-2给出数码管驱动缓冲电路。

8位动态数码管的段由U202驱动,位由U203驱动。

1位静态数码管由U204驱动。

图F.2-2数据缓冲电路

F.2.3 键盘、开关量输入及发光管显示

本模块设有4位键盘输入(也可由跳线JP206~JP209选择TP201~TP204输出,见表F.3-9),4位开关量输入及8位发光管输出。

键盘输入为负脉冲。

图F.2-3键盘、开关量输入及发光管电路

F.3 接口说明

F.3.1 总线接口(JT201)

总线接口JT201定义见表F.3-1。

F.3.2 键盘输入接口(K201~K203)

表F.3-2是键盘K201~K204接口表。

F.3.3开关量输入接口(S205~S207)

表F.3-3是开关量输入S205~S208接口表。

F.3.4 发光管输出(D201~D208)

表F.3-4是发光管输出D201~D208接口表。

F.3.5 静态显示数码管(LED201)

表F.3-5是静态数码管接口表。

F.3.6 动态显示数码管(LED202~LED203)

表F.3-6是动态数码管接口表。

F.3.7 蜂鸣器引脚BEEP201

表F.3-7是蜂鸣器接口表。

F.3.8 跳线说明

F.3.8.1 下载模块选择跳线JP214~JP217

整个实验箱系统共有3块FPGA/CPLD模块,均通过本模块的ByteblasterII口进行程序下载。

表F.3-8给出下载模块选择跳线说明。

F.3.8.2 键盘输入/输出选择跳线JP206~JP209

CPLD的27、28、29及30引脚,可作为键盘K201~K204的输入,也可通过TP201~TP204输出。

具体通过跳线JP206~JP209进行选择,如表F.3-9。

F.3.8.3 JP210~JP213跳线说明

CPLD的75、74、73、72引脚可作为TP205~TP208输出,也可连接总线中的A0~A3。

具体通过跳线JP210~JP213选择,如表F.3-10。

F.3.9 时钟输入

模块内部含有时钟电路,频率为50MHz,由EPM570T100C的第62引脚输入。

如表F.3-11。

F.3.10 电源输入方式

本模块电源输入方式有如下两种:

(1) PW202为外部12V电源输入(内正外负),可用于单板使用;

(2) PW201为实验箱12V电源输入。