Verilog实验全加器与比较器的设计

- 格式:doc

- 大小:120.50 KB

- 文档页数:5

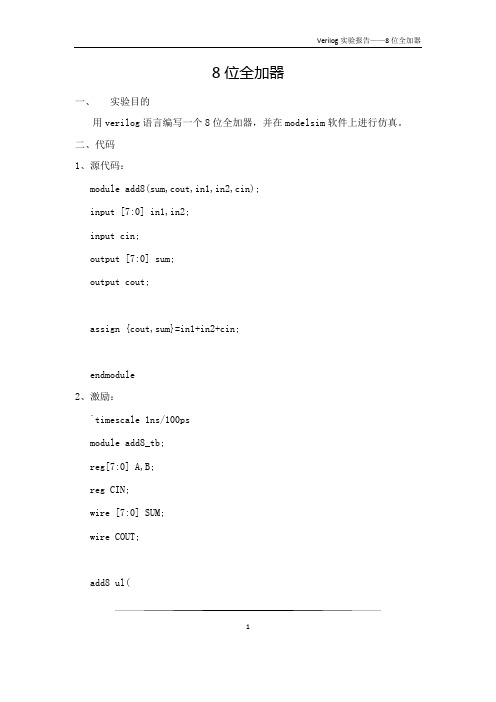

8位全加器一、实验目的用verilog语言编写一个8位全加器,并在modelsim软件上进行仿真。

二、代码1、源代码:module add8(sum,cout,in1,in2,cin);input [7:0] in1,in2;input cin;output [7:0] sum;output cout;assign {cout,sum}=in1+in2+cin;endmodule2、激励:`timescale 1ns/100psmodule add8_tb;reg[7:0] A,B;reg CIN;wire [7:0] SUM;wire COUT;add8 ul(1.sum(SUM),.cout(COUT),.in1(A),.in2(B),.cin(CIN));initialbeginA=8'd0;B=8'd0;CIN=1'b0;#10 A=8'd20;B=8'd129;CIN=1'b1; #10 A=8'd27;B=8'd19;CIN=1'b0; #10 A=8'd157;B=8'd29;CIN=1'b0; #10 A=8'd37;B=8'd68;CIN=1'b0; #10 A=8'd11;B=8'd69;CIN=1'b0; #10 A=8'd54;B=8'd67;CIN=1'b1; #10 A=8'd211;B=8'd0;CIN=1'b0; #10 A=8'd87;B=8'd43;CIN=1'b1; #10 A=8'd23;B=8'd171;CIN=1'b0; #10 A=8'd12;B=8'd12;CIN=1'b1; #10 A=8'd112;B=8'd115;CIN=1'b0; endendmodule23三、实验过程1、上机过程2、仿真波形3、波形说明波形图中,从上至下依次为:输入加数A、输入加数B、输入进位CIN、输出进位COUT、输出和SUM。

实验四四位全加器一、实验目的l. 用组合电路设计4位全加器。

2.了解Verilog HDL语言的行为描述的优点。

2、实验原理4位全加器工作原理1)全加器除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

被加数Ai、加数Bi从低位向本位进位Ci-1作为电路的输入,全加和Si与向高位的进位Ci作为电路的输出。

能实现全加运算功能的电路称为全加电路。

全加器的逻辑功能真值表如表中所列。

2)1位全加器一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin;Co=AB+BCin+ACin其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;这两幅图略微有差别,但最后的结果是一样的。

3)4位全加器4位全加器可看作4个1位全加器串行构成, 具体连接方法如下图所示:采用Verilog HDL语言设计该4位全加器,通过主模块调用子模块(1位全加器)的方法来实现。

3、实验步骤四、实验连线K1-K4:14-11K5-K8:18-15L5-L8:7-10VIJN:83L4:64KHZ:805、心得体会首先,实现这一段全加器代码并不难,但是由于困惑给的三个时钟输入,没有太懂意思,所以只写了全加器控制LED灯的代码;后来问清楚后,运行全加器代码,有错误,原来是建文件时用的是verilog hdl,我建的是其他类型的;后来还有错,原来是把冒号打成分号;编译成功后,LED不亮,后来发现是硬件老化,换了箱子。

这一部分做好后,我准备把控制声音的加上去,本来准备再加一个模块,可是不能有两个顶层块,就对主模块做了补充,用case命令调用不同的状态,因为时间紧迫,所以代码写得比较简单,没有用经典的分频代码。

这里附一小段,是我在研究分频控制时看懂的网上的经典分频代码,适合乐曲自动播放等高级的实现,仅供分享assign preclk=(divider==16383)?1:0;//divider==16383,preclk=1always @(posedge clk) //基频上升沿触发beginif(preclk) //preclk=1divider=origin;elsedivider=divider+1;endalways @(posedge preclk) //调整占空比beginspeaker=~speaker; //2 分频产生方波信号end这部分实现了分频功能,其中origin+divider=16384=2^14,这个数根据自己的需要而定。

verilog全加器实验报告Verilog-全加器上机实验报告西安邮电學院基于Verilog的HDL设计基础实验报告学院名称 :学生姓名 : 专业名称 :班级 : 学时通信与信息工程学院通信工程号 : 间 :2010年11月24日实验题目全加器一、实验内容对一位二进制全加器的设计与验证;再对其进行综合生成网表文件;然后进行后仿真。

二、技术规范1、输入引脚: a,b,c_in;输出引脚:sum,c_out。

2、功能:这是一位二进制全加器。

a,b为输入的两个二进制加数,c_in为低位向本位的借位,sum为全加和,c_out为本位向高位的进位。

三、实验步骤1、在modulesim软件中进行两个一位二进制数的全加器的设计与验证,直到运行结果全部正确;2、在Quartus软件中对刚刚完成的计数器进行综合,生成网表文件;3、在modulesim软件中对计数器进行进行后仿真。

四、源代码1. 设计模块:module Count4(sum,c_out,a,b,c_in);output [3:0] sum;output c_out;input [3:0] a,b;input c_in;wire c1,c2,c3;Count Ca0(sum[0],c1,a[0],b[0],c_in);Count Ca1(sum[1],c2,a[1],b[1],c1);Count Ca2(sum[2],c3,a[2],b[2],c2);Count Ca3(sum[3],c_out, a[3],b[3],c3); Endmodulemodule Count(sum, c_out,a,b,c_in);output sum,c_out;input a,b,c_in;wire s1,c1,c2;xor(s1,a,b);and(c1,a,b);xor(sum,s1,c_in);and(c2,s1,c_in);xor(c_out,c2,c1);endmodule2.激励模块:module jili;reg [3:0] A, B;reg C_IN;wire [3:0] SUM ;wire C_OUT;Count4 CT_4(SUM,C_OUT,A,B,C_IN);initialbegin$monitor($time,A=%b,B=%b,C_IN=%b,---C_OUT=%b,SUM=%b\n,A,B ,C_IN,C_OUT,SUM);endinitialbeginA=4'd0;B=4'd0;C_IN=1'b0;#5 A=4'd3;B=4'd4;#5 A=4'd2;B=4'd5;#5 A=4'd9;B=4'd9;#5 A=4'd10;B=4'd15;#5 A=4'd10;B=4'd5;C_IN=1'b1;endendmodule五、仿真结果及分析五、调试情况,设计技巧及体会1、程序调试:开始时程序一直都编译不出来,总是出现错误,认真修改后,总算是编译成功了,但在SIMULATE时又出现错误,~在同学的帮助下,经过认真的改正,最终修改正确运行成功。

⽤verilogHDL设计⼀个8位字节⽐较器,⽐较两个输⼊字节的⼤⼩,三个输出端⼝,⽤⾏为。

⼀、实验要求:1、⽐较两个输⼊字节的⼤⼩,三个输出端⼝,当a⼤于b,re=1,其余为0;当a⼩于b,reb=1,其余为0;当a等于b时,eq=1,其余为0。

⽤两种描述实现(可⽤⾏为级描述语句和连续赋值语句实现)。

2、写出测试模块,随机产⽣两个8位输⼊数据,通过⼀个周期为100ns的时钟,每隔⼀个周期产⽣两个新的随机数。

3、提交⽐较器程序和测试程序,观测仿真波形,并对仿真波形做分析,说明设计的正确性。

⼆、实验代码:1、⾏为级描述语句实现:module compare1#(parameter W = 8) //wide is 8(input [W-1:0] a,input [W-1:0] b,output reg re,output reg reb,output reg eq);always@(a or b) begin//When a or b changes, the statement within the block executesif(a>b){re,reb,eq}=3'b100; //a>b,re=1'b1else if(a<b){re,reb,eq}=3'b010; //a<b,reb=1'b1else{re,reb,eq}=3'b001; //a=b,eq=1'b1endendmodule2、连续赋值语句实现:module compare2_ass(input [7:0] a,input [7:0] b,output re,output reb,output eq);assign re=(a>b)? 1'b1:1'b0; //a>b,re=1'b1assign reb=(a<b)? 1'b1:1'b0; //a<b,reb=1'b1assign eq=(a==b)? 1'b1:1'b0; //a=b,eq=1'b1endmodule3、测试模块:`timescale 1ns/1psmodule compare_tb();parameter CYCLE = 10;//100MHzreg [7:0] a;reg [7:0] b;wire re1;//The output ports of the two modules are defined separately wire re2;wire reb1;wire reb2;wire eq1;wire eq2;initial begina = 8'h00;b = 8'h00;#(CYCLE*1000)$stop;endalways #(CYCLE*10) //two random numbers per 100nsa={$random}%256;always #(CYCLE*10) //two random numbers per 100nsb={$random}%256;compare1 U1(.a(a),.b(b),.re(re1),.reb(reb1),.eq(eq1));compare2_ass U2(.a(a),.b(b),.re(re2),.reb(reb2),.eq(eq2));endmodule4、仿真波形:⾏为级描述语句实现的⽐较器波形:如下图所⽰,当a>b时re=1:如下图所⽰,当a<b时reb=1如下图所⽰,当a=b时eq=1:如下图所⽰,测试模块可实现每隔⼀个周期为100ns的时钟产⽣两个新的8位随机输⼊数据:连续赋值语句实现的⽐较器波形:如下图所⽰,当a>b时re=1:如下图所⽰,当a<b时reb=1:如下图所⽰,当a=b时eq=1:如下图所⽰,测试模块可实现每隔⼀个周期为100ns的时钟产⽣两个新的8位随机输⼊数据:。

实验报课程名称:Verilog数字系统设计实验实验项目:全加器与比较器的设计姓名:专业:计算机科学与技术班级:学号:计算机科学与技术学院实验教学中心实验项目名称:全加器与比较器的设计一、实验目的1.学习用Verilog HDL 语言描述组合逻辑电路。

2.学会Quartus II 利用仿真与下载调试的程序方法。

二、实验内容利用Verilog HDL 语言设计四位全加器和比较器。

三、实验用设备仪器及材料硬件:计算机 软件:Quartus II 软件四、实验原理及接线1. 数值比较器用途是比较两个二进制数的大小。

一位数值比较器:比较输入的两个1位二进制数A 、B 的大小。

多位数值比较器:比较输入的两个位二进制数A 、B 的大小,比较时需从 高位到低位逐位比较。

比较器功能框图:GSE下表是一位数值比较器的真值表。

表1-1 比较器真值表2.全加器:全加器是实现两个一位二进制数及低位来的进位数相加(即将三个二进制数相加),求得和数及向高位进位的逻辑电路。

所以全加器有三个输入端(Ai,Bi,Ci-1)和两个输出端Si,Ci+1。

真值表如下:五、实验程序代码及仿真1、比较器代码module bijiaoqi(a,b,l,g,e,ledcom);input[3:0] a,b;output l,g,e;output ledcom;reg l,g,e;always@(a,b)beging = a>b ? 1:0;l = a<b ? 1:0;e = a==b ? 1:0;endendmodule比较器结果仿真结果2、全加器代码module add(a,b,cin,cout,sum);input a,b,cin;output cout,sum;wire a,b,cin,cout,sum;wire w1,w2,w3,w4;and u1(w1,a,b);and u2(w2,a,cin);and u3(w3,b,cin);or #2 u4(cout,w1,w2,w3);xor f1(w4,a,b);xor #1 f2(sum,w4,cin);endmodule全加器结果仿真结果六、心得与体会通过本次实验,使我掌握了Verilog编程方法以及熟悉了如何使用QuartusII 软件。

实验二全加器的设计

预习要求:要求同学们在实验前务必完成一位全加器、八位全加器项目设计、仿真、引脚锁定。

最后将自己预习做的工程项目文件夹压缩后,以“学号_姓名_实验二”命名后,于实验前交各实验小组组长,由小组组长收齐后交实验指导教师。

否则不允许参加实验。

一、实验目的

1、熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路

2、掌握层次化设计的方法

3、利用层次化的设计方法,设计一个8位全加器

4、熟悉利用CPLD/FPGA实验开发平台进行系统设计验证。

二、实验原理

一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接。

三、实验内容

1、完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个硬件符号入库。

KEY1、KEY

2、KEY3分别接ain、bin、cin;发光管LED2、LED1分别接sum和cout。

2、实验内容

建立一个更高层次的原理图设计,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真。

3、思考

设计一电路,在FPGA开发平台上验证8位全加器。

提示:设计电路如下图所示,其中位扫描应用减计数器。

四、实验报告

详细叙述8位加法器的设计流程;给出各层次的原理图及其对应的仿真波形图;给出加法器的时序分析情况;最后给出硬件测试流程和结果。

verilog实现加法器半加器如果不考虑来⾃低位的进位将两个1⼆进制数相加,称为半加。

实现半加运算的逻辑电路称为半加器。

真值表>> 逻辑表达式和s=ab′+a′b>> 逻辑表达式进位输出co=abverilog codemodule halfadder(output s, //sumoutput co, //carryinput a,input b);assign s = a ^ b;assign co = a & b;//assign {co,s} = a + b;endmoduletestbenchmodule halfadder_tb;wire s;wire co;reg a;reg b;initialbegina = 0;b = 0;#10 a = 0 ;b = 0;#10 a = 0 ;b = 1;#10 a = 1 ;b = 0;#10 a = 1 ;b = 1;#10 $finish;endinitial begin$fsdbDumpfile("test.fsdb");$fsdbDumpvars();endhalfadder u_halfadder(.s(s),.co(co),.a(a),.b(b));endmodule全加器在将两位多位⼆进制数相加时,除了最低位以外,每位都应该考虑来⾃低位的进位,即将两个对应位的加数和来⾃低位的进位3个数相加。

这种运算称为全加,所⽤的电路称为全加器。

真值表逻辑表达式和s=(a′b′ci′+ab′ci+a′bci+abci′)′>> 逻辑表达式进位输出co=(a′b′+b′ci′+a′ci′)′verilog codemodule fulladder(output s, //sumoutput co, //carry to high bitinput a,input b,input ci //carry from low bit);//RTL levelassign s = ~((~a&~b&~ci)||(a&~b&ci)||(~a&b&ci)||(a&b&~ci));assign co = ~((~a&~b)||(~b&~ci)||(~a&~ci));//assign {co,s} = a + b + ci;endmoduletestbenchmodule fulladder_tb;wire s;wire co;reg a;reg b;reg ci;initialbeginci = 0; a = 0 ;b = 0;#10 ci = 0; a = 0 ;b = 1;#10 ci = 0; a = 1 ;b = 0;#10 ci = 0; a = 1 ;b = 1;#10 ci = 1; a = 0 ;b = 0;#10 ci = 1; a = 0 ;b = 1;#10 ci = 1; a = 1 ;b = 0;#10 ci = 1; a = 1 ;b = 1;#10 $finish;endinitial begin$fsdbDumpfile("test.fsdb");$fsdbDumpvars();endfulladder u_fulladder(.s(s),.co(co),.a(a),.b(b),.ci(ci));endmodule多位加法器串⾏进位加法器依次将低位全加器的进位输出co接到全加器的进位输⼊端ci,就可以构成多位加法器。

实验一:半加器与全加器实验(1)实验目的与任务目的:理解半加器、全加器原理;掌握加法器Verilog编写方法;熟悉基于Quartus II软件的Verilog代码文本输入设计流程。

任务:基于Quartus II软件和EDA实验箱完成全加器的设计、仿真与硬件测试。

(2)实验设备带有windows操作系统和Quartus II软件的PC机一台;EDA实验箱一台(包含电源线和下载线)。

(3)实验内容基于Quartus II软件使用Verilog HDL设计半加器与全加器,并进行仿真和硬件测试。

硬件测试方案:使用拨码开关SW1(被加数)、SW2(加数)和SW3(进位输入)作为输入,以发光二极管LED0(和)和LED1(进位输出)作为输出。

拨动SW1、SW2和SW3,LED0和LED1显示正确。

原理图:注意:原理图中的SW0、SW1、SW2应该为实验箱上的SW1、SW2、SW3。

(4)实验步骤①运行Quartus II软件,编写半加器和全加器的Verilog代码,并保存(半加器保存为h_adder.v,全加器保存为f_adder.v)。

②创建工程,工程名为f_adder,把h_adder.v和f_adder.v添加到工程中,选择目标芯片为Cyclone III系列的EP3C120F780C8,不使用第三方EDA工具。

③编译。

④使用Quartus II自带的仿真工具对全加器进行时序仿真(打开波形编辑器,设置仿真时间50us,波形文件存盘f_adder.vwf,将工程f_adder的端口信号节点选入波形编辑器中,总线数据格式设置和参数设置,编辑输入波形数据,启动仿真器,观察仿真结果)。

⑤引脚锁定。

⑥编译文件(产生JTAG编程文件f_adder.sof(掉电丢失);并通过转换得到JTAG间接编程文件f_adder_file.jic(掉电不丢失))下载,硬件测试,随意拨动实验箱中的SW1、SW2和SW3,观察LED0和LED1的变化。

设计一位全加器的设计流程概述,基本步骤下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!全加器设计流程概述全加器是数字逻辑电路中的一个重要组成部分,主要用于实现二进制数的加法运算。

Verilog加法一、概述在数字电路设计中,加法是最基本的运算之一。

Verilog是一种硬件描述语言,常用于数字电路的建模和仿真。

本文将详细介绍Verilog中的加法实现方法和相关知识。

二、加法原理加法是一种基本的算术运算,用于将两个数值相加得到它们的和。

在数字电路中,加法可以通过逻辑门电路来实现。

常见的加法电路有半加器、全加器、加法器等。

2.1 半加器半加器是最基本的加法电路,用于将两个输入位相加,并输出它们的和以及进位。

半加器的真值表如下:A B Sum Carry0 0 0 00 1 1 01 0 1 01 1 0 12.2 全加器全加器是一种可以处理两个输入位和一个进位位的加法电路。

全加器的真值表如下:A B Cin Sum Cout0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 12.3 加法器加法器是由多个全加器组成的电路,用于实现多位数的加法运算。

常见的加法器有Ripple Carry Adder(连续进位加法器)、Carry Look-ahead Adder(预先计算进位加法器)等。

三、Verilog实现在Verilog中,可以使用模块化的方式来实现加法器电路。

下面是一个4位全加器的Verilog代码示例:module FullAdder(input wire A,input wire B,input wire Cin,output wire Sum,output wire Cout);assign Sum = A ^ B ^ Cin;assign Cout = (A & B) | (Cin & (A ^ B));endmodulemodule FourBitAdder(input wire [3:0] A,input wire [3:0] B,output wire [3:0] Sum,output wire Cout);wire [3:0] carry;FullAdder FA0(A[0], B[0], 1'b0, Sum[0], carry[0]);FullAdder FA1(A[1], B[1], carry[0], Sum[1], carry[1]);FullAdder FA2(A[2], B[2], carry[1], Sum[2], carry[2]);FullAdder FA3(A[3], B[3], carry[2], Sum[3], Cout);endmodulemodule TestFourBitAdder;reg [3:0] A;reg [3:0] B;wire [3:0] Sum;wire Cout;FourBitAdder FBA(A, B, Sum, Cout);initial beginA = 4'b0001;B = 4'b0011;#10;$display("Sum: %b", Sum);$display("Cout: %b", Cout);endendmodule四、仿真结果通过上述Verilog代码进行仿真,可以得到以下结果:Sum: 0100Cout: 0五、总结本文介绍了Verilog中加法的原理和实现方法。

实验报告

课程名称:Verilog数字系统设计实验

实验项目:全加器与比较器的设计

姓名:

专业:计算机科学与技术

班级:

学号:

计算机科学与技术学院

实验教学中心

实验项目名称:全加器与比较器的设计

一、实验目的

1.学习用Verilog HDL语言描述组合逻辑电路。

2.学会Quartus II利用仿真与下载调试的程序方法。

二、实验内容

利用Verilog HDL语言设计四位全加器和比较器。

三、实验用设备仪器及材料

硬件:计算机软件:Quartus II软件

四、实验原理及接线

1. 数值比较器

用途是比较两个二进制数的大小。

一位数值比较器:比较输入的两个1位二进制数A、B的大小。

多位数值比较器:比较输入的两个位二进制数A、B的大小,比较时需从高位到低位逐位比较。

比较器功能框图:

G

S

E

B1

B0

下表是一位数值比较器的真值表。

表1-1 比较器真值表

2.全加器:全加器是实现两个一位二进制数及低位来的进位数相加(即将三个二进制数相加),求得和数及向高位进位的逻辑电路。

所以全加器有三个输入端(Ai,Bi,Ci-1)和两个输出端Si,Ci+1。

真值表如下:

五、实验程序代码及仿真

1、比较器代码

module bijiaoqi(a,b,l,g,e,ledcom);

input[3:0] a,b;

output l,g,e;

output ledcom;

reg l,g,e;

always@(a,b)

begin

g = a>b ? 1:0;

l = a<b ? 1:0;

e = a==b ? 1:0;

end

endmodule

比较器结果仿真结果

2、全加器代码

module add(a,b,cin,cout,sum); input a,b,cin;

output cout,sum;

wire a,b,cin,cout,sum;

wire w1,w2,w3,w4;

and u1(w1,a,b);

and u2(w2,a,cin);

and u3(w3,b,cin);

or #2 u4(cout,w1,w2,w3);

xor f1(w4,a,b);

xor #1 f2(sum,w4,cin);

endmodule

全加器结果仿真结果

六、心得与体会

通过本次实验,使我掌握了Verilog编程方法以及熟悉了如何使用QuartusII 软件。

我了解了什么是比较器,什么是全加器,并且能够通过编程实现它们。

同时进行了比较器和全加器的实验结果仿真。

不断的上机训练使我掌握了Verilogde 上机过程,了解Verilog语言的使用。

从书本走到实际中进行操作,真正实现了语言的运用。

同时,我学回了把代码变成实际输出,看到成果让我十分开心。

在实验中,我不但认识到了掌握Verilog知识的重要性,更能够理论充分的联系实际,实现了书本知识的良好掌握。