Verilog 实验指导书

- 格式:doc

- 大小:266.00 KB

- 文档页数:10

电子科技大学计算机科学与工程学院实验指导书实验名称Verilog组合逻辑设计电子科技大学教务处制表一、概述本实验使用Xilinx ISE软件和Verilog语言进行组合逻辑的设计与实现。

实验内容包括1.3-8译码器的设计和实现。

2.4位并行进位加法器的设计和实现。

3.两输入4位多路选择器的设计和实现。

实验要求如下:1.采用Verilog语言设计,则使用门级方式进行描述。

2.编写仿真测试代码。

3.编写约束文件,使输入、输出信号与开发板的引脚对应。

4.下载到FPGA开发板,拨动输入开关,观察Led灯的显示是否符合真值表。

二、实验原理:1.74x138译码器是输出低有效的3-8译码器。

表1所示为74x138译码器的真值表。

表1 译码器的真值表根据上述函数表达式,可画出逻辑电路图为。

图1 3-8译码器的逻辑电路图2. 数据选择器的逻辑功能是根据地址选择端的控制,从多路输入数据中选择一路数据输出。

因此,它可实现时分多路传输电路中发送端电子开关的功能,故又称为复用器(Multiplexer),并用MUX来表示。

201Y 为数据选择器的输出,根据真值表可写出它的输出函数表达式为:如果输入再加上低有效的输入使能端,则输出的表达式变为根据上述函数表达式,可画出2输入4位多路选择器的逻辑电路图为。

图2 2输入4位多路选择器的逻辑电路图2. 1位全加器的真值表如下表3 1位全加器的真值表对于4位并行加法器,可以按入下公式进行设计图3所示为4位并行进位加法器框图,本实验中用Verilog语句来描述。

图3 4位并行进位加法器三、设计实现1.在ISE设计中可以直接输入如下3-8译码器的代码仿真结果如下图所示。

图4 译码器的仿真结果3.译码器在Nexys3开发板上的约束文件4.4位并行加法器的代码仿真结果如下图所示。

图5 加法器的仿真结果6.加法器在Nexys3开发板上的约束文件7.数据选择器的代码仿真结果如下图所示。

图6 数据选择器的仿真结果9.数据选择器在Nexys3开发板上的约束文件。

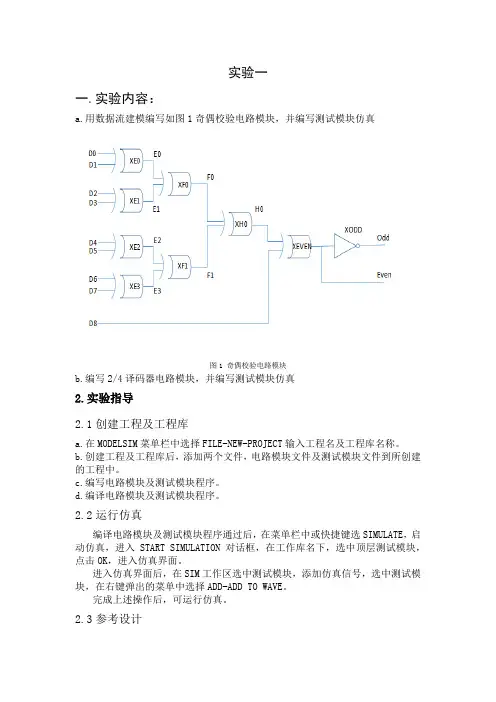

实验一一.实验内容:a.用数据流建模编写如图1奇偶校验电路模块,并编写测试模块仿真图1 奇偶校验电路模块b.编写2/4译码器电路模块,并编写测试模块仿真2.实验指导2.1创建工程及工程库a.在MODELSIM菜单栏中选择FILE-NEW-PROJECT输入工程名及工程库名称。

b.创建工程及工程库后,添加两个文件,电路模块文件及测试模块文件到所创建的工程中。

c.编写电路模块及测试模块程序。

d.编译电路模块及测试模块程序。

2.2运行仿真编译电路模块及测试模块程序通过后,在菜单栏中或快捷键选SIMULATE,启动仿真,进入START SIMULATION 对话框,在工作库名下,选中顶层测试模块,点击OK,进入仿真界面。

进入仿真界面后,在SIM工作区选中测试模块,添加仿真信号,选中测试模块,在右键弹出的菜单中选择ADD-ADD TO WAVE。

完成上述操作后,可运行仿真。

2.3参考设计2.3.1奇偶校a.电路模块module parity_9_bit(D,even,odd);input [8:0] D;output even,odd;assign #(4,3) odd=~even;assign #(4,4) even=(((D[0]^D[1])^D[2]^D[3]))^((D[4]^D[5])^(D[6]^D[7])))^D[8];endmoduleb.测试模块module test_parity;2.3.2译码器a.2/4译码器真值表b.电路模块module decode2_4(d,s);二.程序设计2.14奇偶校验程序module jioujiao (D, even,odd) ;input [8:0] D ;output even, odd;assign #(4,3) odd= ~even;assign #(4,4) even= (((D[0]^D[1])^(D[2]^D[3]))^ ((D[4]^D[5])^(D[6]^D[7])))^ D[8];endmodule测试程序`timescale 1 ns/ 1 nsmodule parity_9_bit_vlg_tst();// constants// general purpose registers// test vector input registersreg [8:0] D;// wireswire even;wire odd;// assign statements (if any)parity_9_bit i1 (// port map - connection between master ports and signals/registers .D(D),.even(even),.odd(odd));initialbegin#0 D = 0;#20 D = 1;#30 D = 9'b0_0000_0011;#30 D = 9'b0_0000_0111;#30 D = 9'b0_0000_1111;#30 D = 9'b0_0001_1111;#30 D = 9'b0_0011_1111;#30 D = 9'b0_0111_1111;#30 $stop;endendmodule2.24二四译码器程序module decode2_4(d, s, rst);input [1:0]s;input rst;output [3:0]d;reg [3:0]d;always @(s or rst)beginif(!rst)d <= 0;else if(s==2'b00) d <= 4'b0001;else if(s==2'b01) d <= 4'b0010;else if(s==2'b10) d <= 4'b0100;else if(s==2'b11) d <= 4'b1000;endendmodule测试程序`timescale 1 ns/ 1 psmodule decode2_4_vlg_tst();// constants// general purpose registersreg eachvec;// test vector input registersreg rst;reg [1:0] s;wire [3:0] d;// assign statements (if any)decode2_4 i1 (.d(d),.rst(rst),.s(s));initialbegins = 0;rst = 1;#1 rst = 0;#1 rst = 1;#10s=2'b00;#10s=2'b01;#10s=2'b10;#10s=2'b11;#10 $stop;endendmodule三.实验结果测试图1图2 1奇偶校验仿真图图22二四译码器仿真图四.实验总结本次实验是通过数据流建模的方式完成部分任务,通过本次实验。

电子科技大学计算机科学与工程学院实验指导书实验名称Verilog组合逻辑设计电子科技大学教务处制表一、概述本实验使用Xilinx ISE软件和Verilog语言进行组合逻辑的设计与实现。

实验内容包括1.3-8译码器的设计和实现。

2.4位并行进位加法器的设计和实现。

3.两输入4位多路选择器的设计和实现。

实验要求如下:1.采用Verilog语言设计,则使用门级方式进行描述。

2.编写仿真测试代码。

3.编写约束文件,使输入、输出信号与开发板的引脚对应。

4.下载到FPGA开发板,拨动输入开关,观察Led灯的显示是否符合真值表。

二、实验原理:1.74x138译码器是输出低有效的3-8译码器。

表1所示为74x138译码器的真值表。

12_2_ 0_1_2_3_4_5_6_7_G G G A L G B LY L C B A GY L C B A GY L C B A GY L C B A GY L C B A GY L C B A GY L C B A GY L C B A G=⋅⋅=⋅⋅⋅=⋅⋅⋅=⋅⋅⋅=⋅⋅⋅=⋅⋅⋅=⋅⋅⋅=⋅⋅⋅=⋅⋅⋅根据上述函数表达式,可画出逻辑电路图为。

图1 3-8译码器的逻辑电路图2. 数据选择器的逻辑功能是根据地址选择端的控制,从多路输入数据中选择一路数据输出。

因此,它可实现时分多路传输电路中发送端电子开关的功能,故又称为复用器(Multiplexer),并用MUX来表示。

表2 2输入1位多路选择器的真值表数据输入选择控制S 输出Y D0 D10 0 0 00 1 00 1 0 0 1 1 1 0 1 0 0 1 0 0 1 1 1 1 0 1 0 1 1 1 101为选择控制端,Y 为数据选择器的输出,根据真值表可写出它的输出函数表达式为:01Y SD SD =+如果输入再加上低有效的输入使能端,则输出的表达式变为0101_()__Y EN L SD SD EN L S D EN L S D =⋅+=⋅⋅+⋅⋅根据上述函数表达式,可画出2输入4位多路选择器的逻辑电路图为。

《FPGA设计与应用》实验指导书熊利祥编武汉理工大学华夏学院2011年9月前言一、实验课目的数字电路与系统设计实验课是电子工程类专业教学中重要的实践环节,包括了ISE开发环境基本操作及FPGA的基本原理、基带传输系统的设计、Uart串口控制器电路的设计、PS/2接口的设计、VGA显示接口设计。

要求学生通过实验学会正确使用EDA技术,掌握FPGA器件的开发,熟练使用ISE开发环境,掌握Verilog语言的编程,掌握数字电路和系统的设计。

通过实验,使学生加深对课堂专业教学内容的理解,培养学生理论联系实际的能力,实事求是,严谨的科学作风,使学生通过实验结果,利用所学的理论去分析研究EDA技术。

培养学生使用Basys 2开发板的能力以及运用实验方法解决实际问题的能力。

二、实验要求:1.课前预习①认真阅读实验指导书,了解实验内容;②认真阅读有关实验的理论知识;③读懂程序代码。

2.实验过程①按时到达实验室;②认真听取老师对实验内容及实验要求的讲解;③认真进行实验的每一步,观察程序代码与仿真结果是否相符;④将实验过程中程序代码和仿真结果提交给老师审查;⑤做完实验后,整理实验设备,关闭实验开发板电源、电脑电源后方可离开。

3.实验报告①按要求认真填写实验报告书;②认真分析实验结果;③按时将实验报告交给老师批阅。

三、实验学生守则1.保持室内整洁,不准随地吐痰、不准乱丢杂物、不准大声喧哗、不准吸烟、不准吃东西;2.爱护公务,不得在实验桌及墙壁上书写刻画,不得擅自删除电脑里面的文件;3.安全用电,严禁触及任何带电体的裸露部分,严禁带电接线和拆线;4.任何规章或不按老师要求操作造成仪器设备损坏须论价赔偿。

目录实验一Uart通用串口接口的设计 (4)实验二PS/2接口的设计 (28)实验三VGA显示接口设计 (30)附录一 basys 2开发板资料 (36)实验一 Uart串口控制接口电路的设计一、实验目的1.掌握分频模块的设计方法。

试验一:开关、LED灯及多路复用器1.1将输入/输出器件连接到FPGA上实验原理:用18 个波段开关作为电路的输入,用18 个红色LED作为电路的输出,实现用波段开关控制红色LED,将开关拨到上方,相应的LED灯亮,否则LED灯灭实验步骤:实验步骤:(1)新建一个QuartusII工程(2)新建一个Verilog文件,将该Verilog文件添加到工程中并编译整个工程(3)分配引脚LEDR[0],PIN_AE23 SW[0],PIN_N25LEDR[1],PIN_AF23 SW[1],PIN_N26LEDR[2],PIN_AB21 SW[2],PIN_P25LEDR[3],PIN_AC22 SW[3],PIN_AE14LEDR[4],PIN_AD22 SW[4],PIN_AF14LEDR[5],PIN_AD23 SW[5],PIN_AD13LEDR[6],PIN_AD21 SW[6],PIN_AC13LEDR[7],PIN_AC21 SW[7],PIN_C13LEDR[8],PIN_AA14 SW[8],PIN_B13LEDR[9],PIN_Y13 SW[9],PIN_A13LEDR[10],PIN_AA13 SW[10],PIN_N1LEDR[11],PIN_AC14 SW[11],PIN_P1LEDR[12],PIN_AD15 SW[12],PIN_P2LEDR[13],PIN_AE15 SW[13],PIN_T7LEDR[14],PIN_AF13 SW[14],PIN_U3LEDR[15],PIN_AE13 SW[15],PIN_U4LEDR[16],PIN_AE12 SW[16],PIN_V1LEDR[17],PIN_AD12 SW[17],PIN_V2(4)编译该工程,完成后下载到FPGA中(5)通过拨动波段开关并观察红色LED的变化来验证所设计的功能是否正确参考代码:module led1(sw,d);input [17:0] sw;output [17:0] d;assign d=sw;endmodule1.2 3位宽5选1多路复用器实验原理:实现一个5选1的多路复用器,即从5个输入x,y,w,u,v中选取一个输出到m,输出选择用一个3位的输入s0s1s2实现实验步骤:(1)新建一个QuartusII工程(2)新建一个Verilog文件,用SW17~SW15作为选择端输入s0s1s2,用剩下的15个波段开关SW14~SW0作为u,v,w,x,y,用绿色LED即LEDG2~LEDG0作为输出M,将该Verilog 文件添加到工程中(3)分配连接波段开关、绿色LED的FPGA管脚LEDG[0],PIN_AE22LEDG[1],PIN_AF22LEDG[2],PIN_W19LEDG[3],PIN_V18LEDG[4],PIN_U18LEDG[5],PIN_U17LEDG[6],PIN_AA20LEDG[7],PIN_Y18(4)编译工程,完成后下载到FPGA中(5)拨动波段开关并观察绿色LED的变化,以验证3位5选1多路复用器的功能是否正确,确定从u到v的所有输入都能够被选择输出到M参考代码:module sel5to1(s,u,v,w,x,y,m);input[2:0] s,u,v,w,x,y;output[2:0] m;reg[2:0] m;always@(s)beginif(s=='b000)m=u;else if(s=='b001)m=v;else if(s=='b010)m=w;else if(s=='b011)m=x;else if(s=='b100)m=y;elsem=m;endendmodule1.3并行加法器实验原理:全加器的电路如图1(a)所示,输入为a,b和ci,输出为s和co,图1(b)是该电路的符号表示,表1为全加器的真值表,全加器实现了二进制加法,其输出为一个2位的二进制和co s=a+b+ci,用四个全加器模块的电路可以实现4位二进制数的加法,如图1(c)所示,这种加法器电路一般称为并行加法器(a ) (b )表1 实验步骤:(1)新建一个QuartusII 工程(2)建立一个Verilog 文件,然后用4个全加器电路来实现并行加法器电路(3)分别用SW7~SW4和SW3~SW0代表A 和B ,使用SW8代表加法器的进位输入cin ,而加法器的输出cout 和S 连接到LEDG4~LEDG0上,将代码添加到工程中 (4)进行引脚分配(5)改变输入A ,B 和cin 的值,观察计算结果是否正确 参考代码:module add(a,b,s,cout); input[3:0] a,b; output [3:0] s; output cout;wire c0,c1,c2;addone addone1(a[0],b[0],0,s[0],c0), addone2(a[1],b[1],c0,s[1],c1), addone3(a[2],b[2],c1,s[2],c2),addone4(a[3],b[3],c2,s[3],cout);endmoduleciabbcoF AFA FA FA FAs0s1s2s3c o c ic 1c 2c 3a1a2a3b1b2b3a0b0omodule addone(a,b,cin,s,cout);input a,b, cin;output s,cout;assign {cout,s}=a+b+cin;endmodule实验二:乘法器、锁存器及触发器2.1无符号乘法器实验原理:图1(a)位两位十进制数乘法的实现P=A*B,其它A=12,B=11,P=132,图1(b)是用4位二进制乘法实现的A和B的乘积,B的每一位要么是0,要么是1,因此算式中的加数要么是一位的A,要么是0000,图1(c)是用逻辑与实现的二进制乘法的过程12* 111212132(a)(b)图1(c)图2是实现4位二进制乘法P=A*B的电路,该电路中,用逻辑与实现每一行的乘法,用全加器实现每一列的加法,从而得到所需要的和。

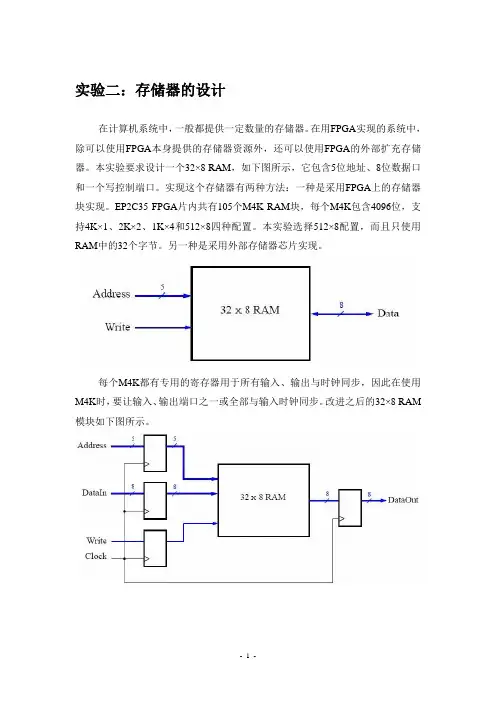

实验二:存储器的设计在计算机系统中,一般都提供一定数量的存储器。

在用FPGA实现的系统中,除可以使用FPGA本身提供的存储器资源外,还可以使用FPGA的外部扩充存储器。

本实验要求设计一个32×8 RAM,如下图所示,它包含5位地址、8位数据口和一个写控制端口。

实现这个存储器有两种方法:一种是采用FPGA上的存储器块实现。

EP2C35 FPGA片内共有105个M4K RAM块,每个M4K包含4096位,支持4K×1、2K×2、1K×4和512×8四种配置。

本实验选择512×8配置,而且只使用RAM中的32个字节。

另一种是采用外部存储器芯片实现。

每个M4K都有专用的寄存器用于所有输入、输出与时钟同步,因此在使用M4K时,要让输入、输出端口之一或全部与输入时钟同步。

改进之后的32×8 RAM 模块如下图所示。

1.用LPM实现32×8 RAM常用的逻辑电路如加法器、计数器、寄存器和存储器都可调用QuartusII提供的参数化功能模块LPM实现。

本实验采用LPM altsyncram实现存储器。

第1步:新建一个Quartus项目,并命名为lpm_sram。

第2步:新建一个图形文件,新建一个图形文件,并命名为lpm_sram.bdf。

打开符号(symbol)库,如下图所示。

从左边符号库中选中”altsyncram”,点击“ok”出现如下图所示的界面,第4步:点击Next按钮,在下一个对话框中选择“with one read/write port”模式,如下图所示。

第5步:点击Next按钮,在下一个对话框中选择存储器容量是32个字节,如下图所示。

第6步:其他对话框均采用默认值即可,最后按Finish按钮即完成RAM模块的设计。

第8步:添加相应的输入和输出端口,端口命名如下图所示。

第9步:进行语法检查,检查通过后,打开Pin Planner,用SW7~SW0作为数据输入、SW12~SW8作为地址的输入、SW13作为Write信号、结果显示在LEDG 上。

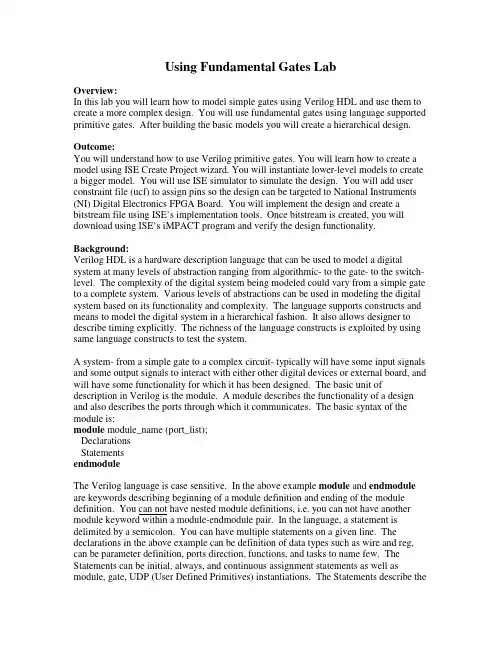

Using Fundamental Gates LabOverview:In this lab you will learn how to model simple gates using Verilog HDL and use them to create a more complex design. You will use fundamental gates using language supported primitive gates. After building the basic models you will create a hierarchical design. Outcome:You will understand how to use Verilog primitive gates. You will learn how to create a model using ISE Create Project wizard. You will instantiate lower-level models to create a bigger model. You will use ISE simulator to simulate the design. You will add user constraint file (ucf) to assign pins so the design can be targeted to National Instruments (NI) Digital Electronics FPGA Board. You will implement the design and create a bitstream file using ISE’s implementation tools. Once bitstream is created, you will download using ISE’s iMPACT program and verify the design functionality. Background:Verilog HDL is a hardware description language that can be used to model a digital system at many levels of abstraction ranging from algorithmic- to the gate- to the switch-level. The complexity of the digital system being modeled could vary from a simple gate to a complete system. Various levels of abstractions can be used in modeling the digital system based on its functionality and complexity. The language supports constructs and means to model the digital system in a hierarchical fashion. It also allows designer to describe timing explicitly. The richness of the language constructs is exploited by using same language constructs to test the system.A system- from a simple gate to a complex circuit- typically will have some input signals and some output signals to interact with either other digital devices or external board, and will have some functionality for which it has been designed. The basic unit of description in Verilog is the module. A module describes the functionality of a design and also describes the ports through which it communicates. The basic syntax of the module is:module module_name (port_list);DeclarationsStatementsendmoduleThe Verilog language is case sensitive. In the above example module and endmodule are keywords describing beginning of a module definition and ending of the module definition. You can not have nested module definitions, i.e. you can not have another module keyword within a module-endmodule pair. In the language, a statement is delimited by a semicolon. You can have multiple statements on a given line. The declarations in the above example can be definition of data types such as wire and reg, can be parameter definition, ports direction, functions, and tasks to name few. The Statements can be initial, always, and continuous assignment statements as well as module, gate, UDP (User Defined Primitives) instantiations. The Statements describe theactual functionality of the module. The identifiers must be defined using Declarations before they ca be used.The language defines three fundamental modeling styles. In a given module all or subset of these styles can be used. The three modeling styles are: Structural, Dataflow, and Behavioral. This lab exercise uses Structural style modeling. Structure can be described in Verilog using Built-in gate primitives, Switch-level primitives, User-Defined Primitives (UDP), and module instances. The Switch-level primitives are used to model fundamental gate functionality or a system built with switches or transistors. The UDP are used to define a unit as a black-box with providing functionality in truth-table form and explicit timing relationships between input and output ports. In this lab exercise you will use gate primitives and module instantiations. The language defines the following gates:[Verilog Quick Reference]Here is an example of instantiating a nor gate:nor X1 (S1, A, B);where X1 is the instance name. It is optional for the gate- or switch-level instantiation. The instance name is required for a module instantiation. S1 is output, and A and B are input.References:1. National Instruments’ Digital Electronics FPGA Board user manual2. Verilog HDL booksStephen Brown, Zvonko G. Vranesic, “Fundamentals of Digital Logic with Verilog Design”, 2002 Zainalabedin Navabi, “Verilog Digital Systems Design: RT Level Synthesis, Testbench, andVerification”, 2005Samir Paltinkar, “Verilog HDL: A Guide to Digital Design and Synthesis”, 2003Joseph Cavanagh, “Verilog HDL: Digital Design and Modeling”, 2007Michael D. Ciletti, “Modeling, Synthesis, and Rapid Prototyping with Verilog HDL”, 2003Douglas J. Smith, “HDL Chip Design: A Practical Guide for Designing, Synthesizing and Simulating ASICs and FPGAs using VHDL or Verilog”, 19963. On-line references:Verilog HDL Reference Card: /class/ee183/handouts_win2003/VerilogQuickRef.pdfVerilog Quick Reference: /~howard/pulsenet/docs/verilog_quikref.pdfTutorial on Verilog: .sa/COE/abouh/COE%20202%20Verilog%20Guidelines.pdfProblem Statement:Design a minority gate that has three inputs and one output. The output is logic 1 whenever the numbers of inputs which are logic 1 are zero or less than half of the input (i.e. 1 in this case).Implementation:The circuit to be designed consists of three inputs and one output. Typically such circuit can be implemented using a combinational network. A truth table is created and then some Boolean minimization technique (e.g. K-Map) may be used to reduce the number of logic gates used. The truth table for the design at hand is shown next along with K-Map and minimized Boolean expression.Inputs A B C OutputF0 0 0 1 0 0 1 1 0 1 0 10 1 1 01 0 0 1 1 0 1 0 1 1 0 0 1 1 1 01 1 0 11 0 0 000 01 11 1001AB C F = A C + B C + A B F = (A+C) * (B+C) * (A+B)The two expressions are equivalent. We will use the 2nd expression in this design.Procedure:1. Create a ISE project• Launch ISE: Select Start → Programs → Xilinx ISE Design Suite 10.1 →ISE → Project Navigator• In the Project Navigator, select File → New Project. The New Project Wizard opens• For Project Location, use the “…” button to browse to C:\NI\Verilog_labs, and then click OK• For Project Name, type minoritygate_lab • Click Next • Select the following options and click Next Device Family: Spartan3E Device: xc3s500E Package: ft256 Speed Grade: –5 Synthesis Tool: XST (VHDL/Verilog) Simulator: ISE Simulator (VHDL/Verilog)Preferred Language: Verilog•The Create New Source dialog will appear. You can use this dialog to createa new HDL source file by defining the module name and ports. You will dothis once to get experience. Subsequent files creation will be done using a text file rather than using the dialog. Click New Source button• A new source wizard will appear. Select Verilog Module as a source type andenter my_2or in the File name field and click Next• A Define Module form will appear. Enter in1, in2 as the input in Port Nam e field and out1 as the output. Change the input Direction to output by clicking and drop-down button and selection output as the direction. Click Next and then OK to create the file•Click Next and Add Existing Sources form will be displayed. Click Finish as we do not have anything to add•Click Finish. A project will be created and my_or2.v file be created and added to the project. The file will be opened and displayed in the editorwindow. You can enter related information regarding project name, target devices, etc. You will also see a module and endmodule statements arecreated. The only thing that is needed is to add the functionalityYou will notice that the project hierarchy view window showing the part information as well as my_2or as the top-level model•Enter a gate-level instantiation statement that uses primitive gate to perform or function on the two inputs and output the result with 2 ns delay•Save and close the file•Click New button () and select text file and click OK•Enter the module, endmodule, and gate-level instantiation statement to model 2-input and function using the port names as in1, in2, and out1•Save and close the file, giving my_2and.v as the filename•Similarly, create a new model for the minority gate functionality (3 inputs [in1, in2, and in3] and one output [out1]), instantiating my_2or and my_2and models, and using necessary number of fundamental gates instantiations and having 2 ns as the delay. Use named-mapped port convention. The named-port convention requires a port name of the parent module be listed firstpreceded with “.” followed by a net name that is connecting that port in the current module. In the below figure, .in1 is the port name of my_or2 mdoule (parent module) where as in1_n is the net name connecting to that port. In named-port mapping convention, one need not mention all the ports of the parent module. The unlisted parent module ports are drive logic 0 if theyinput and left unconnected if they are output.•Right-click on my_2or entry in the Sources window and select Add Source …•Select minoritygate.v and my_2and.v files and click Open•Click OK to finish the addition2. Simulate the design using ISIM•Right-click on the minoritygate entry in Sources window and select New Source•Select Test Bench Waveform as the source type and enter minoritygate_tb in the File name field. Click Next•Select minoritygate as the UUT to associate the testbench to the source model and click Next followed by clicking Finish button•Select combinatorial (internal clock) and click Finish to display the input and output signals. Click appropriately in the waveform window to generate input stimulus as shown below•Save the file•Select Sources tab and then click minoritygate in Sources window, and click on the drop-down button of the Sources for window and select Behavioral Simulation•Select minoritygate_tb in Sources tab, expand its entry to see UUT. Select Processes tab, expand Xilinx USE Simulator, and double-click on Simulate Behavioral Model entry to run the simulator•The source files will be compiled and the executable file(minoritygate_tb_ism_beh.exe) be generated which is then run, displaying the result in a waveform window•You can view lower-level signals by selecting Sim Insulator tab in Sources window, expanding hierarchy, selecting a particular instance, then clicking Sim Objects in tab in Processes window, and then selecting and dragging a desired signal(s) in the waveform window•You can zoom-in or zoom-out the waveform window by clicking on appropriate buttons ()•You can restart by clicking on () button and re-run by clicking on run for the specified time()button•You can change the run-time by typing in the new time field(), clicking restart button, and then clicking on run for the specified time button•Close the simulator by closing the waveform window and click OK to close the active simulator3. Implement the design•Select implementation in Sources for window•Select minoritygate module in Sources window•Expand User Constraints processes in Processes window•Double-click on Floorplan IO Pre-Synthesis to open PACE program•Click OK and then Yes to add ucf file•In PACE window assign pin locations and I/O Std as shown below•Click Save button• A dialog box will appear. Choose XST Default: <> option and click OK as we are using XST synthesis tools•Close the PACE program using File→Close• A minoritygate.ucf file will be added to the project. Open that file and see how the constraints are written•Close the file•Select minoritygate in Sources window and double-click on Implement Design process in Processes window. This will go through Synthesis, and Implementation stages•Expand Synthesis processes and double click on View RTL Schematic and View Technology Schematic processes to get different views•You can push-in to a lower-level schematic by double-clicking on the top-level•When the implementation is completed, expand Implement Design process to view the Place & Route report•Double-click on the Place & Route Report to view the report. Look at the resource utilization and note that 1 slice is being used•You can see similar information by clicking on Design Summary tab and looking at the various information4. Verify the design in hardware•Select minoritygate in Sources window and double-click on GenerateProgramming File process to generate the bit file for the designConfiguration Project (iMPACT) process•Connect the board with the USB-JTAG cable•Power ON the board•Click Finish to use the JTAG chain•Select minoritygate.bit file to be assigned to xc3s500e device and click Open•Click Bypass button for xcf04s and then OK to use FPGA device programming•Right-click on the FPGA and select Program•This will program the FPGA and DONE light will lit on the board•Once programmed successfully, verify the functionality by using SW0 thru SW2 and monitoring LD0 output. Verify that when more than one switch isturned ON, LD0 turns OFF•Once confirmed the functionality, power down the board and close ISE saving project changesConclusion:In this lab exercise you learned how to design a hierarchical system. You also learned how to model a circuit using gate-level as well as module-instantiations. You were able to simulate the design at each level and then verify the complete design in hardware board.。

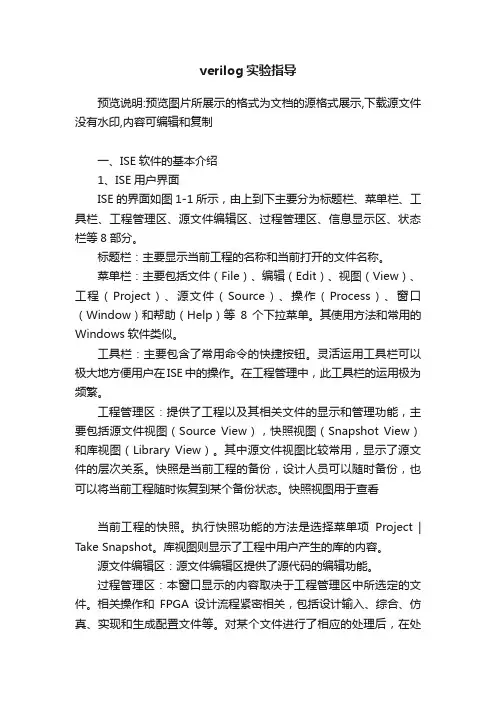

verilog实验指导预览说明:预览图片所展示的格式为文档的源格式展示,下载源文件没有水印,内容可编辑和复制一、ISE软件的基本介绍1、ISE用户界面ISE的界面如图1-1所示,由上到下主要分为标题栏、菜单栏、工具栏、工程管理区、源文件编辑区、过程管理区、信息显示区、状态栏等8部分。

标题栏:主要显示当前工程的名称和当前打开的文件名称。

菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、窗口(Window)和帮助(Help)等8个下拉菜单。

其使用方法和常用的Windows软件类似。

工具栏:主要包含了常用命令的快捷按钮。

灵活运用工具栏可以极大地方便用户在ISE中的操作。

在工程管理中,此工具栏的运用极为频繁。

工程管理区:提供了工程以及其相关文件的显示和管理功能,主要包括源文件视图(Source View),快照视图(Snapshot View)和库视图(Library View)。

其中源文件视图比较常用,显示了源文件的层次关系。

快照是当前工程的备份,设计人员可以随时备份,也可以将当前工程随时恢复到某个备份状态。

快照视图用于查看当前工程的快照。

执行快照功能的方法是选择菜单项Project | Take Snapshot。

库视图则显示了工程中用户产生的库的内容。

源文件编辑区:源文件编辑区提供了源代码的编辑功能。

过程管理区:本窗口显示的内容取决于工程管理区中所选定的文件。

相关操作和FPGA设计流程紧密相关,包括设计输入、综合、仿真、实现和生成配置文件等。

对某个文件进行了相应的处理后,在处理步骤的前面会出现一个图标来表示该步骤的状态。

信息显示区:显示ISE中的处理信息,如操作步骤信息、警告信息和错误信息等。

信息显示区的下脚有两个标签,分别对应控制台信息区(Console)和文件查找区(Find in Files)。

如果设计出现了警告和错误,双击信息显示区的警告和错误标志,就能自动切换到源代码出错的地方。

《可编程逻辑设计》实验手册福州大学物理与信息工程学院电子信息工程系注意事项1、本实验手册是为了配合《EDA技术实用教程》,作为本课程实验环节的补充指导而编制。

2、实验中涉及的QuartusⅡ软件的使用请参考《EDA技术实用教程》中有关章节。

3、手册中所有的虚线空白框,都留出来作为实验记录之用,每个实验完成后,应按照实验内容的要求将实验结果记入框中。

4、每个实验后面都附有一道思考题,完成实验内容后可以作为更进一步的练习。

5、每个实验中的硬件测试需要在实验箱上完成,引脚锁定请参考手册最后的实验箱引脚资源说明自行确定。

6、实验一~实验七为必做部分,请自行合理安排时间完成;实验八为选做部分。

7、每次实验后将手册相关部分(完成实验结果记录)、实验源代码(.v文件)或电路图一起,作为实验报告上交。

8、课程结束后请将所有报告按顺序加封面装订好上交,作为实验部分成绩计入总成绩。

目录实验一利用原理图输入法设计4位全加器 (1)实验二简单组合电路的设计 (4)实验三简单时序电路的设计 (6)实验四异步清零和同步时钟使能的4位加法计数器 (8)实验五七段数码显示译码器设计 (10)实验六数控分频器的设计 (12)实验七4位十进制频率计的设计 (14)实验八交通灯逻辑控制电路设计 (16)附录EDA实验箱部分资源引脚说明 (20)实验一利用原理图输入法设计4位全加器一、实验目的:熟悉如何在QuartusⅡ集成环境下利用原理图输入设计简单组合逻辑电路,掌握层次化的电路设计方法。

二、实验原理:一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的进位输入信号cin相接。

三、实验内容:1.QuartusII软件的熟悉熟悉QuartusⅡ环境下原理图的设计方法和流程,可参考课本5.4节的内容,重点掌握层次化的设计方法。

2.设计1位全加器原理图设计的原理图如下所示3.利用层次化原理图方法设计4位全加器(1)生成新的空白原理图,作为4位全加器设计输入(2)利用已经生成的1位全加器作为电路单元,设计4位全加器的原理图,如下所示4、设计一个超前进位4位全加器以上设计的全加器是基于串行进位的结构,高位的进位输入必须等待低位的运算结果,造成较长的延时。

“Verilog硬件描述语言”课程上机指导书程军2007-3第1次上机(2学时):1. ModelSim概览ModelSim仿真软件是由MentorGraphic公司的子公司Model技术公司开发的工业界上最为通用的仿真器之一,它可以用于Verilog仿真,VHDL仿真或者两者的混合仿真。

ModelSim仿真软件产品的类型很多,我们在这里要介绍的是ModelSim/SE,它是ModleSim主要的版本,功能最为强大,包含了ModelSim/PLUS的所有功能及其附加功能。

ModelSim/SE随着时间的推移不断地推出新的版本,我们要介绍的是Mentor Graphis公司于2005年6月推出的ModelSim/Se 6.1版本的使用。

首先要准备本实验教程的实验数据,请每个同学将目录/cad/Labs/mentor/modelsim/下的的modelsimLab文件夹(内部包含lab1、lab2、lab3、lab4四个文件夹)复制到自己的home目录下你新建的自己名字的目录内。

执行以下命令:unix%cd ~ unix%mkdir yourname unix%cd /cad/Labs/mentor/modelsim unix%cp -r modelsimLab ~/yourname unix%cd ~/yourname/modelsimLab/lab1 输入fpga.setup命令,然后输入vsim命令,便可以得到图1.1所示的ModelSim图形用户界面。

fpga.setup命令是为了设置环境变量,在每一个要运行modelsim的Terminal中只要执行一次。

unix%fpga.setup unix%vsim2. 基本的使用步骤ModelSim 有三种实现方法。

第一种是交互式的命令行,这种操作方法没有用户界面,唯一的界面是控制台的命令行。

第二种是用户界面(UI),它能够接收菜单输入和命令行输入。

文档编号版本 密级深圳市华为技术有限公司1.0内部公开共 56页研究管理部文档中心资源类别: HDL 语言Verilog 基本电路设计指导书(仅供内部使用)Verilog Group 拟制: 批准: 批准:日期: 日期: 日期:2000/04/04 yyyy/mm/dd yyyy/mm/dd深圳市华为技术有限公司版权所有 不得复制修订记录日期修订版本描述作者2000/04/04 1.00 2001/02/28 1.01Verilog Group 初稿完成修订,主要增加三态和一些电路图苏文彪目 录1前言5 56 6 6789 2典型电路的设计2.1全加器的设计2.2数据通路2.2.1四选一的多路选择器 2.2.2译码器 2.2.3优先编码器 2.3计数器 2.4算术操作 2.5逻辑操作 2.6移位操作 2.7时序器件10 10 11 12 12 12 13 2.7.1上升沿触发的触发器2.7.2 带异步复位、上升沿触发的触发器 2.7.3带异步置位、上升沿触发的触发器 2.7.4带异步复位和置位、上升沿触发的触 发器14 15 16 2.7.5带同步复位、上升沿触发的触发器 2.7.6带同步置位、上升沿触发的触发器 2.7.7带异步复位和时钟使能、上升沿触发 的触发器16 17 18 20 20 23 26 30 30 31 31 31 31 2.7.8 D-Latch (锁存器) 2.8 ALU2.9有限状态机(FSM )的设计2.9.1概述2.9.2One-hot 编码 2.9.3 Binary 编码 2.10三态总线2.10.1三态 buffer 2.10.2双向 I/O buffer3常用电路设计3.1CRC 校验码产生器的设计3.1.1概述3.1.2 CRC 校验码产生器的分析与硬件实 现32 33 3.1.3并行 CRC-16校验码产生器的 Verilog HDL 编码3.1.4串行 CRC-16校验码产生器的 Verilog HDL 编码35 37 373.2随机数产生电路设计3.2.1概述3.2.2伪随机序列发生器的硬件实现3.2.3 8位伪随机序列发生器的 Verilog HDL编码37384041 41 41 44 44 443.3双端口RAM仿真模型3.4同步FIFO的设计3.4.1功能描述3.4.2设计代码3.5异步FIFO设计3.5.1概述3.5.2设计代码Verilog 基本电路设计指导书关键词:电路、摘要:本文列举了大量的基本电路的Verilog HDL代码,使初学者能够迅速熟悉基本的HDL建模;同时也列举了一些常用电路的代码,作为设计者的指导。

实验一VERILOG 设计基础一、实验目的1、学习VERILOG的基本语法和编程规则2、掌握通用寄存器等常用基本数字模块的VERILOG描述和基本设计方法3、理解带使能控制和异步清零的8位寄存器的设计原理4、掌握使用VERILOG设计和验证带使能控制和异步清零的8位寄存器的方法5、掌握移位寄存器的设计方法二、实验任务(1) 设计一个带使能控制和异步清零的8位寄存器,实现8位输入的锁存,在时钟的上升沿处得到一个8位的输出和一个8位的反向输出,将结果显示在发光二极管。

模块的物理结构如下:R15 R14 R i R 015 14 i 0图3.49 带使能控制和异步清零的16位寄存器模块的使用注意事项1.数据源D(7..0)一直加在寄存器的数据输入端;2.周期性的时钟信号Clock一直加在寄存器的时钟输入端3.使能信号Enable控制寄存器是否接受数据。

当Enable = '0'时,寄存器不接受数据,保持原来的状态不变;当Enable = '1'时,在时钟信号Clock正跳变时,寄存器接受并保存当时D(7..0)的数据;4.本寄存器其它方面的功能与3.3中所描述的寄存器相同。

完成的参考电路图如下:(2) 设计一个有左、右移位功能的8位寄存器,并仿真验证。

模块的端口描述如下:三、实验步骤1 编写VERILOG代码2功能仿真进行分析与综合,排除语法上的错误建立波形仿真文件,输入激励生成功能仿真网表进行功能仿真,观察输出结果3选择器件DE2_115开发板的使用者请选择CYCLONE IV 4CE1154绑定管脚5 下载验证DE2_115开发板的下载:使用USB-Blaster进行下载四、实验内容通过输入数据先进行计算,并通过实验进行验证。

1)将清零信号Reset(sw17)设为0,将输入信号D(sw7~sw0)设为10101010,观察输出信号Q(ledr7~ledr0)和Qb(ledg7~ledg0),观察并记录输出。

《Verilog HDL硬件描述语言》实验教学大纲

课程代码:MICR3001

课程名称:Verilog HDL硬件描述语言

英文名称:Verilog HDL

实验室名称:微电子实验室

课程学时:72实验学时:18

一、本课程实验教学目的与要求

通过实验要求学生掌握用Verilog HDL硬件描述语言进行集成电路设计的流程和方法。

学会使用Max+plusⅡ,QuartusⅡ设计软件,掌握从HDL源代码的输入→编译→仿真→管脚锁定→下载全过程。

学会用ModelSim设计软件,用Verilog HDL编写测试码对设计模块进行仿真。

二、主要仪器设备及现有台套数

PC,现有35台; EDA实验箱,25套;

1、实验报告:有设计代码,仿真结果,管脚排列,验证结果。

2、考核方式:

(1)实验课的考核方式:教师验收评定成绩。

(2)实验课考核成绩:根据实验完成情况和实验报告是否完整确定,实验课成绩占课程总成绩的10%。

五、实验教材、参考书

1、教材:在编

2、参考书:J.Bhasker著,夏宇闻等译《Verilog HDL入门》.北京航空航天大学出版社.2008出版。

vivado_实验指导书FPGA Basys3开发实验指导书安全使⽤规范●使⽤扩展接⼝扩展电路应⽤前请关闭电路板总开关,避免损坏器件。

●电路板建议在绝缘平台上使⽤,否则可能引起电路板损坏。

●电路使⽤时应防⽌静电。

●液晶显⽰器件或模块结雾时,不要通电⼯作,防⽌电极化学反应,产⽣断线。

●电源正负极、输⼊/输出端⼝定义时需谨慎,避免应接反引起开发板的损坏。

●保持电路板的表⾯清洁。

●⼩⼼轻放,避免不必要的硬件损伤⽬录实验⼀:熟悉VIV ADO编译环境(⼀) (1)⼀、实验⽬的 (1)⼆、实验内容 (1)三、实验要求 (1)四、实验步骤 (1)实验⼆:组合逻辑电路设计 (15)⼀、实验⽬的 (15)⼆、实验内容 (15)三、实验要求 (15)四、实验步骤 (15)五、实验结果 (19)实验三:时序逻辑电路设计 (21)⼀、实验⽬的 (21)⼆、实验内容 (21)三、实验要求 (21)四、实验步骤 (21)五、实验结果 (30)实验四:状态机 (32)⼀、实验⽬的 (32)⼆、实验内容 (32)三、实验要求 (32)四、实验步骤 (32)五、实验结果 (37)实验五:模块化调⽤ (38)⼀、实验⽬的 (38)⼆、实验内容 (38)三、实验要求 (38)实验六:数码管显⽰ (41)⼀、实验⽬的 (41)⼆、实验内容 (41)三、实验要求 (41)四、实验背景知识 (41)五、实验⽅案及实现 (43)六、实验结果 (45)实验七:交通灯 (47)⼀、实验⽬的 (47)⼆、实验内容 (47)三、实验要求 (47)四、实验⽅案及实现 (47)五、实验结果 (52)实验⼋:秒表的设计 (54)⼀、实验⽬的 (54)⼆、实验内容 (54)三、实验要求 (54)四、实验⽅案及实现 (54)五、实验结果 (57)实验九: 蜂鸣器演奏实验 (59)⼀、实验⽬的 (59)⼆、实验内容 (59)三、实验要求 (59)四、实验背景知识 (59)五、实验结果 (64)实验⼗:字符型LCM 驱动 (65)⼀、实验⽬的 (65)⼆、实验内容 (65)三、实验要求 (65)五、实验程序实现 (69)六、实验结果 (74)实验⼗⼀:VGA (76)⼀、实验⽬的 (76)⼆、实验内容 (76)三、实验要求 (76)四、实验背景知识 (76)五、实验结果 (80)实验⼗⼆:PS/2接⼝控制 (81)⼀、实验⽬的 (81)⼆、实验内容 (81)三、实验要求 (81)四、实验背景知识 (81)五、实验⽅案及实现: (84)六、实验结果 (90)实验⼀:熟悉VIVADO编译环境(⼀)⼀、实验⽬的1.熟悉VIV ADO的编译环境;2.了解在VIV ADO环境下运⽤Verilog HDL 语⾔的编程开发流程,包括源程序的编写、编译、模拟仿真及程序下载。

实验1:Q u a r t u s I I基本设计流程体验实验实验步骤:1.启动QuartusII。

2.创建工程。

(1)选择File->NewProjectWizard命令(2)输入工程库文件夹(注意:不要使用Quartus安装目录,不要使用路径中包含中文的目录,例如桌面等)。

输入工程名:MUX41a(3)跳过“添加文件”步骤。

(4)选择目标芯片(EP3C55F484C8)(5)跳过“工具设置”步骤,点击“Finish”。

3.输入设计文件。

(1)选择“File->New”命令,选择VerilogHDLFile选项。

(2)在文本编辑器中输入4选一选择器的代码(使用Case语句)。

(3)选择File->SaveAs命令保存文件。

3.进行全程编译。

编译过程中注意Processing窗口的编译信息。

4.查看编译报告。

扩展实验与思考:1.将代码中Case语句修改为if-else语句,比较两者的编译结果(硬件资源使用情况)。

2.将if-else语句改为不完整条件语句,再次编译后查看编译结果(1.查看综合报告中的警告信息;2.利用Tools>NetlistViewers>RTLViewer查看结构图)。

实验2:ModelSim仿真实验1实验步骤:(1)启动Modelsim;(2)选择File->New->Project建立新工程,工程目录指定为实验1所用目录,加入验证对象文件MUX41a.v;(3)在Project窗口中选中设计文件,单击鼠标右键,选择Compile->CompileAll 编译源代码;如有编译错误,修改源代码;(4)选择Simulate->StartSimulation或点击Simulate按键,选Library窗口中work->MUX41a,点击OK。

(5)在Object窗口中选择需要观察的信号,单击鼠标右键,选择Add->ToWave->SelectedSingals,添加待观察信号至波形窗口;(6)在Transcript窗口中使用force输入激励信号;例如:forceA0(7)在Transcript窗口输入run命令或点击run按键执行仿真,查看结果. (8)改变激励信号,执行仿真并查看结果。

实验指导书实验一:Quartus II软件操作1.实验目的(1)掌握组合逻辑电路的设计方法。

(2)掌握Quartus II 软件的使用方法,以及原理图输入方法。

(3)掌握半加器和全加器的电路设计。

2.Quartus II 的原理图输入法本节通过几个简单的例子向大家介绍FPGA开发软件Quartus II的原理图输入法的设计步骤。

Quartus II 的原理图编辑输入法设计电路时,首先要建立设计项目。

第1步:打开Quartus II。

第2步:新建一个空项目。

执行File->New Project Wizard命令,进入新建项目向导。

如图1-1所示,填入项目的名称,默认项目保存路径在Quartus安装下,建议修改为其他地址,新建一个文件夹作为当前项目存放地址。

图1-1 新建项目向导第3步:执行Next,进入向导的下一页进行项目内文件的添加操作,如果没有文件需要添加进项目,则直接按Next按钮既可。

第4步:指定CPLD/FPGA器件,如图1-2所示,选择芯片系列为“CycloneII”,型号为“EP2C35F672C6N”。

选择型号时,可直接在列表框中查找,也可通过指定封装方式(Package)为“FBGA”、引脚数(Pin count)为“672”以及速度等级(Speed grade)为“6”这3个参数值来进行筛选。

图1-2 器件选择第5步:向导的后面几步不做更改,直接按Next即可,最后按Finish结束向导。

到此即完成了一个项目的新建工作。

第6步:新建一个图形文件。

由于之前建立的项目还是一个空项目,所以接着需要为项目新建文件。

执行File->New命令,在“Device Design Files”选项页中选择“Block Diagram/Schematic File”,然后点击OK按钮。

将该图形文件另存为hadder.bdf。

图形编辑窗口如图1-3所示,窗口左边是图形编辑工具条。

- 3 -图1-3 图形编辑窗口第7步:在图形编辑窗口的空白处双击,打开符号库窗口,如图1-4所示。

实验一QUARTUS Ⅱ的设计流程[输入方式:文本输入、图形输入、波形输入等]一、实验目的:一、掌握QUARTUSⅡ安装进程;二、熟悉QUARTUSⅡ设计环境;3、掌握QUARTUSⅡ的设计进程。

二、实验内容:用文本输入法设计一个半加器。

三、实验步骤:一、安装QUARTUS II。

注:第一次安装QUARTUS要安装license。

二、QUARTUSⅡ设计开发步骤(一)、创建工作文件夹在windows中成立一个文件夹(又称工作库或WORK LIBRARY),用于保留设计工程项目的有关文件。

注:设计工程项目的有关文件不能保留在根目录下,必需保留在一个文件夹之下。

例如成立的文件夹:E:\HADD(二)、启动Quartus II点击QUARTUSⅡ图标打开QUARTUSⅡ设计窗口。

(三)、设计文件输入1、打开输入文件编辑器点击菜单File\new…新成立一个文本设计文件。

用文本输入法输入程序。

程序见附录。

2、保留文件,文件名名同实体名。

后缀.v(四)、全编译(逻辑综合)1、创建工程点击菜单File\New Project Wizard…….进行工程设置。

完成工作文件夹的选定、工程名、顶层设计文件名、编程器件的肯定等工程。

2、编译前的相关设置设置⑴选择PLD芯片:Assignmenmts\Settings\Device弹出的窗口当选择选择芯片。

⑵选择配置芯片的工作方式:Assignmenmts\Settings\Device\Device&Pin Options 弹出的窗口中首选General项,在Options栏当选择Auto-restart-configuration after error.⑶选择配置芯片和编程方式:Assignmenmts\Settings\Device\Device&Pin Options 弹出的窗口当选择Configuration栏,在窗口中设置配置方式,配置芯片和是不是生成紧缩的配置文件。

实验一简单组合逻辑电路的设计一实验要求1.用verilog HDL语言描写出简单的一位数据比较器及其测试程序;2.用测试程序对比较器进行波形仿真测试;画出仿真波形;3. 总结实验步骤和实验结果。

二实验原理与内容这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码://--------------- compare.v -----------------module compare(equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时,//equal输出为0。

endmodule测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块源代码:`timescale 1ns/1ns //定义时间单位。

module comparetest;reg a,b;wire equal;initial //initial常用于仿真时信号的给出。

begina=0;b=0;#100 a=0; b=1;#100 a=1; b=1;#100 a=1; b=0;#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

endcompare compare1(.equal(equal),.a(a),.b(b)); //调用模块。

endmodule实验二 简单时序逻辑电路的设计一 实验要求1.用verilog HDL 语言描写出简单的二分之一分频器及其测试程序;2.用测试程序对分频器进行波形仿真测试;画出仿真波形;3.总结实验步骤和实验结果。

二 实验原理与内容在Verilog HDL 中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。

在可综合的Verilog HDL 模型,我们通常使用always 块和 @(posedge clk)或 @(negedge clk)的结构来表述modelsim6.0使用教程1.modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。

2. 安装3. Modelsim仿真方法Modelsim的仿真分为前仿真和后仿真,下面先具体介绍一下两者的区别。

3.1 前仿真前仿真也称为功能仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电路与理想情况是否一致。

可综合FPGA代码是用RTL级代码语言描述的,其输入为RTL级代码与Testbench.3.2 后仿真后仿真也称为时序仿真或者布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。

其输入文件为从布局布线结果中抽象出来的门级网表、Testbench和扩展名为SDO或SDF的标准时延文件。

SDO或SDF的标准时延文件不仅包含门延迟,还包括实际布线延迟,能较好地反映芯片的实际工作情况。

一般来说后仿真是必选的,检查设计时序与实际的FPGA运行情况是否一致,确保设计的可靠性和稳定性。

3.3 Modelsim仿真的基本步骤Modelsim的仿真主要有以下几个步骤:建立库并映射库到物理目录;编译原代码(包括Testbench;执行仿真。

3.3.1 建立库在执行一个仿真前先建立一个单独的文件夹,后面的操作都在此文件下进行,以防止文件间的误操作。

然后启动Modelsim将当前路径修改到该文件夹下,修改的方法是点File->Change Directory选择刚刚新建的文件夹见下图。

仿真库是存储已编译设计单元的目录,modelsim 中有两类仿真库,一种是工作库,默认的库名为work,另一种是资源库。

Work 库下包含当前工程下所有已经编译过的文件。

所以编译前一定要建一个work 库,而且只能建一个work 库。

资源库存放work 库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被放在不同的资源库内。

例如想要对综合在cyclone 芯片中的设计做后仿真,就需要有一个名为cyclone_ver 的资源库。

映射库用于将已经预编译好的文件所在的目录映射为一个modelsim 可识别的库,库内的文件应该是已经编译过的,在Workspace 窗口内展开该库应该能看见这些文件,如果是没有编译过的文件在库内是看不见的。

建立仿真库的方法有两种。

一种是在用户界面模式下,点File->New->Library出现下面的对话框,选择a new library and a logical mapping to it,在LibraryName 内输入要创建库的名称,然后OK ,即可生成一个已经映射的新库。

另一种 方法是在Transcript 窗口输入以下命令: vlib work /* 库名 */vmap work work/* 映射的逻辑名称 存放的物理路径 */ 如果要删除某库,只需选中该库名,点右键选择Delete 即可。

需要注意的是不要在modelsim 外部的系统盘内手动创建库或者添加文件到库里;也不要modelsim 用到的路径名或文件名中使用汉字,因为modelsim 可能无法识别汉字而导致莫名其妙的错误。

3.3.2 编写与编译测试文件在编写Testbench 之前最好先将要仿真的目标文件编译到工作库中,点Compile->Compile 或需要注意的是不要在modelsim 外部的系统盘内手动创建库或者添加文件到库里;也不要modelsim 用到的路径名或文件名中使用汉字,因为modelsim 可能无法识别汉字而导致莫名其妙的错误。

3.3.2 编写与编译测试文件在编写Testbench 之前最好先将要仿真的目标文件编译到工作库中,点Compile->Compile 或将出现下面的对话框,在Library 中选择工作库,在查找范围内找到要仿真的目标文件,然后点Compile 和Done 。

或在命令行输入vlog fulladder.v 。

此时目标文件已经编译到工作库中,在Library 中展开工作库会发现该文件。

当对要仿真的目标文件进行仿真时需要给文件中的各个输入变量提供激励源,并对输入波形进行的严格定义,这种对激励源定义的文件称为Testbench,即测试台文件。

下面先讲一下Testbench的产生方法。

我们可以在modelsim内直接编写Testbench,而且modelsim还提供了常用的各种模板。

具体步骤如下:⑴.执行File->New->Source->verilog,或者直接点击工具栏上的新建图标,会出现一个verilog 文档编辑页面,在此文档内设计者即可编辑测试台文件。

需要说明的是在Quartus中许多不可综合的语句在此处都可以使用,而且testbench只是一个激励源产生文件,只要对输入波形进行定义以及显示一些必要信息即可,切记不要编的过于复杂,以免喧宾夺主。

⑵.Modelsim提供了很多Testbench模板,我们直接拿过来用可以减少工作量。

点View->Source->Show Language Templates然后会出现一个加载工程,接着你会发现在刚才的文档编辑窗口左边出现了一个Language Templates窗口,见下图。

展开Verilog项,双击Creat Testbench会出现一个创建向导,见下图选择Specify Design Unit工作库下的目标文件,点Next,出现下面对话框可以指定Testbench的名称以及要编译到的库等,此处我们使用默认设置直接点Finish。

这时在Testbench内会出现对目标文件的各个端口的定义还有调用函数接下来,设计者可以自己往Testbench内添加内容了,然后保存为.v格式即可。

按照前面的方法把Testbench文件也编译到工作库中。

3.3.3 执行仿真因为仿真分为前仿真和后仿真,下面分别说明如何操作。

⑴. 前仿真前仿真,相对来说是比较简单的。

在上一步我们已经把需要的文件编译到工作库内了,现在我们只需点simulate->Start Simulation或快捷按钮会出现start simulate对话框。

点击Design标签选择Work库下的Testbench文件,然后点OK即可,也可以直接双击Testbench文件,此时会出现下面的界面。

在主界面中会多出来一个Objects窗口,里面显示Testbench里定义的所有信号引脚,在Workspace里也会多出来一个Sim标签。

右键点击fuladder_tb.v,选择Add->Add to Wave,如下图所示。

然后将出现Wave窗口,现在就可以仿真了,见下图。

窗口里面已经出现了待仿真的各个信号,点将开始执行仿真到100ns,继续点仿真波形也将继续延伸,见下图.若点,则仿真一直执行,直到点才停止仿真。

也可以在命令行输入命令:run @1000则执行仿真到1000ns,后面的1000也可以是别的数值,设计者可以修改。

在下一次运行次命令时将接着当前的波形继续往后仿真。

对于复杂的设计文件,最好是自己编写testbench文件,这样可以精确定义各信号以及各个信号之间的依赖关系等,提高仿真效率。

对于一些简单的设计文件,也可以在波形窗口自己创建输入波形进行仿真。

具体方法是双击work库里的目标仿真文件fulladder.v,然后点workspace窗口中出现的sim标签,右键点击fuladder,选择Add->Add to Wave,如下图所示。