实验七 SOPC 基础实验

- 格式:doc

- 大小:15.73 MB

- 文档页数:96

SOPC实验指导书电信学院实验中心目录第一章EL-SOPC4000实验系统的资源介绍 (1)一、系统功能概述 (1)二、系统硬件资源 (2)三、特别说明 (11)第二章数字可编程设计实验 (12)实验一组合逻辑3-8译码器的设计 (12)第三章基于NIOS的软核设计实验 (23)实验一 Nios软核的设计 (23)实验二外设模块的设计 (27)实验三 SOPC应用系统的生成 (40)实验四 Nios II软核验证以及Nios II IDE软件的介绍 (46)实验五 SOPC系统的PIO验证 (52)实验六基于NIOS的交通灯实验 (55)实验七 7段数码管显示实验 (59)实验八按键及拨码开关实验 (61)实验九 16×16 LED点阵实验 (62)实验十 UART与PC机通信实验 (64)第一章EL-SOPC4000实验系统的资源介绍一、系统功能概述EL-SOPC4000实验箱是集EDA 和SOPC 开发为一体的综合性实验箱,它不仅可以独立完成各种EDA 设计,也可以完成多种SOPC开发。

主CPU适配器E-PLAY-SOPC配合EL-SOPC4000底板,可完成各种基本的EDA实验。

在实验板上有丰富的外围扩展资源,有常用的按键,拨码开关,LED灯,蜂鸣器,交通灯,16x16点阵,数码管,4x4矩阵键盘,AD/DA,CAN功能单元,RS232,RS485,可调时钟输出。

实验板上还集成了一个8寸的VGA接口的液晶屏,可完成视频图像的显示。

由于CPU 适配器E-PLAY-SOPC本身具有E_PLAY接口,只需提供电源即可独立完成功能测试,也可控制用户开发的E_PLAY接口模块。

由于EL-SOPC4000底板加入了两路E_LAB外扩接口,可以配合公司现有的多种E_LAB模块,来完成大学生毕业设计、电子设计竞赛、及创新设计,同时该系统也是从事教学及科研的广大教师和工程师们的理想开发工具,具有极高的灵活性,开放性和可开发性。

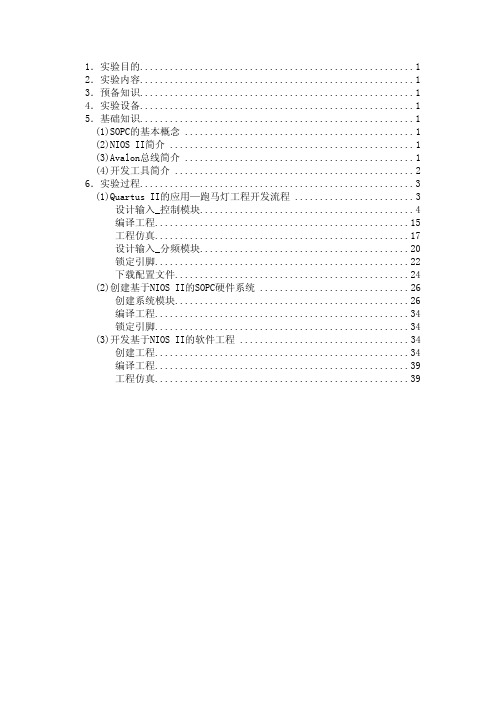

1.实验目的 (1)2.实验内容 (1)3.预备知识 (1)4.实验设备 (1)5.基础知识 (1)(1)SOPC的基本概念 (1)(2)NIOS II简介 (1)(3)Avalon总线简介 (1)(4)开发工具简介 (2)6.实验过程 (3)(1)Quartus II的应用—跑马灯工程开发流程 (3)设计输入_控制模块 (4)编译工程 (15)工程仿真 (17)设计输入_分频模块 (20)锁定引脚 (22)下载配置文件 (24)(2)创建基于NIOS II的SOPC硬件系统 (26)创建系统模块 (26)编译工程 (34)锁定引脚 (34)(3)开发基于NIOS II的软件工程 (34)创建工程 (34)编译工程 (39)工程仿真 (39)SOPC实验指导1.实验目的(1)了解SOPC设计技术(2)了解基于软核的嵌入式系统设计的原理和技术(3)学习并掌握一种系统定制的方法2.实验内容(1) 创建并完成一个基本的跑马灯工程,熟悉Altera综合开发平台Quartus II 的应用(2) 利用SOPC Builder创建基于NIOS II的SOPC硬件系统(3) 利用NIOS II IDE开发应用程序,利用软件实现控制一个LED灯闪烁3.预备知识(1)C语言基础、VHDL或Verilog语言基础(2)程序调试的基础和方法4.实验设备(1)硬件:NIOS II Evaluation Kit(基于Cyclone EP1C12)、PC机;(2)软件:操作系统(Windows98/2000/XP)、Quartus II、NIOS II IDE。

5.基础知识(1)SOPC的基本概念z SOPC即片上可编程系统,这种技术基于FPGA芯片,将处理器、存储器、I/O口等系统设计需要的模块集成到一起,完成整个系统的主要逻辑功能,具有设计灵活,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

(2)NIOS II简介z在很多对速度的要求不是很高的低端应用,Altera将一个软核放入PLD,这 个软核就是NIOS,它只占芯片内部很少的一部分逻辑单元,成本很低。

sopc实验心得

在进行SOPC(系统级可编程器件)实验的过程中,我深刻体会到了它的强大和灵活性。

SOPC是一种基于现场可编程门阵列(FPGA)技术的系统设计方法,它将硬件与软件相结合,可以实现高度集成和可重构的设计。

在实验中,我首先学习了SOPC的基本概念和原理,了解了它的组成部分以及各个组件之间的连接方式。

然后,我利用Quartus II软件进行了仿真和综合,将设计的硬件描述语言(HDL)代码转化为FPGA可以理解的形式。

通过仿真,我可以预先验证设计的正确性,并对其进行修改和优化。

接着,我进行了FPGA的编程和配置,将设计好的逻辑电路加载到FPGA芯片中。

通过这一步骤,我可以将自己的设计直接在硬件上实现,并进行实时的测试和调试。

这种即时性和灵活性是SOPC的一个重要优点,它使得我们能够更加高效地进行系统级设计和验证。

在SOPC实验中,我还学习了使用Nios II软核处理器进行嵌入式系统设计。

Nios II是一款可编程的32位RISC处理器,可以根据需求进行定制和配置。

通过Nios II,我可以在FPGA上实现复杂的嵌入式系统,并编写C语言程序进行控制和操作。

总的来说,SOPC实验让我深入了解了系统级可编程器件的原理和应用。

通过实践,我学会了使用Quartus II软件进行FPGA设计和配置,掌握了硬件描述语言

和嵌入式系统的开发方法。

这些知识和技能对我未来的学习和工作都具有重要的意义,我相信在不久的将来,SOPC技术将会在各个领域得到广泛应用。

《SOPC技术》课程实验报告姓名:学号:班级:同组者:指导教师:高金定信息科学与工程学院2013-2014学年第一学期《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验1:基于LPM的正弦信号发生器的设计二、任务及要求【任务】在QuartusII平台上,采用查找表的设计方法,利用LPM兆功能模块,完成64点(8位)的正弦信号发生器的设计。

正弦信号发生器结构框图如下:【要求】1.数据存储ROM和地址信号发生器均由LPM模块实现。

2.在Quartus II软件上进行时序仿真。

3.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)【思考】1.编写DAC0832数模转换程序,利用示波器观察输出信号波形。

2.如何在此基础上设计方波、三角波等信号发生器?如何实现波形幅度等参数可调?三、实验程序(原理图)四、仿真及结果分析五、硬件验证1、选择模式:2、引脚锁定情况表:六、小结《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验2:基于DSP Builder正弦信号发生器的设计二、任务及要求【任务】采用DSP Builder系统建模的方法,设计正弦信号发生器,要求采用查找表的方法,完成正弦信号发生器模块的建模、仿真。

Signal Compiler【要求】:1.完成模型构建及仿真,得到如下波形图。

2.将模型转换成VHDL硬件描述语言,利用Modelsim软件进行RTL仿真。

3.再在Quartus II软件上进行编译、时序仿真与时序分析。

4.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)三、仿真模型及参数四、仿真及结果分析五、小结《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验3:基于DSP Builder的FIR数字低通滤波器的设计二、任务及要求【任务】:调用DSP Builder模块,设计FIR低通数字滤波器,完成建模与仿真。

黑龙江科技大学SOPC设计基础实验报告学院:黑龙江科技大学学号: ********** 姓名:实验一开发软件使用练习一实验目的实验目的:掌握基于SOPC硬核处理器的设计流程。

二实验设备安装Quartu II的PC、实验箱三实验内容1 添加SOPC硬核1,.创建一个工程,取名。

2.添加.bdf文件,取名和工程名同名。

3.在Tools菜单下打开SOPC Builder。

4.创建系统,取名NIOS2,选择使用Verilog语言。

5.设置系统主频和指定FPGA。

6.加入NIOS2 CPU模块,选择型号,并设置相关参数。

7.依次添加定时器、Butoon PIO、LCD控制器、外部RAM和Flash接口、外部RAM和Flash总线、JTAG UART接口,并将这些模块命名成自己熟悉的名字。

8.分配IP模块的地址和中断号9.配置NIOS2 系统10.生成NIOS2并加入到工程中2 创建PLL器件由于Sdram的时钟是由fpga提供的,所以要创建一个PLL器件来实现对时钟的控制,Quartus II提供了Megawizard Plug-In Manager工具对Plug-In器件以及IP Core进行创建和管理,在Megawizard Plug-In Manager中可以创建各种逻辑门电路以及存储器件。

选择Tools/Megawizard Plug-In Manager点击“Next”,进入Manager,选择“IO/ALTPLL”,选择输出文件类型为“VHDL”,选择输出文件的名字“mypll”点击“Next”,选择器件的速度为8,输出的频率为50MHz,其它设置不变。

点击“Next”,去掉复位、使能等选项点击“Next”,进入Clock c0的设定。

改变“Enter output clock frequency”为50MHz点击“Next”,进入Clock c1的设定,不作改变点击“Next”进入Clock e0的设定。

SOPC设计基础实验报告学院:电子与信息工程学院学号:姓名:实验一开发软件使用练习一实验目的实验目的:掌握基于SOPC硬核处理器的设计流程。

二实验设备安装Quartu II的PC、实验箱三实验内容和步骤1)打开Quarts II 11.1,建立工程2)在菜单栏的File中选择New选项3)默认是New Quartus II Project,选OK4)选择Next,工程目录选择自己新建的文件夹,工程名输入E_Play5)源文件添加,点击Next直接跳过6)选择编号为EP4CE6E22C8的器件7)EDA工具选择,直接点击Next跳过8)项目信息显示,点击Finish完成空工程的建立9)配置无用引脚:在主页面菜单栏点击Assignments,接着在下拉框中选择Device选项,出现如下窗口:As input tri-stated with weak pull-up.点击OK完成。

创建软核处理器系统1)点击菜单栏的Tools,在下拉框中选择SOPC Builder选项,将System Name定为E_Play,下方的Target HDL选VHDL,最后点击OK确认。

2)Device Family选择Cylone IV E,Clock Frequency定为50MHz3)配置软核处理器系统点开左侧Processors总选项,双击Nios II Processor,选择Nios II/e另外在JTAG Debug Module选项中选择第一项,点击Finish完成配置4)配置存储器点开左侧Memories and Memory Controllers总选项,点开第二个On-Chip分选项,双击On-Chip-Memory,在Total memory sizes后输入4096点击Finish,在Onchip-memory2_0上右击,Rename为onchip-memory5)点开左侧Interface Protocols总选项,点开Serial分选项,双击JTAG UART,点击Finish完成6)在jtag_uart_0上右击,Rename为jtag_uart产生软核处理器系统1)双击cpu_0,将Reset Vector和Exception Vector的Memory均设置为onchip_memory,点击Finish完成。

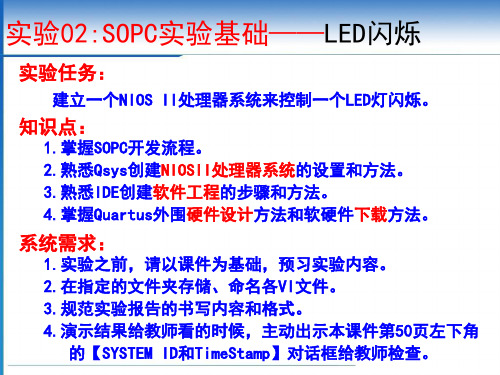

《SOPC技术与应用》实验指导书哈尔滨理工大学自动化学院电子信息科学与技术系2008年10月7日实验一 SOPC快速入门一、实验目的1、学习Quartus II、SOPC Builder、Nios II IDE的基本操作;2、初步了解SOPC的开发流程,基本掌握Nios II软核的定制流程;3、掌握Nios II软件的开发流程;掌握软件的基本调试方法。

二、实验设备硬件:PC机,GW48系列SOPC/EDA实验开发平台;软件:Quartus II 8.0,SOPC Builder 8.0,Nios II IDE 8.0。

三、实验内容建立可用于控制LED闪烁的简单Nios II处理器系统,具体包括:1、在Quartus II中建立一个工程;2、使用SOPC Builder建立并生成一个简单的基于Nios II的硬件系统;3、在Quartus II工程中编译基于Nios II的硬件系统并生成配置文件.sof;4、在Nios II IDE中建立对应硬件系统的用户C/C++工程,编写一简单用户程序,在Nios II IDE中编译程序生成可执行文件.elf;5、将配置文件.sof和可执行文件.elf都下载到FPGA进行调试运行。

四、实验原理控制LED灯闪烁的用户程序代码很小,可将其固化在片内ROM来执行。

变量、堆栈等空间使用片内RAM,不使用任何片外存储器。

整个系统的框图如图1所示。

从图1控制LED闪烁的系统框图可知,其它逻辑与Nios II系统一样可存在于FPGA中。

Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。

为了简单起见,本实验在FPGA内不包括其它逻辑。

图1 控制LED闪烁的系统框图五、实验步骤1、使用Quartus II建立工程2、使用SOPC Builder创建NiosII系统SOPC Builder设计过程不需要按固定顺序进行,本实验采用常用设计步骤。

读者可采用不同的顺序进行SOPC Builder设计。

xx 学院实验题目VGA接口实验学院名称:电子与信息工程学院专业:电信101 嵌入式方向姓名:x x姓名:x x指导教师:xVGA接口实验一.实验目的了解VGA显示原理,熟悉VGA核的使用方法。

二.实验设备硬件:PC机,SmartSOPC教学实验开发平台,带VGA接口的显示器,SmartCore_VGA_PS2_lc6 Nios II系统;软件:Nios II IDE 5.0。

三.实验内容熟悉使用光盘中提供的VGA核(zlg_avalon_vga)。

VGA核(zlg_avalon_vga)采用了SRAM(IS61V25616AL)来做显存,每个像素点的RGB用一位字节来存放,则显示为256色,显存大小为640x480=300KB,格式如表5.2所列。

VGA接口的时序控制由FPGA 完成,主要有4个模块组成:行、场同步信号产生模块、FIFO缓冲模块、显存读/写仲裁模块及SRAM读/写操作模块。

其中后面3个模块主要是用SRAM来构成一个双口RAM。

其他还有一些控制测试模块,如鼠标指针显示模块。

VGA核使用外部SRAM作为显示缓冲。

对VGA进行操作时,也就是对显示缓冲区进行数据填充。

根据不同的数据显示不同的图形或字符。

显示缓冲区共有480行,每一行有640个像素点,使用低10为地址做列地址(0~639),高9位地作为行地址(0~479)。

这样做方便于显示区的数据更改和管理。

但是对现实缓冲区进行操作时要注意地址组合。

实验模板位于:配套光盘\SmartSOPC\SmartSOPC_Software_Template\VGA_test。

四.实验预习要求(1)预习光盘中提供的VGA核(zlg_avalon_vga)的Verilog代码,位于:配套光盘\SmartSOPC\SmartSOPC_Component\ zlg_avalon_vga文件夹中。

(2)熟悉第1章介绍的VGA硬件电路。

五.实验步骤(1)使用试验箱提供的排线按照引脚分配情况从核心板上PACK的45、43、41、23、20、18、16、14、15和17引脚连接到COM1(VGA_COM)的R2、R1、R0、G2、G0、B1、B0、VSYNC、HSYNC。

实验七SOPC 基础实验SOPC即System-On-a-Programmable-Chip(可编程片上系统),本章通过一系列的实验,使学习者对SOPC的应用有较为深刻的认识,并对FPGA的仿真与设计环境有深入的了解,为进一步的工作奠定基础。

7.1 SOPC概述SOPC是PLD和ASIC技术融合的结果,它是一种特殊的嵌入式系统。

首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

由于FPGA无论在逻辑门密度还是在运行频率等诸多方面都取得了长足进步,基于FPGA的嵌入式系统成为SOPC的热点。

目前已经可以把处理器软核、ASIC硬核、数字信号处理器件以及网络控制等各种数字逻辑控制器以IP核的形式集成到FPGA芯片里,构成嵌入式系统。

7.2 基本硬件设计实验嵌入式开发环境EDK是用于设计嵌入式处理系统的集成软件,是利用嵌入式PowerPC™硬处理器核和/或Xilinx MicroBlaze™软处理器核进行Xilinx平台FPGA设计时所需的全部技术文档和IP。

EDK包括硬件部分和软件部分:1. 硬件部分:Xilinx Platform Studio (XPS)XPS是设计嵌入式处理器系统硬件部分的开发环境和用户图形界面。

可使用底层系统生成器BSB(Base System Builder )创建XPS工程,BSB能够快速和有效地创建工程设计。

Xilinx推荐使用BSB向导来创建任何新的嵌入式设计工程,BSB能够满足你所有设计的需要,并且可以帮助你节省很多时间。

使用BSB创建XPS的过程如下:创建顶层工程文件(*.xmp File)选择板型选择和配置处理器选择和配置多重I/O口添加内部的外围设备设置软件观看系统摘要页2. 软件部分:Software Development Kit (SDK)SDK是综合的开发环境,是对XPS的补充,可用C/C++进行嵌入式软件应用的编写和验证。

SDK同其他很多软件开发工具一样,是建立在Eclipse™开放源码基础结构之上的。

1.实验目的(1)学习生成XPS 工程;(2)学习使用Base System Builder(BSB)生成一个系统;(3)下载测试应用程序并检测超级终端输出。

2.实验内容在XPS 中可以使用Base System Builder 生成一个工程,同时生成很多文件,包括:处理器系统文件MHS 文件;原理图文件PBD 文件。

系统一旦生成,处理器系统的网表即可以生成。

整个设计的结构如下:图7-1 设计结构图3.实验准备(1)将光盘下03. Examples of Program \ 03. EDK9.1 实验程序目录下的labs 的文件夹拷贝到E:盘根目录下;(2)将USB 下载电缆与计算机及XUPV2Pro 板的J8 连接好;(3)将RS232 串口线一端与计算机连接好,另一端与板卡的J11 相连接;(4)启动计算机后,将XUPV2Pro 的电源开关SW11 打开到ON 上。

观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源;(5)打开超级终端。

4.实验步骤(1) 打开工程1)选择Start → Programs → Xilinx Platform Studio 9.1i → Xilin x Platform Studio,进入EDK 的XPS 环境;2)选择Base System Builder Wizard 并单击OK 按钮图7-2 操作示意3)弹出Create New Project Using Base System Builder Wizard 对话框,新建工程文件E:/labs/lab1/system.xmp,然后单击OK 按钮;图7-3 操作示意4)选择I would like to create a new design 选项卡,单击Next 按钮;图7-4 操作示意5)弹出Select Board 对话框,选择I would like to create a system for a custom board选项,单击Next 按钮;图7-5 操作示意6)弹出Select Processor 对话框,按照下面内容进行设置并选择PowerPC 作为处理器,单击Next 按钮;Architecture: virtex2pDevice: xc2vp30Package: ff896Speed grade: -7图7-6 操作示意7)弹出Configure Processor 对话框。

按照以下内容进行设置;Reference Clock Frequency: 100 MHz (板上的这个外部时钟源可以用来产生处理器和总线时钟。

时钟频率值取决于FPGA 或者你所使用的板卡,因为某一片上资源(DCMs)可能需要进行定时器乘除法运算)Processor Clock Frequency: 300 MHzBus Clock Frequency: 100 MHzJTAG Debug Interface: FPGA JTAGOn-Chip Memory (OCM) – Data: NONEOn-Chip Memory (OCM) – Instruction: NONE图7-7 操作示意8)单击Next 按钮,弹出Configure IO Interfaces 对话框,单击Add Device 按钮,按照如下选择,单击OK 按钮;IO Interface Type:UARTDevice:RS232图7-8 操作示意9)Peripheral 选择OPB UARTLITE,Baudrate 选择115200,不选择Use Parity选项,其它选项采用默认值;图7-9 操作示意10)单击next 按钮,弹出Add Internal Peripherals 对话框,memory size 选择64 KB。

PLB block RAM 接口控制器被默认添加,此时可单击Add Peripheral 来另外添加内部外设。

在下个实验中,则是在已有工程中添加内部外设的方法;11)单击next 按钮,弹出Software Setup 对话框;12)单击Next 按钮,弹出memory test 设置选项;13)单击Next 按钮,弹出Peripheral test 设置选项;图7-13 操作示意14)单击Next 按钮,弹出System Created 对话框,显示生成的系统概况,单击Generate 按钮。

注意:外围设备的地址映像可能不同;图7-14 操作示意图7-15 操作示意15)单击Finish 按钮,完成生成的工程。

然后单击OK 按钮,选择start usingPlatform Studio,单击OK 按钮;图7-16 操作示意(2)分析生成的工程1)研究生成的工程文件,并浏览黑体字图表显示;图7-17 操作示意2)浏览System Assembly 窗口,观察设计中使用的不同组件,会看到PowerPC 处理器,JTAG 控制器,plb2opb bridge 和plb_bram_if_cntlr 与PowerPC 处理器的一侧相连接,opb_uartlit 与opb 总线相连接;图7-18 操作示意3)双击opb_uartlite,弹出相关的参数,可看到其基地址和高地址的位置;图7-19 操作示意4)不用保存任何改变,关闭对话框。

System Assembly viewer 可以方便的浏览整个系统和总线连接情况。

如果需要更详细的信息,需要采用其它工具。

5)在Project 选项中,打开system.ucf 文件,添加如下内容:Net sys_clk_pin LOC=AJ15;Net sys_clk_pin IOSTANDARD = LVCMOS25;Net sys_rst_pin LOC=AH5;Net sys_rst_pin IOSTANDARD = LVTTL;Net fpga_0_RS232_RX_pin LOC=AJ8;Net fpga_0_RS232_RX_pin IOSTANDARD = LVCMOS25;Net fpga_0_RS232_TX_pin LOC=AE7;Net fpga_0_RS232_TX_pin IOSTANDARD = LVCMOS25;Net fpga_0_RS232_TX_pin SLEW = SLOW;Net fpga_0_RS232_TX_pin DRIVE = 12;(3) 生成硬件网表1)在XPS中, 选择Hardware → Generate Netlist 或者在工具栏点击按钮;图7-20 操作示意2)在生成过程中,注意观察输出窗口的网表生成器;图7-21 操作示意(4) 下载测试应用程序1)在Project Information Area 窗口中的Applications 选项卡中,右键单击TestApp_Peripheral ,选择“Mark to Initialize BRAM”;’图7-22 操作示意2)右键单击TestApp_Memory,取消选择“Mark to initialize BRAMs”;图7-23 操作示意3)选择Device Configuration J Update Bitstream,这个过程将会依次执行run platform generator J Generate the bitstream J library generator J compile theSW code J merge the executable with the bitstream;图7-24 操作示意4)连接XUP 板的下载接口和串行接口,接通电源。

打开超级终端,并完成以下设置;图7-25 操作示意5)选择Device Configuration J Download bitstream;图7-26 操作示意6) 在超级终端可以看到如下输出。

图7-27 显示示意注:如不能下载,则双击etc/download.cmd 文件,将-p 1 改为-p 3。

assignfile -p 1 -file implementation/download.bitprogram -p 1图7-28 操作示意7.3 添加IP 核实验IP核是经过反复验证过的、具有特定功能的模块,它是直接用Xilinx FPGA 底层硬件语言描述的,当然用户也可用Custom IP Core工具定制用户IP。

本实验将指导你在上面一个实验中完成的处理器系统中,如何把系统所需IP核(库IP 核和用户IP核)添加进去。