DRC检测

- 格式:doc

- 大小:53.50 KB

- 文档页数:2

DRC规则检查项⽬PROTEL DXP2004 DRC 规则英⽂对照⼀、Error Reporting 错误报告A:Violations Associated with Buses 有关总线电⽓错误的各类型(共12项)1.bus indices out of range 总线分⽀索引超出范围.2.Bus range syntax errors 总线范围的语法错误3.Illegal bus range values ⾮法的总线范围值4.Illegal bus definitions 定义的总线⾮法5.Mismatched bus label ordering 总线分⽀⽹络标号错误排序6.Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线7.Mismatched bus widths 总线宽度错误8.Mismatched bus section index ordering 总线范围值表达错误,9.Mismatched electrical types on bus 总线上错误的电⽓类型10.Mismatched generics on bus (first index) 总线范围值的⾸位错误11.Mismatched generics on bus (second index) 总线范围值末位错误12.Mixed generics and numeric bus labeling 总线命名规则错误 ) B:Violations Associated Components 有关元件符号电⽓错误(共20项)1.Component Implementations with duplicate pins usage 元件管脚在原理图中重复被使⽤2.Component Implementations with invalid pin mappings 元件管脚在应⽤中和PCB封装中的焊盘不符3.Component Implementations with missing pins in sequence 元件管脚的序号出现序号丢失4.Component contaning duplicate sub-parts 元件中出现了重复的⼦部分5.Component with duplicate Implementations 元件被重复使⽤6. Component with duplicate pins 元件中有重复的管脚7. Duplicate component models ⼀个元件被定义多种重复模型)8. Duplicate part designators 元件中出现标⽰号重复的部分9. Errors in component model parameters 元件模型中出现错误的的参数10.Extra pin found in component display mode 多余的管脚在元件上显⽰.11.Mismatched hidden pin component 元件隐藏管脚的连接不匹配12.Mismatched pin visibility 管脚的可视性不匹配13.Missing component model parameters 元件模型参数丢失14.Missing component models 元件模型丢失15.Missing component models in model files 元件模型不能在模型⽂件中找到16.Missing pin found in component display mode 不见的管脚在元件上显⽰17.Models found in different model locations 元件模型在未知的路径中找到18.Sheet symbol with duplicate entries ⽅框电路图中出现重复的端⼝19.Un-designated parts requiring annotation 未标记的部分需要⾃动标号20.Unused sub-part in component 元件中某个部分未使⽤C:violations associated with document 相关的⽂档电⽓错误(共10项)1.conflicting constraints 约束不⼀致的2.duplicate sheet symbol name 层次原理图中使⽤了重复的⽅框电路图3.duplicate sheet numbers 重复的原理图图纸序号.4.missing child sheet for sheet symbol ⽅框图没有对应的⼦电路图5.missing configuration target 缺少配置对象6.missing sub-project sheet for component 元件丢失⼦项⽬7.multiple configuration targets ⽆效的配置对象8.multiple top-level document ⽆效的顶层⽂件9.port not linked to parent sheet symbol ⼦原理图中的端⼝没有对应到总原理图上的端⼝10.sheet enter not linked to child sheet ⽅框电路图上的端⼝在对应⼦原理图中没有对应端⼝D:violations associated with nets 有关⽹络电⽓错误(共19项)1.adding hidden net to sheet 原理图中出现隐藏⽹络2.adding items from hidden net to net 在隐藏⽹络中添加对象到已有⽹络中3.auto-assigned ports to device pins ⾃动分配端⼝到设备引脚4.duplicate nets 原理图中出现重名的⽹络5.floating net labels 原理图中有悬空的⽹络标签6.global power-objects scope changes 全局的电源符号错误/doc/661647277.htmlparameters with no name ⽹络属性中缺少名称/doc/661647277.htmlparameters with no value ⽹络属性中缺少赋值/doc/661647277.htmls containing floating input pins ⽹络包括悬空的输⼊引脚/doc/661647277.htmls with multiple names 同⼀个⽹络被附加多个⽹络名/doc/661647277.htmls with no driving source ⽹络中没有驱动/doc/661647277.htmls with only one pin ⽹络只连接⼀个引脚/doc/661647277.htmls with possible connection problems ⽹络可能有连接上的错误14.signals with multiple drivers 重复的驱动信号15.sheets containing duplicate ports 原理图中包含重复的端⼝16.signals with load 信号⽆负载17.signals with drivers 信号⽆驱动18.unconnected objects in net ⽹络中的元件出现未连接对象19.unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)1.No Error ⽆错误2.Object not completely within sheet boundaries 原理图中的对象超出了图纸边框3.Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型1.same parameter containing different types 相同的参数出现在不同的模型中2.same parameter containing different values 相同的参数出现了不同的取值⼆、Comparator 规则⽐较A:Differences associated with components 原理图和PCB上有关的不同(共16项)1.Changed channel class name 通道类名称变化2.Changed component class name 元件类名称变化3.Changed net class name ⽹络类名称变化4.Changed room definitions 区域定义的变化5.Changed Rule 设计规则的变化6.Channel classes with extra members 通道类出现了多余的成员/doc/661647277.htmlponent classes with extra members 元件类出现了多余的成员8.Difference component 元件出现不同的描述9.Different designators 元件标⽰的改变10.Different library references 出现不同的元件参考库11.Different types 出现不同的标准12.Different footprints 元件封装的改变13.Extra channel classes 多余的通道类14.Extra component classes 多余的元件类15.Extra component 多余的元件16.Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关⽹络不同(共6项)1.Changed net name ⽹络名称出现改变2.Extra net classes 出现多余的⽹络类3.Extra nets 出现多余的⽹络4.Extra pins in nets ⽹络中出现多余的管脚5.Extra rules ⽹络中出现多余的设计规则/doc/661647277.htmlclass with Extra members ⽹络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)1.Changed parameter types 改变参数类型2.Changed parameter value 改变参数的取值3.Object with extra parameter 对象出现多余的参数【Violations Associated with Buses】栏——总线电⽓错误类型(1)【Bus indices out of range】:总线分⽀索引超出范围。

drc检查项目

DRC(Design Rule Check)是一种电路设计中常用的自动化检

查工具,用于检查设计是否符合规定的设计规则。

DRC检查

项目一般包括以下内容:

1. 线宽规则:检查线宽是否满足要求,例如最小线宽、最小间距等。

2. 线与层规则:检查线与金属层、电源层等的接触情况,确保没有未连接或过度连接的情况。

3. 路由规则:检查布线是否满足布线规则,例如最小径迹宽度、最小径迹间距等。

4. 电气规则:检查电路是否符合电气规则,例如电源与地线是否连接良好、信号线与电源线之间是否有足够的间距等。

5. 元件规则:检查元件的引脚、符号等是否正确,且与电路中的连接一致。

这些检查项目可以帮助设计工程师及时发现设计中的问题,避免制造出错误的电路板。

版图的物理验证版图的物理验证主要有DRC,ERC(电气规则检查)和LVS三种方法。

DRC 表示设计规则检查,是Design Rule Checking的缩写,LVS是Layout Versus Schematic的缩写,ERC是Electrical Rule Checking。

DRC用来检查版图的几何图形符合工艺规则要求,以便芯片能在工艺线上生产出来;LVS把设计得到的版图和逻辑网表进行比较,检查各器件大小和连接关系是否完全一致;ERC主要是检查版图电性能(如衬底是否正确接电源或地,又无栅极悬空等)以保证各器件能正常工作。

物理验证成功则可以出带(Tapeout),或生成macro cell 做作为整个设计的一部份来使用,数据格式一般采用GDSII。

下面以Mentor公司的物理验证Calibre来说明版图的验证过程。

1.ANT流程2.DRC流程DRC验证需要输入版图文件(GDSII格式)和规则文件,规则文件一般由厂商提供。

Mentor 公司的Calibre软件是DRC方面的主流工具。

其规则文件的语法简单,但规则较繁杂。

规则文件通常包括描述模块(Description Block)、输入层模块(Inputlayer Block)、操作模块(Operation Block)三个部分。

每一个模块有一个开始标志(如:*DESCRIPTION)和结束标志(*END)。

描述模块定义了Dracula运行环境。

包括运行模式、基本单元名、输入/输出设备、文件名、格式、图形比例元素、网格大小、输出记录文件、警告消息显示等。

输入层模块把布局图的层名或层编号和Calibre的层名对应起来,并提供Calibre进行验证所需的其他关于层的信息。

主要是:要输出的层、层名、掩膜顺序、要输出的层、文本层。

操作层定义要进行的操作和应用程序并且标出错误。

它定义的操作类型有:逻辑、电气节点、缩放、参数、空间、ERC、DRC、LVS、LPE和PRE。

第27卷 第3期核电子学与探测技术Vol.27 No.3 2007年 5月Nuclear Elect ronics &Detection TechnologyMa y 2007 箱包D R 2C T 检测系统断层定位控制设计黄毅斌,向新程,裘伟东(清华大学核能与新能源技术研究院,北京100084) 摘要:简要介绍了箱包DR 2CT 检测系统的原理,分析了控制子系统的功能,并详细介绍了控制子系统断层定位P ID 控制方案设计及其参数整定方法。

基于PID 控制的控制子系统大大减小了定位误差,其断层定位精度满足设计目标和要求。

关键词:箱包DR 2CT 检测系统;定位控制;P ID 控制中图分类号: TL81 文献标识码: A 文章编号: 025820934(2007)0320444203收稿日期:2006211221作者简介黄毅斌(),男,福建人,清华大学核研院助研,博士,从事辐射技术研究工作1 箱包DR 2C T 检测系统简介自从“9.11”之后,各国的航空业都在不断加强自身的安全防范系统,并对旅客行李和航空货运安全检查提出了更严格的要求。

国际航空界为了避免和遏制恐怖事件的发生,急需增强现有的箱包行李X 射线检测系统的功能,使之具备迅速发现爆炸物、易燃品等违禁物并自动报警的功能,即“物性判别”功能。

清华大学核研院在成功研制出60Co 集装箱C T 检测系统的基础上,针对箱包行李检查的特点,攻克技术难关,研发出了我国具有自主知识产权的箱包DR 2C T 检测系统[122]。

箱包DR 2C T 检测系统的结构示意图如图1所示。

所研制的箱包DR 2C T 检测系统由两个子检测系统串联组合而成:依靠平移扫描获得投影图像的DR 子检测系统;依靠旋转扫描获得断层图像的C T 子检测系统。

箱包DR 2CT 检测系统的两个子检测系统通过一套皮带输送机连接。

前部的DR 子检测系统可实时获取箱包的DR 投影图像,借此能了解其中物品的详细情况,并确定需要进行断层扫描的可疑部位。

drc和lvs验证原理DRC和LVS验证原理1. 什么是DRC和LVS验证DRC和LVS是集成电路设计中非常重要的验证流程,用于确保芯片设计的正确性和可靠性。

DRC全称为Design Rule Check(设计规则检查),LVS全称为Layout versus Schematic(布局与原理图相对比)。

DRC验证主要检查物理设计是否符合制造工艺规范,而LVS验证主要检查布局和原理图之间的一致性。

2. DRC验证原理•DRC验证主要通过规则检查器对物理设计进行分析和验证,通常包括以下几个方面:–尺寸规则检查:检查晶体管、连线等元件的尺寸是否符合制造工艺要求;–布局规则检查:检查器件间的间距、连线的宽度等是否符合要求;–链接规则检查:检查连接的连线长度、电容等是否符合要求;–电压规则检查:检查是否存在电压冲突、短路等问题。

•DRC验证的目标是确保物理设计满足制造工艺的要求,避免制造工艺的失败和电路性能的问题。

3. LVS验证原理•LVS验证主要通过比较布局和原理图之间的差异来检查设计的正确性,通常包括以下几个步骤:1.提取布局:将物理设计中的连线、晶体管等元件提取出来,生成布局;2.提取原理图:从设计工具中提取原理图;3.生成SPICE模型:将原理图转换为SPICE模型,用于电路模拟;4.进行电路模拟:使用SPICE模拟器对提取的布局和原理图进行电路模拟;5.比较结果:对模拟结果进行比较,检查是否存在差异。

•LVS验证的目标是确保布局和原理图的一致性,避免因布局错误导致的电路功能故障和性能问题。

4. DRC和LVS验证之间的关系DRC和LVS验证是互补的,虽然都是针对芯片设计的不同方面进行验证,但两者之间相互影响: - DRC验证主要考虑制造工艺的要求,而LVS验证主要考虑设计功能的正确性,因此,DRC验证的结果可以为LVS验证提供一定的参考; - 如果DRC验证不通过,表示物理设计存在问题,可能导致LVS验证失败; - 如果LVS验证不通过,表示布局和原理图不一致,可能需要对物理设计进行调整,以修复问题。

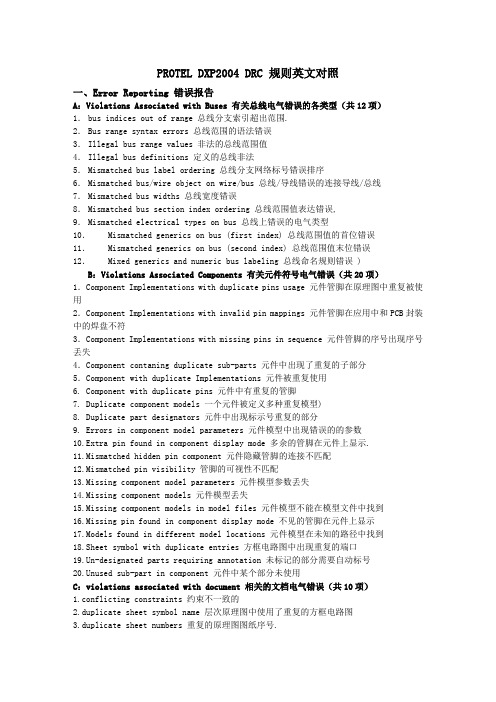

PROTEL DXP2004 DRC 规则英文对照一、Error Reporting 错误报告A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)1.bus indices out of range 总线分支索引超出范围.2.Bus range syntax errors 总线范围的语法错误3.Illegal bus range values 非法的总线范围值4.Illegal bus definitions 定义的总线非法5.Mismatched bus label ordering 总线分支网络标号错误排序6.Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线7.Mismatched bus widths 总线宽度错误8.Mismatched bus section index ordering 总线范围值表达错误,9.Mismatched electrical types on bus 总线上错误的电气类型10.Mismatched generics on bus (first index) 总线范围值的首位错误11.Mismatched generics on bus (second index) 总线范围值末位错误12.Mixed generics and numeric bus labeling 总线命名规则错误 ) B:Violations Associated Components 有关元件符号电气错误(共20项)1.Component Implementations with duplicate pins usage 元件管脚在原理图中重复被使用2.Component Implementations with invalid pin mappings 元件管脚在应用中和PCB封装中的焊盘不符3.Component Implementations with missing pins in sequence 元件管脚的序号出现序号丢失4.Component contaning duplicate sub-parts 元件中出现了重复的子部分5.Component with duplicate Implementations 元件被重复使用6. Component with duplicate pins 元件中有重复的管脚7. Duplicate component models 一个元件被定义多种重复模型)8. Duplicate part designators 元件中出现标示号重复的部分9. Errors in component model parameters 元件模型中出现错误的的参数10.Extra pin found in component display mode 多余的管脚在元件上显示.11.Mismatched hidden pin component 元件隐藏管脚的连接不匹配12.Mismatched pin visibility 管脚的可视性不匹配13.Missing component model parameters 元件模型参数丢失14.Missing component models 元件模型丢失15.Missing component models in model files 元件模型不能在模型文件中找到16.Missing pin found in component display mode 不见的管脚在元件上显示17.Models found in different model locations 元件模型在未知的路径中找到18.Sheet symbol with duplicate entries 方框电路图中出现重复的端口19.Un-designated parts requiring annotation 未标记的部分需要自动标号20.Unused sub-part in component 元件中某个部分未使用C:violations associated with document 相关的文档电气错误(共10项)1.conflicting constraints 约束不一致的2.duplicate sheet symbol name 层次原理图中使用了重复的方框电路图3.duplicate sheet numbers 重复的原理图图纸序号.4.missing child sheet for sheet symbol 方框图没有对应的子电路图5.missing configuration target 缺少配置对象6.missing sub-project sheet for component 元件丢失子项目7.multiple configuration targets 无效的配置对象8.multiple top-level document 无效的顶层文件9.port not linked to parent sheet symbol 子原理图中的端口没有对应到总原理图上的端口10.sheet enter not linked to child sheet 方框电路图上的端口在对应子原理图中没有对应端口D:violations associated with nets 有关网络电气错误(共19项)1.adding hidden net to sheet 原理图中出现隐藏网络2.adding items from hidden net to net 在隐藏网络中添加对象到已有网络中3.auto-assigned ports to device pins 自动分配端口到设备引脚4.duplicate nets 原理图中出现重名的网络5.floating net labels 原理图中有悬空的网络标签6.global power-objects scope changes 全局的电源符号错误 parameters with no name 网络属性中缺少名称 parameters with no value 网络属性中缺少赋值s containing floating input pins 网络包括悬空的输入引脚s with multiple names 同一个网络被附加多个网络名s with no driving source 网络中没有驱动s with only one pin 网络只连接一个引脚s with possible connection problems 网络可能有连接上的错误14.signals with multiple drivers 重复的驱动信号15.sheets containing duplicate ports 原理图中包含重复的端口16.signals with load 信号无负载17.signals with drivers 信号无驱动18.unconnected objects in net 网络中的元件出现未连接对象19.unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)1.No Error 无错误2.Object not completely within sheet boundaries 原理图中的对象超出了图纸边框3.Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型1.same parameter containing different types 相同的参数出现在不同的模型中2.same parameter containing different values 相同的参数出现了不同的取值二、Comparator 规则比较A:Differences associated with components 原理图和PCB上有关的不同(共16项)1.Changed channel class name 通道类名称变化2.Changed component class name 元件类名称变化3.Changed net class name 网络类名称变化4.Changed room definitions 区域定义的变化5.Changed Rule 设计规则的变化6.Channel classes with extra members 通道类出现了多余的成员ponent classes with extra members 元件类出现了多余的成员8.Difference component 元件出现不同的描述9.Different designators 元件标示的改变10.Different library references 出现不同的元件参考库11.Different types 出现不同的标准12.Different footprints 元件封装的改变13.Extra channel classes 多余的通道类14.Extra component classes 多余的元件类15.Extra component 多余的元件16.Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关网络不同(共6项)1.Changed net name 网络名称出现改变2.Extra net classes 出现多余的网络类3.Extra nets 出现多余的网络4.Extra pins in nets 网络中出现多余的管脚5.Extra rules 网络中出现多余的设计规则 class with Extra members 网络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)1.Changed parameter types 改变参数类型2.Changed parameter value 改变参数的取值3.Object with extra parameter 对象出现多余的参数【Violations Associated with Buses】栏——总线电气错误类型(1)【Bus indices out of range】:总线分支索引超出范围。

PROTEL DXP2004 DRC 规则英文对照一、Error Reporting 错误报告A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)1.bus indices out of range 总线分支索引超出范围.2.Bus range syntax errors 总线范围的语法错误3.Illegal bus range values 非法的总线范围值4.Illegal bus definitions 定义的总线非法5.Mismatched bus label ordering 总线分支网络标号错误排序6.Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线7.Mismatched bus widths 总线宽度错误8.Mismatched bus section index ordering 总线范围值表达错误,9.Mismatched electrical types on bus 总线上错误的电气类型10.Mismatched generics on bus (first index) 总线范围值的首位错误11.Mismatched generics on bus (second index) 总线范围值末位错误12.Mixed generics and numeric bus labeling 总线命名规则错误 ) B:Violations Associated Components 有关元件符号电气错误(共20项)1.Component Implementations with duplicate pins usage 元件管脚在原理图中重复被使用2.Component Implementations with invalid pin mappings 元件管脚在应用中和PCB封装中的焊盘不符3.Component Implementations with missing pins in sequence 元件管脚的序号出现序号丢失4.Component contaning duplicate sub-parts 元件中出现了重复的子部分5.Component with duplicate Implementations 元件被重复使用6. Component with duplicate pins 元件中有重复的管脚7. Duplicate component models 一个元件被定义多种重复模型)8. Duplicate part designators 元件中出现标示号重复的部分9. Errors in component model parameters 元件模型中出现错误的的参数10.Extra pin found in component display mode 多余的管脚在元件上显示.11.Mismatched hidden pin component 元件隐藏管脚的连接不匹配12.Mismatched pin visibility 管脚的可视性不匹配13.Missing component model parameters 元件模型参数丢失14.Missing component models 元件模型丢失15.Missing component models in model files 元件模型不能在模型文件中找到16.Missing pin found in component display mode 不见的管脚在元件上显示17.Models found in different model locations 元件模型在未知的路径中找到18.Sheet symbol with duplicate entries 方框电路图中出现重复的端口19.Un-designated parts requiring annotation 未标记的部分需要自动标号20.Unused sub-part in component 元件中某个部分未使用C:violations associated with document 相关的文档电气错误(共10项)1.conflicting constraints 约束不一致的2.duplicate sheet symbol name 层次原理图中使用了重复的方框电路图3.duplicate sheet numbers 重复的原理图图纸序号.4.missing child sheet for sheet symbol 方框图没有对应的子电路图5.missing configuration target 缺少配置对象6.missing sub-project sheet for component 元件丢失子项目7.multiple configuration targets 无效的配置对象8.multiple top-level document 无效的顶层文件9.port not linked to parent sheet symbol 子原理图中的端口没有对应到总原理图上的端口10.sheet enter not linked to child sheet 方框电路图上的端口在对应子原理图中没有对应端口D:violations associated with nets 有关网络电气错误(共19项)1.adding hidden net to sheet 原理图中出现隐藏网络2.adding items from hidden net to net 在隐藏网络中添加对象到已有网络中3.auto-assigned ports to device pins 自动分配端口到设备引脚4.duplicate nets 原理图中出现重名的网络5.floating net labels 原理图中有悬空的网络标签6.global power-objects scope changes 全局的电源符号错误 parameters with no name 网络属性中缺少名称 parameters with no value 网络属性中缺少赋值s containing floating input pins 网络包括悬空的输入引脚s with multiple names 同一个网络被附加多个网络名s with no driving source 网络中没有驱动s with only one pin 网络只连接一个引脚s with possible connection problems 网络可能有连接上的错误14.signals with multiple drivers 重复的驱动信号15.sheets containing duplicate ports 原理图中包含重复的端口16.signals with load 信号无负载17.signals with drivers 信号无驱动18.unconnected objects in net 网络中的元件出现未连接对象19.unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)1.No Error 无错误2.Object not completely within sheet boundaries 原理图中的对象超出了图纸边框3.Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型1.same parameter containing different types 相同的参数出现在不同的模型中2.same parameter containing different values 相同的参数出现了不同的取值二、Comparator 规则比较A:Differences associated with components 原理图和PCB上有关的不同(共16项)1.Changed channel class name 通道类名称变化2.Changed component class name 元件类名称变化3.Changed net class name 网络类名称变化4.Changed room definitions 区域定义的变化5.Changed Rule 设计规则的变化6.Channel classes with extra members 通道类出现了多余的成员ponent classes with extra members 元件类出现了多余的成员8.Difference component 元件出现不同的描述9.Different designators 元件标示的改变10.Different library references 出现不同的元件参考库11.Different types 出现不同的标准12.Different footprints 元件封装的改变13.Extra channel classes 多余的通道类14.Extra component classes 多余的元件类15.Extra component 多余的元件16.Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关网络不同(共6项)1.Changed net name 网络名称出现改变2.Extra net classes 出现多余的网络类3.Extra nets 出现多余的网络4.Extra pins in nets 网络中出现多余的管脚5.Extra rules 网络中出现多余的设计规则 class with Extra members 网络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)1.Changed parameter types 改变参数类型2.Changed parameter value 改变参数的取值3.Object with extra parameter 对象出现多余的参数【Violations Associated with Buses】栏——总线电气错误类型(1)【Bus indices out of range】:总线分支索引超出范围。

基于Cadence软件DRACULA工具的DRC检查DRC(Design Rule Check)大致分为三大步:1、准备工作,技术文件的导入以及修改2、导出GDS数据3、对GDS文件进行DRC检查1、准备工作,技术文件的导入以及修改首先,新建一个目录DRC(名字可以任意取,自己知道就可以)用来作DRC 检查,主要用于存放技术文件,GDS数据,以及检查结果等等。

做DRC检查需要有DRC技术文件,该技术文件由工艺厂商提供。

把技术文件放到DRC目录下。

注意,由于LINUX系统和WIN系统的差别,这里需要对技术文件进行处理,否则DRACULA读入技术文件时会出错,转换命令为:dos2unix ,这里的两个分别是转换前后的技术文件。

转换完毕之后,需要把program这一行注释掉(如果有的话),大约在70行左右,方法是,在行首插入分号(;)。

CSMC06的技术文件是需要修改的,CSMC05好像不用,具体自己看吧。

2、导出GDS数据由于DRACULA工具不能直接对图形化的版图进行检查,所以需要先把LAYOUT 倒成GDS数据。

下面介绍GDS数据的导出。

1.icfb-log窗口――>file――>Export――>stream2.点击Library Browser来选择LAYOUT所在的位置,在output file一栏填写导出GDS数据的名称,也可以在前面加入路径,比如:./DRC/***.GDS,这样,导出的GDS数据就在DRC目录下,否则就在默认的目录下。

3.全部填好了啊,那就点“OK”吧,然后等待,弹出窗口,提示:“GDS文件导出成功!”。

好了,GDS的导出就完成了。

3、对GDS文件进行DRC检查1.修改DRC技术文件,indisk的值改为输入的GDS文件名(代后缀名);primary的值改为topcell的名称(约在68行左右),保存退出;2.启动控制台:首先进入DRC目录 cd DRC输入命令 PDRACULA输入命令 /g (读取技术文件)输入命令 /f输入命令 ./ (运行检查程序)。

双随机检查方案1. 引言双随机检查(Double Random Check,DRC)方案是一种在质量控制过程中常用的统计方法。

它通过对样本进行双重随机抽样和检查,能够有效地检测缺陷和错误,提高产品质量和生产效率。

本文将详细介绍双随机检查方案的原理、应用和操作步骤。

2. 原理双随机检查方案基于统计学的抽样原理,通过对样本进行双重随机抽取和检查,来推断整体批次的质量水平。

它的基本原理是,首先随机选择一批样本进行初次抽检,然后再从初次抽检通过的样本中随机选择一部分进行复检。

如果初次抽检和复检的结果都符合要求,则批次被认为是合格的;如果有一个或多个样本不符合要求,则批次被认为是不合格的。

3. 应用场景双随机检查方案广泛应用于生产流程的各个环节,特别是在大批量生产中具有重要作用。

以下是一些典型的应用场景:3.1 制造业在制造业中,双随机检查方案可以用于检验原材料、半成品和成品的质量。

通过对抽样的材料进行检查,可以及早发现和纠正生产过程中的问题,确保产品的质量符合标准要求。

3.2 贸易业在贸易业中,双随机检查方案可以用于检查进口和出口货物的质量和符合性。

通过对随机抽样的货物进行检查,可以确保货物的质量和规范符合贸易合同和相关法规的要求,避免纠纷和损失。

3.3 服务行业在服务行业中,双随机检查方案可以用于检查服务质量和合规性。

例如,在餐饮业中,可以对随机抽取的菜品进行检查,以确保食品安全和卫生条件符合相关规定。

4. 操作步骤双随机检查方案的操作步骤通常包括以下几个阶段:4.1 确定抽检样本数根据生产批次的大小和质量要求,确定需要抽检的样本数量。

一般情况下,样本数量要足够大,以能够统计出可靠的结果。

4.2 初次抽检根据抽检样本数,随机选择一批样本进行初次抽检。

抽检的方式可以使用随机数表、随机数生成器或随机抽签等方法,确保抽检的过程是随机的,不受个人主观因素的影响。

4.3 复检从初次抽检通过的样本中,再次随机选择一部分进行复检。

OrCAD 培训教材Capture Features●Vendor specific libraries●Integration with all other OrCAD EDA tools●Netlist interface to other PCB desig1packages●Cross-probing and bi-directional annotation between schematicand PCB designs.●Integration of company parts database (Capture CIS).●Customized Bill of Materials reportsPSpice Features●提供一个对电路进行仿真的环境●分析验证你的电路●对电路进行参数优化●对器件的模型参数进行提取Layout Features●提供对PCB板进行设计的环境●周到齐全的EDA软件接口●功能强大的机械设计环境(Visual CCAD)●与制作加工相结合的GerbTool工具●功能多样的策略与模板OrCAD的基础知识OrCAD常用文档类型✧*.opj—项目管理文件✧*.dsn—电路图文件✧*.olb—图形符号库文件✧*.lib—仿真模型描述库文件✧*.mnl—网络表文件✧*.max—电路板文件✧*.tch—技术档文件✧*.gbt—光绘文件✧*.llb—PCB封装库文件✧*.log *.lis—记录说明文件✧*.tpl—板框文件✧*.sf—策略档文件OrCAD软件包含的库1、*.olb-Capture专用的图形符号库只有电气特性,没有仿真特性的库。

此类库没有相应的*.lib库,且器件属性中没有PspiceTemplate属性。

能够利用PSpice进行仿真的库。

此类库有相应的*.lib库,且器件属性中有PspiceTemplate属性。

2、*.lib-PSpice仿真库,利用Spice语言对Capture中的图形符号进行功能定义与描述,可以编辑。