实验二 组合逻辑电路

- 格式:doc

- 大小:60.00 KB

- 文档页数:3

实验二组合逻辑电路的设计一、实验目的1.设计8段译码器、两路4位二进制比较器,并在实验装置上验证所设计的电路;2.学习用VHDL语句进行逻辑描述。

二、实验要求用VHDL设计8段译码器、两路4位二进制比较器,对CPLD器件进行配置及下载来验证自己的设计,验证电路的外围器件可选用按键输入、指示灯输出。

三、设计方案按键的状态作为输入,输出对应数字的编码,连接到数码管上面可以看到数码管显示对应的数值。

代码:LED.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity LED isport(number:in std_logic_vector(3 downto 0);ledout:out std_logic_vector(7 downto 0));end;architecture u1 of LED isbeginwith number selectledout<="00111111"when"0000", --0"00000110"when"0001", --1"01011011"when"0010", --2"01001111"when"0011", --3"01100110"when"0100", --4"01101101"when"0101", --5"01111101"when"0110", --6"00000111"when"0111", --7"01111111"when"1000", --8"01101111"when"1001", --9"01110111"when"1010", --A"01111100"when"1011", --B"00111001"when"1100", --C"01011110"when"1101", --D"01111001"when"1110", --E"01110001"when"1111"; --Fend;实验结果:按下试验箱的按键后,数码管显示按键的状态。

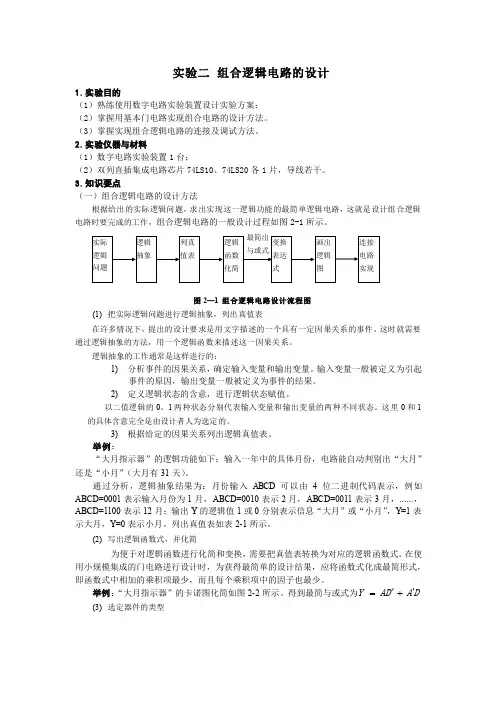

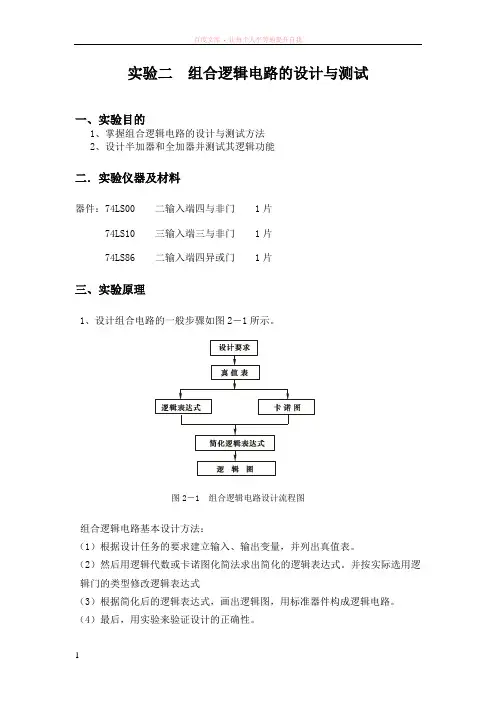

实验二组合逻辑电路的设计与测试一、实验目的1、掌握组合逻辑电路的设计与测试方法2、设计半加器和全加器并测试其逻辑功能二.实验仪器及材料器件:74LS00 二输入端四与非门 1片74LS10 三输入端三与非门 1片74LS86 二输入端四异或门 1片三、实验原理1、设计组合电路的一般步骤如图2-1所示。

图2-1 组合逻辑电路设计流程图组合逻辑电路基本设计方法:(1)根据设计任务的要求建立输入、输出变量,并列出真值表。

(2)然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。

并按实际选用逻辑门的类型修改逻辑表达式(3)根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。

(4)最后,用实验来验证设计的正确性。

2、 组合逻辑电路设计举例设计任务: 用“与非”门设计一个四个人的表决电路。

当四个输入端中有三个或四个为“1”时,输出端才为“1”。

(同意用"1"表示,反对用"0"表示;决议通过用"1"表示,不通过用"0"表示。

)设计步骤:(1)根据题意列出真值表如表2-1所示,再填入卡诺图表2-2中。

表2-2(2) 由卡诺图得出逻辑表达式,并演化成“与非”的形式 Z =ABC +BCD +ACD +ABD =ABC ACD BCD ABC ⋅⋅⋅(3)根据逻辑表达式画出用“与非门”构成的逻辑电路如图2-2所示。

图2-2 表决电路逻辑图(4)用实验验证逻辑功能A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1B 0 0 0 0 1 1 11 0 0 0 0 1 1 1 1C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Z 0 0 0 0 0 0 0 1 0 00 1 0 1 1 1 CD AB00 01 11 10 0001 111 1 1 110 1在实验装置适当位置选定三个14P插座,按照集成块定位标记插好集成块74LS20。

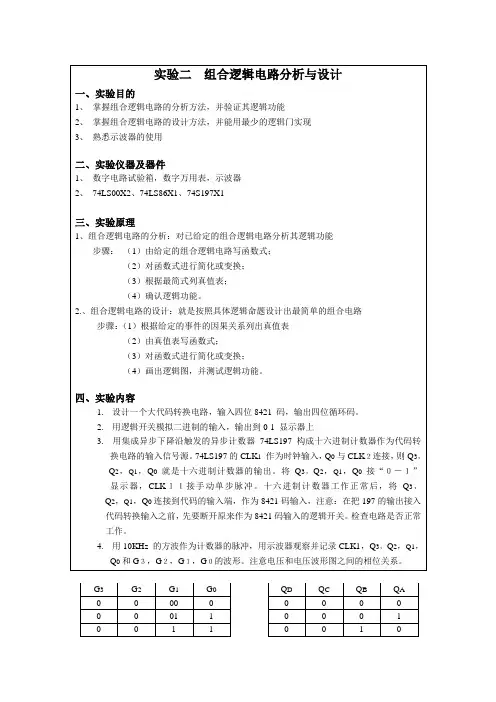

实验二组合逻辑电路分析与设计一、实验目的1、掌握组合逻辑电路的分析方法,并验证其逻辑功能2、掌握组合逻辑电路的设计方法,并能用最少的逻辑门实现3、熟悉示波器的使用二、实验仪器及器件1、数字电路试验箱,数字万用表,示波器2、74LS00X2、74LS86X1、74S197X1三、实验原理1、组合逻辑电路的分析:对已给定的组合逻辑电路分析其逻辑功能步骤:(1)由给定的组合逻辑电路写函数式;(2)对函数式进行简化或变换;(3)根据最简式列真值表;(4)确认逻辑功能。

2.、组合逻辑电路的设计:就是按照具体逻辑命题设计出最简单的组合电路步骤:(1)根据给定的事件的因果关系列出真值表(2)由真值表写函数式;(3)对函数式进行简化或变换;(4)画出逻辑图,并测试逻辑功能。

四、实验内容1. 设计一个大代码转换电路,输入四位8421 码,输出四位循环码。

2. 用逻辑开关模拟二进制的输入,输出到0-1 显示器上3. 用集成异步下降沿触发的异步计数器74LS197 构成十六进制计数器作为代码转换电路的输入信号源。

74LS197的CLK1作为时钟输入,Q0与CLK2连接,则Q3,Q2,Q1,Q0就是十六进制计数器的输出。

将Q3,Q2,Q1,Q0接“0-1”显示器,CLK11接手动单步脉冲。

十六进制计数器工作正常后,将Q3,Q2,Q1,Q0连接到代码的输入端,作为8421码输入,注意:在把197的输出接入代码转换输入之前,先要断开原来作为8421码输入的逻辑开关。

检查电路是否正常工作。

4. 用10KHz 的方波作为计数器的脉冲,用示波器观察并记录CLK1,Q3,Q2,Q1,Q0和G3,G2,G1,G0的波形。

注意电压和电压波形图之间的相位关系。

G3G2G1G0Q D Q C Q B Q A0 0 00 0 0 0 0 00 0 01 1 0 0 0 10 0 1 1 0 0 1 00 0 1 0 0 0 1 10 1 1 0 0 1 0 00 1 1 1 0 1 0 10 1 0 1 0 1 1 00 1 0 0 0 1 1 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 1 1 0 1 01 1 1 0 1 0 1 11 0 1 0 1 1 0 01 0 1 1 1 1 0 11 0 0 1 1 1 1 01 0 0 0 1 1 1 1表(一)循环码表表(二)多功能发生电路函数表根据卡诺图,可以得到以下结果:G3=QD G2=Q3(+)Q2G1=Q2(+)Q1 G0=Q1(+)Q0逻辑电路图:波形图:CP QAQB QCQD G0G1 G2G3G2与G3相位差从上到下依次为:CP、QA、QB、QC、QD、G0、G1、G2、G3分析:1、CP与Q0同相,Q3的周期是CP的2倍2、CP与Q1同相,Q1的周期是CP的4倍3、CP与Q2同相,Q2的周期是CP的8倍4、CP与Q3同相,Q3的周期是CP的16倍5、CP与G 0同相,G0的周期是CP的4倍6、G1 超前CP 一个CP周期,G1的周期是CP的8倍7、CP与G2同相,G2的周期是CP的16倍8、G3滞后CP 4个CP周期,G3的周期是CP的16倍五、心得体会1、通过分析真值表,利用卡诺图化简,从而得出输入与输出相对应的关系。

实验二组合逻辑电路的设计

一、实验目的

略

二、实验器件数据

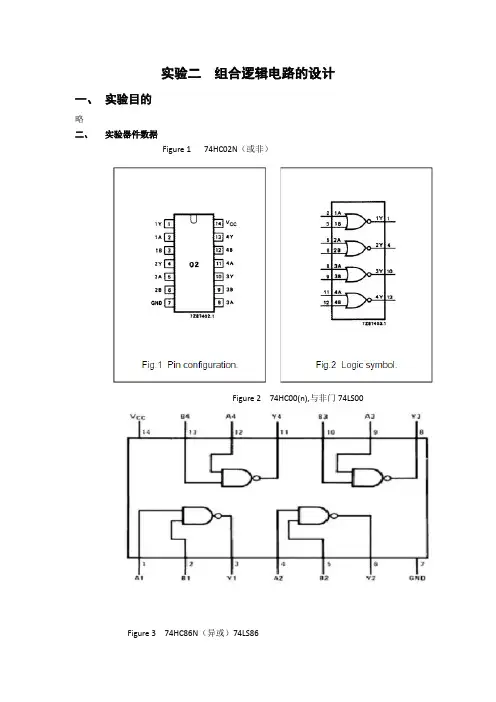

Figure 1 74HC02N(或非)

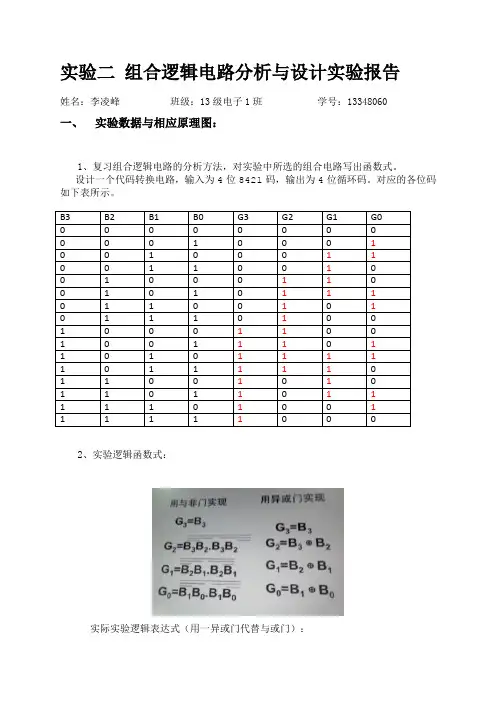

Figure 2 74HC00(n),与非门74LS00

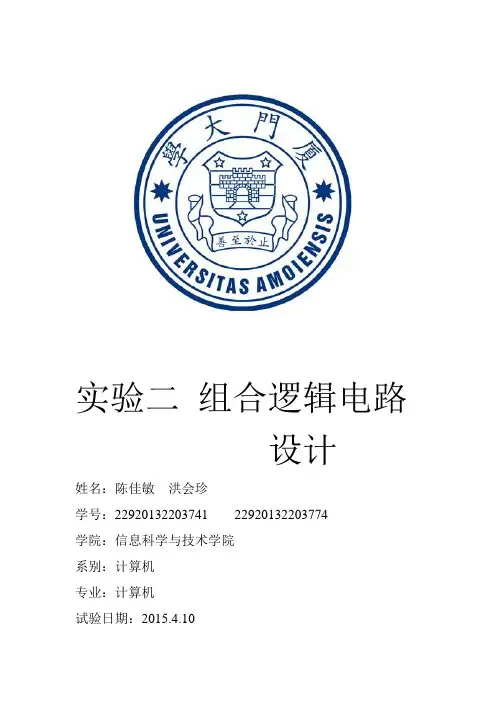

Figure 3 74HC86N(异或)74LS86

三、 实验原理

1. 二进制加法运算电路

二进制加法电路可以由一位全加器组合而成; 全加器逻辑表达式为:111()=('()')'n n n n n

n n n n n n n n n n D A B C C A B C A B A B C A B ---=⊕⊕⎧

⎨

=+⊕⊕⎩g g ()'

一位全加器电路实现如下:

图中,用74LS00D 代替74HC86N

如果要实现多为二进制的加法运算,可将多个全加器级联。

例如将两个全加器级联, 并且在最后输出接一个带解码器的数字显示管,就构成了一个两位二进制数相加的加法器,

如

下图

2.二进制减法运算电路

为了实现减法电路,引入了补码系统,求补码只需让输入取反并使最后一位来自低位进位置高电平,其中,取反可以通过与高电平做异或运算来实现,电路如下:

注意:此时图中电子管输出应该为减法答案的补码。

下面,将补码答案转换为原码。

有如下电路:

注意,通过对图中低电平/高电平的转换(低位的进位信息和补码的取反信息),该减法电路实际上可以变化为加法电路。

可以加入控制信号K,使其为1时电路执行减法,否则执行加法,电路如下:

四、实验内容

1.基本要求:

原码输出结果,并显示正负标志2.提高要求:略。

实验二组合逻辑电路分析与设计实验报告

姓名:李凌峰班级:13级电子1班学号:13348060

一、实验数据与相应原理图:

1、复习组合逻辑电路的分析方法,对实验中所选的组合电路写出函数式。

设计一个代码转换电路,输入为4位8421码,输出为4位循环码。

对应的各位码如下表所示。

2、实验逻辑函数式:

实际实验逻辑表达式(用一异或门代替与或门):

3、实际实验逻辑图:

4、实际实验操作图

二、实验操作记录

1,检测转换电路:

2,实测波形图

10hz方波:

G3 G2 G1 G0波形:

B1 B2 B3 B4波形图:

由以上波形图张图绘制出总的时序图如下:

三、心得与体会

1、这次实验所用器材用了异或门74LS86和异步计数器74LS197.分析组合逻辑电路

时,要先由给定的组合逻辑电路写函数式,然后对函数式进行化简或变换,再根据最简式列真值表,最后确认逻辑功能。

设计组合逻辑电路时,则应先根据给定事件的因果关系列出真值表,然后由真值表写函数式,再对函数式进行化简或变换,最后画出逻辑图,并测试逻辑功能。

2、对示波器的操作仍不够熟悉,在将示波器连接到实验箱的测试端时总是忘了要接地,

致使示波器显示信号不正常。

3、在比较波形时,借用同学的接口同时加载4个波形容易做出总的时序图。

实验二组合逻辑电路设计姓名:陈佳敏洪会珍学号:22920132203741 22920132203774学院:信息科学与技术学院系别:计算机专业:计算机试验日期:2015.4.10一、实验目的掌握组合逻辑电路设计的基本方法,并用与非门实现。

二、实验设备与器件数字逻辑实验箱1台2输入四与非门(7400)2片3输入三与非门(7410)1片三、实验内容1.表决电路设计和实现该电路有四个输入变量A、B、C、D,当输入量中有三个或三个以上为1时,输出F为1,否则F为0。

2.比较电路设计和实现由A1、A0组成一个二进制数A(A1A0),由B1、B0组成另一个二进制数B(B1B0),电路有三个输出端P1、P2、P3:当A>B时,P1=1,P2=P3=0;当A=B时,P2=1,P1=P3=0;当A<B时,P3=1,P1=P2=0。

四、实验步骤和要求1.根据题意,列出真值表;实验1的真值表:A B C D F0 0 0 0 00 0 0 1 00 0 1 0 00 0 1 1 00 1 0 0 00 1 0 1 00 1 1 0 00 1 1 1 11 0 0 0 01 0 0 1 01 0 1 0 01 0 1 1 11 1 0 0 01 1 0 1 11 1 1 0 111 1 1 1 实验2的真值表:A1A0 B1 B0 P1 P2 P3 00 0 0 0 1 0 00 0 1 0 0 1 00 1 0 0 0 1 00 1 1 0 0 1 01 0 0 1 0 0 01 0 1 0 1 0 01 1 0 0 0 1 01 1 1 0 0 1 10 0 0 1 0 0 10 0 1 1 0 0 10 1 0 0 1 0 10 1 1 0 0 1 11 0 0 1 0 0 11 0 1 1 0 0 11 1 0 1 0 0 1 1 1 1 0 1 02.用卡诺图化简,得到最简的与-或表达式。

实验1的卡诺图:B1B0 A1A000 01 11 1000011 111 1 1 10 1最简与-或表达式即为:F=ABC+ABD+BCD+ACD实验2的卡诺图:P1:B1B0 A1A000 01 11 10001 1 1 011 1 1110 1最简与-或表达式即为:p1=A11B +10B A 0B +A1A00BP2:B1B0A1A0 00 01 11 10001 011 111 10 1最简与-或表达式即为:p2=1A 0A 1B 0B +1A A01B B0+A1A0B1B0+A10A B10BP3:B1B0A1A0 00 01 11 1000011 111 1 1 101 1最简与-或表达式即为:p3=1A B1+1A 0A B0+0A B1B03.将表决电路用摩根定理进行逻辑变换为用二输入与非门(7400)实现的形式。

实验二:组合逻辑电路分析与设计姓名: 夕何【实验目的】1.掌握组合逻辑电路的分析方法,并验证其逻辑功能。

2.掌握组合逻辑电路的设计方法,并能用最少的逻辑门实现之。

3.熟悉示波器的使用。

【实验仪器及器件】【实验过程及结果分析】1.代码转换电路的设计已知4位输入8421码为表1,4位输出循环码如表2表1 BCD码表2 GRAY码D C B A0 0 0 00 0 0 1将表1中ABCD 作为自变量,表2中3G ~0G 各自作为因变量可得到四张真值表,即可得出3G ~0G 各自与ABCD 的逻辑函数式如下D G =3 (1)D C G ⊕=2 (2) C B G ⊕=1 (3)0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 11 0 0 11 0 1 01 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1113G2G1G0G0 0 0 0 0 0 1 0 0 1 1 0 0 1 0 0 1 1 0 0 1 1 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 0 10 1 0 10 1 1 1 0 0 1 1B A G ⊕=0 (4)根据老师要求,将G 2和G 1的逻辑表达式变换为: G 2=((C’D)’(CD’)’)’ (5) G 1=((C’B)’(CB’)’)’ (6)由函数式(1)(5)(6)(4)可得如图(1)所示电路图:图(1)AltiumDesigner 本实验电路图2.实际电路图如图(2)所示图(2)实际电路图测试:将ABCD 分接逻辑开关的各输入端口,3G ~0G 接入“0-1”显示器检测,结果如表 3,实验结果:以10KHz 方波作为计数器的脉冲,一GO 位基准,得到各个端口的输出波形: (1)G0 与G1的波形如图(3)所示,其中上边的波形为G0,下边的波形为G1;(2)G2与G0的波形图如图(4)所示,其中上边为G2,下边为G0图(4)(3)G2与G3波形图对比如图(5)所示,其中上边的波形为G2,下边波形为G3。

实验二组合逻辑电路一、实验目的1.掌握数据选择器的功能和应用方法;2.掌握显示译码器的功能和使用方法;3.掌握组合数字电路的设计和实现方法。

二、预习要求1.复习译码器和数据选择器的工作原理;2.复习有关组合电路设计方法的知识;3.阅读74LS138和74LS151的引脚排列图及功能表;4. 设计实验内容所要求的数据记录表格。

三、理论准备1.概述组合逻辑电路又称组合电路,组合电路的输出只决定于当时的外部输入情况,与电路过去状态无关。

因此,组合电路的特点是无“记忆性”。

在组成上组合电路的特点是由各种门电路连接而成,而且连接中没有反馈线存在。

所以各种功能的门电路就是简单组合逻辑电路。

组合逻辑电路的输入信号和输出信号往往不止一个,其功能描述方法通常有函数表达式、真值表、卡诺图和逻辑图等几种。

组合逻辑电路的分析与设计方法,是立足于小规模集成电路分析和设计基本方法之一。

2.组合逻辑电路的分析方法分析的任务是:对给定的电路求解其逻辑功能,即求出该电路的输出与输入之间的逻辑关系,通常是用逻辑式或真值表来描述,有时也加上必须的文字说明。

分析的步骤:(1)逐级写出逻辑表达式,最后得到输出逻辑变量与输入逻辑变量之间的逻辑函数式。

(2)化简。

(3)列出真值表。

(4)文字说明上述四个步骤不是一成不变的。

除第一步外,其它三步根据实际情况的要求而采用。

3.组合逻辑电路的设计方法设计的任务是:使用中、小规模集成电路来设计组合电路是最常见的逻辑电路,由给定的功能要求,设计出相应的逻辑电路。

设计的一般步骤如图3-1所示:根据设计任务的要求建立输入、输出变量,并列出真值表。

然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。

并按实际选用逻辑门的类型修改逻辑表达式。

根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。

最后,用实验来验证设计的正确性。

需要注意的是,在使用中规模集成的组合逻辑电路设计时,需要把函数式变换成适当的形式(而不一定是最简式)。

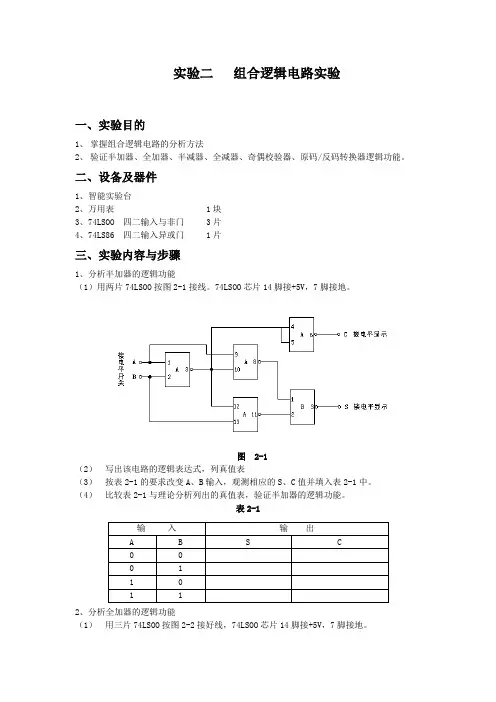

实验二组合逻辑电路实验一、实验目的1、掌握组合逻辑电路的分析方法2、验证半加器、全加器、半减器、全减器、奇偶校验器、原码/反码转换器逻辑功能。

二、设备及器件1、智能实验台2、万用表 1块3、74LSOO 四二输入与非门 3片4、74LS86 四二输入异或门 1片三、实验内容与步骤1、分析半加器的逻辑功能(1)用两片74LSOO按图2-1接线。

74LSOO芯片14脚接+5V,7脚接地。

图 2-1(2)写出该电路的逻辑表达式,列真值表(3)按表2-1的要求改变A、B输入,观测相应的S、C值并填入表2-1中。

(4)比较表2-1与理论分析列出的真值表,验证半加器的逻辑功能。

表2-12、分析全加器的逻辑功能(1)用三片74LSOO按图2-2接好线,74LSOO芯片14脚接+5V,7脚接地。

图2-2(2)分析该线路,写出Sn、Cn的逻辑表达式,列出其真值表。

(3)利用开关改变An、Bn、Cn-1的输入状态,借助指示灯或万用表观测Sn、Cn的值填入表2-2中。

(4)将表2-2的值与理论分析列出的真值表加以比较,验证全加器的逻辑功能。

3、分析半减器的逻辑功能(1)用两片74LSOO按图2-3接好线,74LSOO芯片14脚接+5V,7脚接地。

图 2-3(2)分析该线路,写出D、C的逻辑表达式,列出真值表。

(3)按表2-3改变开关A、B状态,观测D、C的值并填入表2-3中。

(4)将表2-3与理论分析列出的真值表进行比较,验证半减器的逻辑功能。

表 2.34、分析全减器的逻辑功能(1)用一片74LS86和两片74LSOO按图2-4接线。

各片的14脚接+5V,7脚接地。

图 2-4(2)分析该线路,写出Dn、Cn的逻辑表达式,列出真值表。

(3)按表2-4改变An、Bn、Cn-1的开关状态,借助万用表或指示灯观测输出Dn、Cn的状态并填入表2-4中。

(4)对比表2-4和理论分析列出的真值表,验证全减器的逻辑功能。

表 2-45、分析四位奇偶校验器的逻辑功能(1)用74LS86按图2-5接好线。

实验二 组合逻辑电路功能分析与设计一、 实验目的:1、了解组合逻辑电路的特点;2、掌握组合逻辑电路功能的分析方法;3、学会组合逻辑电路的连接方法;4、掌握组合逻辑电路的设计方法。

二、实验原理:1、组合逻辑电路的特点:组合逻辑电路可以有一个或多个输入端,也可以有多个输出端;在组合逻辑电路中,数字信号是单向传递的,只有从输入到输出的传递; 输出信号只与输入的即时状态有关2、组合逻辑电路的分析方法:真值表法;卡洛图法;逻辑表达式法;逻辑电路图法;3、组合逻辑电路的设计步骤:实际的逻辑问题→定义输出和输入变量→真值表→选定器件类型→化简→最简表达式→逻辑图 三、实验器件集成块:74LS00、74LS04、74LS08、74LS32 四、实验内容: (一)、组合逻辑电路功能分析分析图4-1所示电路的逻辑功能: 由电路图所得的逻辑表达式:Y=AB+A B =A ☉B逻辑功能:用与门和与非门实现同或(二)、组合逻辑电路设计(根据组合逻辑电路的设计步骤,分别写出各个组合逻辑电路的设计步骤。

)1、设计一个举重裁判表决器。

设举重比赛有三个裁判,一个主裁判和两个副裁判。

杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。

只有当两个或两个以上裁判(其中必须有主裁判)判明成功时,表示“成功”的灯才亮。

(要求用与非门实现)设A 为主裁判的判定;B ,C 分别为两位副裁判的判别(0为裁判不确定,1为裁判确定);Y=0表示不成功,Y=1表示成功。

1图4-1由真值表得到的逻辑表达式为:Y=AB+AC=ACAB∙电路图为:2、某设备有开关A、B、C,要求仅在开关A接通的条件下,开关B才能接通;开关C 仅在开关B接通的条件下才能接通。

违反这一规程,则发出报警信号。

设计一个由与非门组成的能实现这一功能的报警控制电路。

(要求用与非门实现)设A,B,C分别为三个开关(0表示开关断开,1表示开关闭合);Y=0表示不违反规程,Y=1表示违反规程,将发生报警信号。

本科学生实验报告

云南师范大学教务处编印

实验序号实验名称组合逻辑电路分析实验时间实验室

1.实验元件(元件型号;引脚结构;逻辑功能;引脚名称)

1.SAC-DS4数字逻辑实验箱1个

2.万用表 1块

3.74LS00N 四二输入与非门 3片

74LS00引脚结构及逻辑功能

2.实验目的

1.掌握组合逻辑电路的分析方法

2. 验证半加器、全加器逻辑功能。

3.实验电路原理图及接线方法描述:

(1)两片74LS00N实现半加器的逻辑功能电路图

(2)三片74LS00N实现全加器的逻辑功能电路图

4.实验中各种信号的选取及控制(电源为哪些电路供电;输入信号的分布位置;输出信号的指示类型;总结完成实验条件)

(1)用两片74LS00(引脚见附录)按图4-1接线。

74LS00芯片14脚接+5V,7脚接地。

(2)用三片74LS00按图4-2接好线。

74LS00芯片14脚接 +5v,7脚接地.。

实验二组合逻辑电路分析与设计一、实验目的1.掌握组合逻辑电路的分析方法与测试方法;2.掌握组合逻辑电路的设计方法。

二、实验预习要求1.熟悉门电路工作原理及相应的逻辑表达式;2.熟悉数字集成电路的引脚位置及引脚用途;3.预习组合逻辑电路的分析与设计步骤。

三、实验原理通常, 逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。

电路在任何时刻, 输出状态只决定于同一时刻各输入状态的组合, 而与先前的状态无关的逻辑电路称为组合逻辑电路。

1.组合逻辑电路的分析过程, 一般分为如下三步进行:(1)由逻辑图写出输出端的逻辑表达式;(2)画出真值表;(3)根据对真值表进行分析, 确定电路功能。

2. 组合逻辑电路的一般设计过程为图实验2.1所示。

设计过程中, “最简”是指电路所用器件最少, 器件的种类最少, 而且器件之间的连线也最少.四、实验仪器设备1. TPE-ADⅡ实验箱(+5V电源, 单脉冲源, 连续脉冲源, 逻辑电平开关, LED显示, 面包板数码管等)1台;2. 四两输入集成与非门74LS00 2片;3. 四两输入集成异或门74LS86 1片;4. 两四输入集成与非门74LS20 3片。

五、实验内容及方法1. 分析、测试74LS00组成的半加器的逻辑功能。

(1)用74LS00组成半加器, 如图实验2.2所示电路, 写出逻辑表达式并化简, 验证逻辑关系。

Z1=AB;Z2= Z1A = ABA;Z3= Z1B = ABB;Si= Z2Z3 = ABA ABB = ABA+ABB = AB+ AB = A + B;Ci = Z1A = AB;(2)列出真值表。

(3)分析、测试用异或门74LS86与74LS00组成的半加器的逻辑功能, 自己画出电路, 将测试结果填入自拟表格中, 并验证逻辑关系。

评价: 通过这种方法获得测试结果和上述电路完全相同, 并且在有异或门的情况下实现较为简单, 所以我们应当在设计的时候在条件允许的情况实现最简。

实验二组合逻辑电路(半加器全加器及逻辑运算)一、实验目的1. 掌握组合逻辑电路的功能测试。

2. 验证半加器和全加器的逻辑功能。

3. 学会二进制数的运算规律。

二、实验仪器及材料(1)TPE-D3数字电路实验箱。

(2)器件:74LS00 二输入端四与非门3片74LS86 二输入端四异或门1片74LS54 四组输入与或非门1片三、预习要求1.预习组合逻辑电路的分析方法。

2.预习用与非门和异或门构成的半加器、全加器的工作原理。

3.预习二进制数的运算。

+四、实验内容1.组合逻辑电路功能测试。

图2.1 Y1= ; Y2=(1) 用2片74lS00组成图2.1所示逻辑电路。

为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

(2) 图中A、B、C接电平开关,Y1,Y2接发光管电平显示。

(3) 按表2.1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式。

(4) 将运算结果与实验比较。

表2.1输入输出A B C Y1 Y20 0 0 1 1 1 1 0 0111111112.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知.半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图2.2。

(1).在学习机上用异或门和与门接成以上电路。

A、B 图2.2接电平开关S,Y、Z接电平显示。

(2).按表2.2要求改变A、B状态,填表。

表2.2输入端 A 0 1 0 1B 0 0 1 1输出端YZ3.测试全加器的逻辑功能。

(1).写出图2.3电路的逻辑表达式。

(2).根据逻辑表达式列真值表。

(3).根据真值表画逻辑函数S i C i的卡诺图。

(4).添写表2.3各点状态。

图2.3表2.3A iB iC i-1Y Z X1X2X3S i Ci0 0 00 1 01 0 01 1 00 0 10 1 11 0 11 1 1(5) .按原理图选择与非门并接线进行测试,将测试结果记入表2.4,并与上表进行比较看逻辑功能是否一致。

实验二组合逻辑电路

一、实验目的

1.掌握组合逻辑电路的功能测试。

2.验证半加器和全加器的逻辑功能。

3.学会二进制数的运算规律。

二、实验仪器及材料

器件

74LS00 二输入端四与非门3片

74LS86 二输入端四异或们1片

74LS54 四组输入与或非门1片

三、预习要求

1.预习组合逻辑电路的分析方法。

2.预习用与非门和异或门构成的半加器、全加器的工作原理。

3.预习二进制数的运算。

四、实验内容

1.组合逻辑电路功能测试。

(1)用2片74LS00组成图2.1所示逻辑电路。

为便于接线和检查,

在图中要注明芯片编号以及各引脚对应的编号。

(2)图中A、B、C接电平开关,Y1、Y2接发光管电平显示。

(3)按表2.1要求,改变A、B、C的状态填表并写出Y1、Y2逻辑

表达式。

Y1=A+B,Y2=A’B’C+BC+AB

输入输出

A B C Y1 Y2

0 0 0 0 0

0 0 1 0 1

0 1 1 1 1

1 1 1 1 1

1 1 0 1 0

1 0 0 1 0

1 0 1 1 1

0 1 0 1 1

(4)将运算结果与试验比较。

2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和两个与非门组成如图2.2。

(1)在学习机上用异或门和与门接成以上电路。

A、B接电平开关S、Y、Z接电平显示。

(2)按表2.2要求改变A、B状态,填表。

输入端 A 0 1 0 1

B 0 0 1 1

输出端Y 0 0 0 1

Z 0 0 0 0。