北京理工大学计算机组成原理期末复习

- 格式:pdf

- 大小:354.95 KB

- 文档页数:25

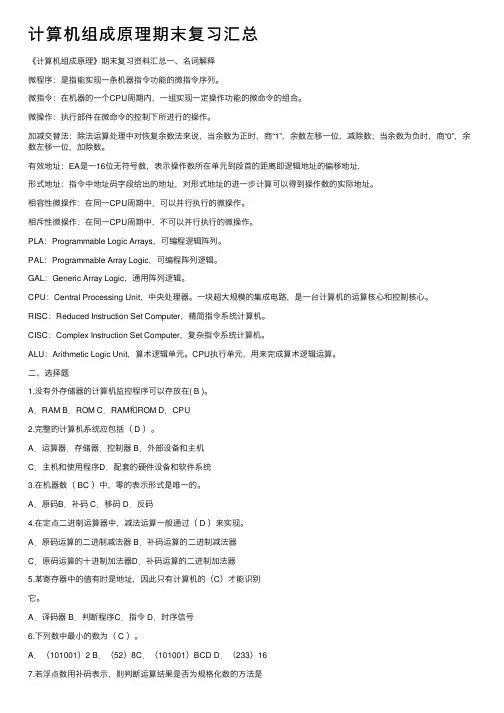

计算机组成原理期末复习汇总《计算机组成原理》期末复习资料汇总⼀、名词解释微程序:是指能实现⼀条机器指令功能的微指令序列。

微指令:在机器的⼀个CPU周期内,⼀组实现⼀定操作功能的微命令的组合。

微操作:执⾏部件在微命令的控制下所进⾏的操作。

加减交替法:除法运算处理中对恢复余数法来说,当余数为正时,商“1”,余数左移⼀位,减除数;当余数为负时,商“0”,余数左移⼀位,加除数。

有效地址:EA是⼀16位⽆符号数,表⽰操作数所在单元到段⾸的距离即逻辑地址的偏移地址.形式地址:指令中地址码字段给出的地址,对形式地址的进⼀步计算可以得到操作数的实际地址。

相容性微操作:在同⼀CPU周期中,可以并⾏执⾏的微操作。

相斥性微操作:在同⼀CPU周期中,不可以并⾏执⾏的微操作。

PLA:Programmable Logic Arrays,可编程逻辑阵列。

PAL:Programmable Array Logic,可编程阵列逻辑。

GAL:Generic Array Logic,通⽤阵列逻辑。

CPU:Central Processing Unit,中央处理器。

⼀块超⼤规模的集成电路,是⼀台计算机的运算核⼼和控制核⼼。

RISC:Reduced Instruction Set Computer,精简指令系统计算机。

CISC:Complex Instruction Set Computer,复杂指令系统计算机。

ALU:Arithmetic Logic Unit,算术逻辑单元。

CPU执⾏单元,⽤来完成算术逻辑运算。

⼆、选择题1.没有外存储器的计算机监控程序可以存放在( B )。

A.RAM B.ROM C.RAM和ROM D.CPU2.完整的计算机系统应包括( D )。

A.运算器.存储器.控制器 B.外部设备和主机C.主机和使⽤程序D.配套的硬件设备和软件系统3.在机器数( BC )中,零的表⽰形式是唯⼀的。

A.原码B.补码 C.移码 D.反码4.在定点⼆进制运算器中,减法运算⼀般通过( D )来实现。

计算机组成原理期末考试及答案A卷基础知识(50分)1、名词解释(10分)机器字长SRAMEPROM指令系统微指令2、选择题(10分)1)设字长32位,使⽤IEEE格式,则阶码采⽤______表⽰。

A.补码B. 原码C. 移码D. 反码2) 四⽚74181ALU和⼀⽚74182CLA器件相配合,具有如下进位传递功能______。

A.形波进位B. 组内先⾏进位,组间先⾏进位C.组内先⾏进位,组间⾏波进位D. 组内形波进位,组间先⾏进位3) 某SARM芯⽚,其存储容量为64K×16位,该芯⽚的地址线数⽬和数据线数⽬分别是___。

A. 16, 16 B .16, 64, C. 64, 8 D. 64, 164)单地址指令中为了完成两个数的算术运算,除地址码指明的⼀个操作数外,另⼀个数常需采⽤______。

A. 堆栈寻址⽅式B. ⽴即寻址⽅式C. 隐含寻址⽅式D. 间接寻址⽅式微5)程序控制器中,机器指令与微指令的关系是______。

A.每⼀条机器指令由⼀条微指令来执⾏B.⼀段机器指令组成的程序可由⼀条微指令执⾏C.⼀条微指令由若⼲条机器指令组成D. 每⼀条机器指令由⼀段⽤微指令编成的微程序来解释执⾏3、填空题(10分)1)存储___①___并按__②____顺序执⾏,这是冯?诺依曼型计算机的⼯作原理。

2)相联存储器是按③访问的存储器。

3) 主存与cache的地址映射有__④___、⑤、⑥三种⽅式。

4)通常指令编码的第⼀个字段是⑦。

5) 异步通信⽅式可分为⑧、⑨、⑩三种类型。

4、问答题(20分)1)在计算机中,为什么要采⽤多级结构的存储器系统2)简述CPU的功能.3)试⽐较⽔平型微指令与垂直型微指令。

4)简述总线集中控制的优先权仲裁⽅式。

⼆、综合应⽤(50分)1、已知X=-0.1101,Y=0.1011,试⽤补码⼀位乘法计算X×Y (15分)2、指令格式如下所⽰。

OP为操作码字段,试分析指令格式特点。

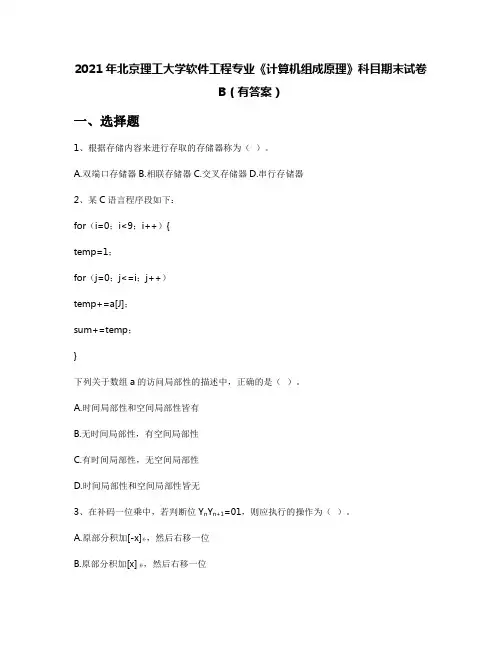

2021年北京理工大学软件工程专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、根据存储内容来进行存取的存储器称为()。

A.双端口存储器B.相联存储器C.交叉存储器D.串行存储器2、某C语言程序段如下:for(i=0;i<9;i++){temp=1;for(j=0;j<=i;j++)temp+=a[J];sum+=temp;}下列关于数组a的访问局部性的描述中,正确的是()。

A.时间局部性和空间局部性皆有B.无时间局部性,有空间局部性C.有时间局部性,无空间局部性D.时间局部性和空间局部性皆无3、在补码一位乘中,若判断位Y n Y n+1=01,则应执行的操作为()。

A.原部分积加[-x]补,然后右移一位B.原部分积加[x]补,然后右移一位C.原部分积加[-x] 补,然后左移一位D.原部分积加[x]补,然后左移一位4、下列关于进制的说法中正确的是()。

I.任何二进制整数都可用十进制表示Ⅱ.任何二进制小数都可用十进制表示Ⅲ.任何十进制整数都可用二进制表示IⅣ.任何十进制小数都可用二进制表示A.I、ⅢB. I、Ⅱ、ⅢC.I、Ⅱ、Ⅲ、ⅣD.Ⅱ、IV5、在C语言程序中,以下程序段最终的f值为()。

Float f=2.5+1e10;f=f-1e10;A.2.5B.250C.0D.3.56、内部总线(又称片内总线)是指()。

A.CPU内部连接各寄存器及运算部件之间的总线B.CPU和计算机系统的其他高速功能部件之间互相连接的总线C.多个计算机系统之间互相连接的总线D.计算机系统和其他系统之间互相连接的总线7、在下列各种情况中,最应采用异步传输方式的是().A.I/O接口与打印机交换信息B.CPU与主存交换信息C.CPU和PCI总线交换信息D.由统一时序信号控制方式下的设备8、计算机()负责指令译码。

A.算术逻辑单元B.控制单元(或者操作码译码器)C.存储器电路D.输入/输出译码电路9、下列关于配备32位微处理器的计算机的说法中,正确的是()。

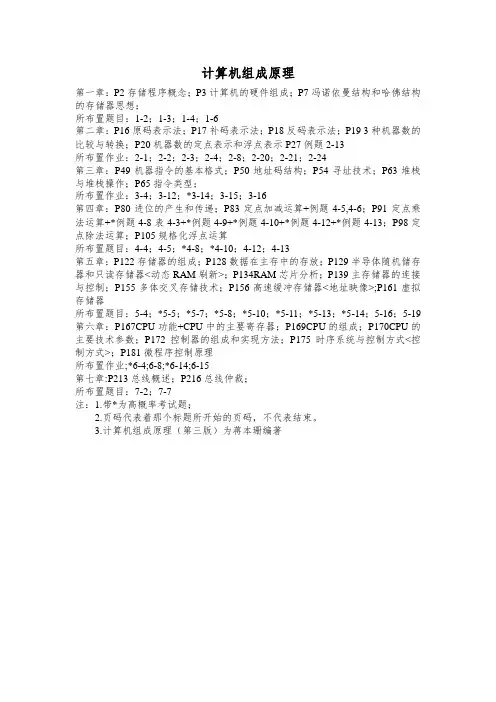

计算机组成原理第一章:P2存储程序概念;P3计算机的硬件组成;P7冯诺依曼结构和哈佛结构的存储器思想;所布置题目:1-2;1-3;1-4;1-6第二章:P16原码表示法;P17补码表示法;P18反码表示法;P19 3种机器数的比较与转换;P20机器数的定点表示和浮点表示P27例题2-13所布置作业:2-1;2-2;2-3;2-4;2-8;2-20;2-21;2-24第三章:P49机器指令的基本格式;P50地址码结构;P54寻址技术;P63堆栈与堆栈操作;P65指令类型;所布置作业:3-4;3-12;*3-14;3-15;3-16第四章:P80进位的产生和传递;P83定点加减运算+例题4-5,4-6;P91定点乘法运算+*例题4-8表4-3+*例题4-9+*例题4-10+*例题4-12+*例题4-13;P98定点除法运算;P105规格化浮点运算所布置题目:4-4;4-5;*4-8;*4-10;4-12;4-13第五章:P122存储器的组成;P128数据在主存中的存放;P129半导体随机储存器和只读存储器<动态RAM刷新>;P134RAM芯片分析;P139主存储器的连接与控制;P155多体交叉存储技术;P156高速缓冲存储器<地址映像>;P161虚拟存储器所布置题目:5-4;*5-5;*5-7;*5-8;*5-10;*5-11;*5-13;*5-14;5-16;5-19 第六章:P167CPU功能+CPU中的主要寄存器;P169CPU的组成;P170CPU的主要技术参数;P172控制器的组成和实现方法;P175时序系统与控制方式<控制方式>;P181微程序控制原理所布置作业;*6-4;6-8;*6-14;6-15第七章:P213总线概述;P216总线仲裁;所布置题目:7-2;7-7注:1.带*为高概率考试题;2.页码代表着那个标题所开始的页码,不代表结束。

3.计算机组成原理(第三版)为蒋本珊编著。

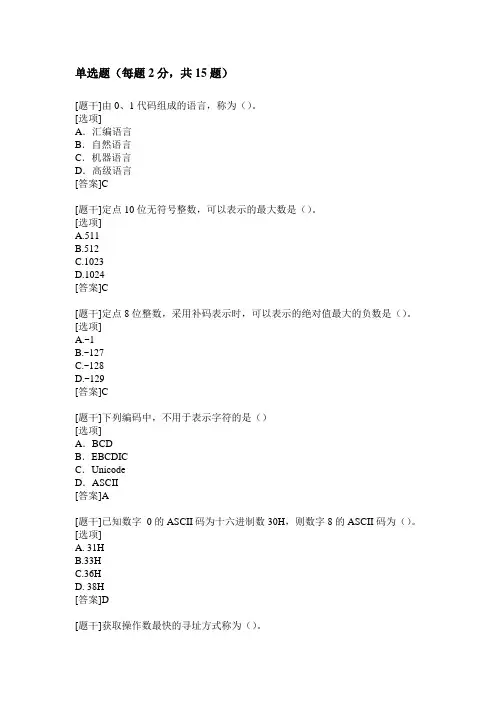

单选题(每题2分,共15题)[题干]由0、1代码组成的语言,称为()。

[选项]A.汇编语言B.自然语言C.机器语言D.高级语言[答案]C[题干]定点10位无符号整数,可以表示的最大数是()。

[选项]A.511B.512C.1023D.1024[答案]C[题干]定点8位整数,采用补码表示时,可以表示的绝对值最大的负数是()。

[选项]A.-1B.-127C.-128D.-129[答案]C[题干]下列编码中,不用于表示字符的是()[选项]A.BCDB.EBCDICC.UnicodeD.ASCII[答案]A[题干]已知数字0的ASCII码为十六进制数30H,则数字8的ASCII码为()。

[选项]A. 31HB.33HC.36HD. 38H[答案]D[题干]获取操作数最快的寻址方式称为()。

[选项]A.直接寻址B.立即寻址C.间接寻址D.寄存器间接寻址[答案]B[题干]在变址寄存器寻址方式中,若变址寄存器的内容是4E3CH,指令中的形式地址是63H,则它对应的有效地址是()。

[选项]A.63HB.4D9FHC.4E3CHD.4E9FH[答案]D[题干]堆栈存储器存取数据的方式是()。

[选项]A.先进先出B.随机存取C.顺序存取D.先进后出[答案]D[题干]在补码表示的机器中,若寄存器A中原存的数为9EH,现存的数为4FH,则表明执行的一条指令是()。

[选项]A.算术左移B.逻辑左移C.算术右移D.逻辑右移[答案]D[题干]在双符号位判断溢出的方案中,出现溢出时,双符号位应当为()。

[选项]A. 00或01B. 01或10C.00或10D. 10或11[答案]B[题干]某字长为8位的计算机中,已知整型变量x、y的机器数分别为[x]补=11110100,[y]补=10110000。

若整型变量z=2 x+y/2,则z的机器数为()。

[选项]A.11000000B.00100100C.10101010D.溢出[答案]A[题干]在补码除法中需要用到3个寄存器,其中A寄存器用来存放()。

《计算机组成原理》期末考试复习要点《计算机组成原理》期末考试复习要点一、试题类型:填空题、选择题、简答题二、重点章节第二、三、四、五章三、复习要点与模拟题㈠数据表示、运算1.进制转换;原码、反码和补码的表示⑴.将十进制数+107/128和-52 化成二进制数,再写出各自的原码、补码、反码表示(符号位和数值位共8位)⑵.将十进制数一0.276和47化成二进制数,再写出各自的原码、补码、反码表示(符号位和数值位共8位)。

⑶.(21)10=( )2=( )8=( )16⑷.x=一0.100l [x]原=( ) [x]补=( ) [-x]=( )⑸.y=0.010l [Y]原=( ) [Y]=( ) [—Y]补=( ) [Y—X]补=( )考核知识点:1)进制的转换2)定点整数、小数的三种码表示3)技巧:●将107转换成二进制后小数点移位(128=27)先写成8位,再转换成原码、反码、补码,如:-52先写成–0110100,再转换成原码10110100、反码11001011、补码11001100 2.有权码与无权码的判断与推导⑴.(27)10=()BCD⑵复习指导书P11第2小题考核知识点1)BCD码是最基本的有权码,也称8421码或二-十进制码。

BCD码实际上是十进制编码,只不过每一个编码用4位二进制数来表示,如35=(00110101)BCD 注意与35的二进制表示是100011两者有区别。

2)其它有权码(一般4位)见书P72表2.9,判断推导过程见复习指导书P133.补码加减运算及溢出判断用补码运算方法计算x十Y=?并判断结果是否溢出(采用双符号位)。

(1) x=0.10ll Y=0.1100(2)x=一0.1011 Y=0.1001解:(1) [x]补=00.1011, [Y]补=00.110000.1011十 00.110001.0111因结果双符号相异,有溢出(2) x=一0.1011 Y=0.1001·.· [x]补=11.010l [Y]补=00.100ll1.010l十 00.100l11.1110因结果双符号相同,不溢出考核知识点1)补码(双符号位)的表示2)溢出的概念与判断4.浮点数加减运算设A=-0.101101*2-3 , B=0.101001*2-2,首先将A、B表示为规范化的浮点数,要求阶码用4位(包括阶三符号位)用移码表示,尾数用8位(含浮点数的符号位)原码表示;再写出A+B的计算步骤和每一步的运算结果。

一、简答题1、试述浮点数规格化的目的和方法。

答:浮点的规格化是为了使浮点数尾数的最高数值位为有效数位。

当尾数用补码表示时,若符号位与小数点后的第一位不相等,则被定义为已规格化的数,否则便是非规格化数。

通过规格化,可以保证运算数据的精度。

方法:进行向左规格化,尾数左移一位,阶码减1,直到规格化完毕。

2、简述循环冗余码(CRC)的纠错原理。

答:CRC码是一种纠错能力较强的校验码。

在进行校验时,先将被检数据码的多项式用生成多项式G(X)来除,若余数为0,说明数据正确;若余数不为0,则说明被检数据有错。

只要正确选择多项式G(X),余数与CRC码出错位位置的对应关系是一定的,由此可以用余数作为判断出错位置的依据而纠正出错的数据位。

3、DRAM存储器为什么要刷新?有几种刷新方式?DRAM存储元是通过栅极电容存储电荷来暂存信息。

由于存储的信息电荷终究是有泄漏的,电荷数又不能像SRAM存储元那样由电源经负载管来补充,时间一长,信息就会丢失。

为此必须设法由外界按一定规律给栅极充电,按需要补给栅极电容的信息电荷,此过程叫“刷新”。

①集中式---正常读/写操作与刷新操作分开进行,刷新集中完成。

②分散式---将一个存储系统周期分成两个时间片,分时进行正常读/写操作和刷新操作。

③异步式---前两种方式的结合,每隔一段时间刷新一次,保证在刷新周期内对整个存储器刷新一遍。

4、CPU中有哪些主要寄存器?简述这些寄存器的功能。

(1)指令寄存器(IR):用来保存当前正在执行的一条指令。

(2)程序计数器(PC):用来确定下一条指令的地址。

(3)地址寄存器(AR):用来保存当前CPU所访问的内存单元的地址。

(4)缓冲寄存器(DR):<1>作为CPU和内存、外部设备之间信息传送的中转站。

<2>补偿CPU和内存、外围设备之间在操作速度上的差别。

<3>在单累加器结构的运算器中,缓冲寄存器还可兼作为操作数寄存器。

2022年北京理工大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、连续两次启动同一存储器所需的最小时间间隔称为()。

A.存储周期B.存取时间C.存储时间D.访问周期2、若单译码方式的地址输入线为6,则译码输出线有()根,那么双译码方式有输出线()根。

A.64,16B.64,32C.32,16D.16,643、在计算机系统中,表明系统运行状态的部件是()。

A.程序计数器B.指令寄存器C.程序状态字D.累加寄存器4、()可区分存储单元中在放的是指令还是数据。

A.存储器B.运算C.用户D.控制器5、指令寄存器的位数取决()。

A.存储器的容量B.指令字长C.机器字长人D.存储字长6、假设某存储器总线采用同步通信方式,时钟频率为50MHz,每个总线事务以突发方式传输8个字,以支持块长为8个字的Cache行读和Cache行写,每字4B.对于读操作,方式顺序是1个时钟周期接收地址,3个时钟周期等待存储器读数,8个时钟周期用于传输8个字。

请问若全部访问都为读操作,该存储器的数据传输速率为()。

A.114.3MB/sB.126.0MB/sC.133.3MB/sD.144.3MB/s7、系统总线中的数据线、地址线、控制线是根据()来划分的。

A.总线所处的位置B.总线的传输方向C.总线传输的内容D.总线的材料8、微指令操作控制字段的每一位代表一个控制信号,这种微程序的控制方式叫作()A.字段直接编码B.字段间接编码C.混合编码D.直接编码9、指令寄存器中寄存的是()A.下一条要执行的指令B.已执行完了的指令C.正在执行的指令D.要转移的指令10、在统一编址的方式下,存储单元和I/O设备是靠()米区分的。

A.不同的地址码B.不同的地址线C.不同的指令D.不同的数据线11、若某设备中断请求的响应和处理时间为100ns,每400ns发出一次中断请求,中断响应所允许的最长延迟时间为50ns,则在该设备持续工作过程中、CPU用于该设备的I/O时间占整个CPU时间的百分比至少是()。

计算机组成原理课程复习要点1、总线、时钟周期、机器周期、机器字长、存储字长、存储容量、立即寻址、直接寻址、MDR、MAR等基本概念。

总线:连接多个部件的信息传输线,是各个部件共享的传输介质。

在某一时刻,只允许有一个部件向总线发送信息,而多个部件可以同时从总线上接收相同的消息。

分为片内总线,系统总线和通信总线。

时钟周期:也称为振荡周期,定义为时钟频率的倒数。

时钟周期是计算机中最基本的、最小的时间单位。

在一个时钟周期内,CPU仅完成一个最基本的动作。

机器周期:完成一个基本操作所需要的时间称为机器周期。

一般情况下,一个机器周期由若干个S周期(状态周期)组成存储容量:存储容量是指存储器可以容纳的二进制信息量,用存储器中存储地址寄存器MAR的编址数与存储字位数的乘积表示。

即:存储容量 = 存储单元个数*存储字长立即寻址:立即寻址的特点是操作数本身设在指令字内,即形式地址A不是操作数的地址,而是操作数本身,又称之为立即数。

数据是采用补码的形式存放的把“#”号放在立即数前面,以表示该寻址方式为立即寻址。

直接寻址:在指令格式的地址字段中直接指出操作数在内存的地址ID。

在指令执行阶段对主存只访问一次。

计算机系统:由计算机硬件系统和软件系统组成的综合体。

计算机硬件:指计算机中的电子线路和物理装置。

计算机软件:计算机运行所需的程序及相关资料。

主机:是计算机硬件的主体部分,由CPU和主存储器MM合成为主机。

CPU:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了CACHE)。

主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器,可随机存取;由存储体、各种逻辑部件及控制电路组成。

存储单元:可存放一个机器字并具有特定存储地址的存储单位。

存储元件:存储一位二进制信息的物理元件,是存储器中最小的存储单位,又叫存储基元或存储元,不能单独存取。

一、填空题1. 用二进制代码表示的计算机语言称为( 机器语言),用助记符编写的语言称为( 汇编语言)。

2. 计算机硬件由( 控制单元)、( 运算器)、( 存储器)、输入系统和输出系统五大部件组成。

3. 十六进制数 CB8 转换成二进制数为( 110010111000 )。

4. 某数 x 的真值-0.1011B,其原码表示为( 1.1011 )。

5. 在浮点加减法运算过程中,在需要( 对阶)或( 右规)时,尾数需向右移位。

6. 指令通常由( 操作码)和( 地址码)两部分组成。

7. 要组成容量为 4K*8 位的存储器,需要( 8 ) 片 4K×1 位的芯片并联,或者需要( 4 ) 片 1K×8 位的芯片串联。

8. 中断处理过程包括( 关中断)、( 保护现场)、( 执行中断服务程序)、( 恢复现场) 和( 开中断) 阶段。

9. 操作数寻址方式包括( 直接寻址)、(间接寻址)、( 立即寻址)、( 隐含寻址)、( 寄存器寻址)、( 寄存器间接寻址)、( 基址寻址)等。

10. 动态 RAM 的刷新包括 ( 分散刷新)、( 集中刷新)和( 异步刷新)三种方式。

11. 高速缓冲存储器的替换算法有( 先进先出)和( 近期最少使用)。

12. 影响流水线性能的因素有( 数据相关)、( 控制相关)和( 资源相关)。

13. 主存储器容量通常以 KB 为单位,其中 1K=(),硬盘的容量以 GB 为单位,其中 1G=()。

14. 主存储器一般采用( 动态 RAM )存储器,CACHE 采用( 静态 RAM )存储器。

15. 世界上第一台计算机产生于( 1946 )年,称为( ENIAC )。

16. I/O 的编址可分为( 不统一编址) 和( 统一编址),前者需要单独的 I/O 指令,后者可通过( 访存) 指令和设备交换信息。

17. CPU 从主存取出一条指令并执行该指令的全部时间叫做( 指令周期),它通常包含若干个( 机器周期),而后者又包含若干个( 时钟周期)。

2021年北京理工大学计算机应用技术专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、关于LRU算法,以下论述正确的是()。

A.LRU算法替换掉那些在Cache中驻留时间最长且未被引用的块B.LRU算法替换掉那些在Cache中驻留时间最短且未被引用的块C.LRU算法替换掉那些在Cache中驻留时间最长且仍在引用的块D.LRU算法替换掉那些在Cache中驻留时间最短且仍在引用的块2、假定编译器将赋值语句“x=x+3;”转换为指令“add xaddr,3”,其中xaddr是x 对应的存储单元地址。

若执行该指令的计算机采用页式虚拟存储管理方式,并配有相应的TLB,且Cache使用直写(Write Trough)方式,则完成该指令功能需要访问主存的次数至少是()。

A.0B.1C.2D.343、在浮点机中,()是隐藏的。

A.阶码B.数符C.尾数D.基数4、假设寄存器的内容为00000000,若它等于-128,则该机器采用了()。

A.原码B.补码C.反码D.移码5、有如下C语言程序段:()short si=-32767;unsigned short usi=si;执行上述两条语句后,usi的值为A.-32767B.32767C.32768D.327696、在计数器定时查询方式下,正确的描述是()。

A.总线设备的优先级可变B.越靠近控制器的设备,优先级越高C.各设备的优先级相等D.对硬件电路故障敏感7、内部总线(又称片内总线)是指()。

A.CPU内部连接各寄存器及运算部件之间的总线B.CPU和计算机系统的其他高速功能部件之间互相连接的总线C.多个计算机系统之间互相连接的总线D.计算机系统和其他系统之间互相连接的总线8、已知计算机A的时钟频率为800MHz,假定某程序在计算机A上运行需要12s。

现在硬件设计人员想设计计算机B,希望该程序在B上的运行时间能缩短为8s,使用新技术后可使B的时钟频率大幅度提高,但在B上运行该程序所需要的时钟周期数为在A上的1.5倍。

第一章计算机系统概论计算机的硬件是由有形的电子器件等构成的,它包括运算器、存储器、控制器、适配器、输入输出设备。

早起将运算器和控制器合在一起称为CPU(中央处理器)。

目前的CPU包含了存储器,因此称为中央处理器。

存储程序并按地址顺序执行,这是冯·诺依曼型计算机的工作原理,也是CPU自动工作的关键。

计算机系统是一个有硬件、软件组成的多级层次结构,它通常由微程序级、一般程序级、操作系统级、汇编语言级、高级语言级组成,每一级上都能进行程序设计,且得到下面各级的支持。

习题:4冯·诺依曼型计算机的主要设计思想是什么?它包括那些主要组成部分?主要设计思想是:存储程序通用电子计算机方案,主要组成部分有:运算器、逻辑控制装置、存储器、输入和输出设备5什么是存储容量?什么是单元地址?什么是数据字?什么是指令字?存储器所有存储单元的总数称为存储器的存储容量。

每个存储单元都有编号,称为单元地址。

如果某字代表要处理的数据,称为数据字。

如果某字为一条指令,称为指令字7指令和数据均存放在内存中,计算机如何区分它们是指令还是数据?每一个基本操作称为一条指令,而解算某一问题的一串指令序列,称为程序第二章运算方法和运算器按对阶操作。

直接使用西文标准键盘输入汉字,进行处理,并显示打印汉字,是一项重大成就。

为此要解决汉字的输入编码、汉字内码、子模码等三种不同用途的编码。

1第三章 内部存储器CPU 能直接访问内存(cache 、主存)双端口存储器和多模块交叉存储器属于并行存储器结构。

cache 是一种高速缓冲存储器,是为了解决CPU 和主存之间速度不匹配而采用的一项重要的硬件技术,并且发展为多级cache 体系,指令cache 与数据cache 分设体系。

要求cache 的命中率接近于1适度地兼顾了二者的优点又尽量避免其缺点,从灵活性、命中率、硬件投资来说较为理想,因而得到了普遍采用。

习题: 1设有一个具有20位地址和32位字长的存储器,问:(1)该存储器能存储多少个字节的信息?(2)如果存储器由512K ×8位SRAM 芯片组成,需要多少片;(3)需要多少位地址做芯片选择?(1)字节M 4832*220= (2)片84*28*51232*1024==K K (3)1位地址作芯片选择 2 已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位DRAM 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问:(1) 若每个内存条16M ×64位,共需几个内存条?(2)每个内存条共有多少DRAM 芯片? (3)主存共需多少DRAM 芯片?CPU 如何选择各内存条?(1). 共需模块板数为m :m=÷2^24=4(块)(2). 每个模块板内有DRAM 芯片数为32 (片)(3) 主存共需DRAM 芯片为:4*32=128 (片)每个模块板有32片DRAM 芯片,容量为16M ×64位,需24根地址线(A23~A0) 完成模块板内存储单元寻址。

2022年北京理工大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、关于LRU算法,以下论述正确的是()。

A.LRU算法替换掉那些在Cache中驻留时间最长且未被引用的块B.LRU算法替换掉那些在Cache中驻留时间最短且未被引用的块C.LRU算法替换掉那些在Cache中驻留时间最长且仍在引用的块D.LRU算法替换掉那些在Cache中驻留时间最短且仍在引用的块2、容量为64块的Cache采用组相联映射方式,字块大小为128个字,每4块为一组。

如果主存为4K块,且按字编址,那么主存地址和主存标记的位数分别为()。

A.16,6B.17,6C.18,8 D .19,83、在定点机中执行算术运算时会产生溢出,其根本原因是()。

A.主存容量不够B.运算结果无法表示C.操作数地址过大D.栈溢出4、ALU属于()。

A.时序电路B.控制器C.组合逻辑电路D.寄存器5、并行加法器中,每位全和的形成除与本位相加两数数值位有关外,还与()有A.低位数值大小B.低位数的全和C.高位数值大小D.低位数送来的进位6、在链式查询方式下,若有N个设备,则()。

A.只需一条总线请求线B.需要N条总线请求线C.视情况而定,可能一条,也可能N条D.以上说法都不对7、在下面描述的PCI总线的基本概念中,不正确的表述是()。

A.PCI总线支持即插即用B.PCI总线可对传输信息进行奇偶校验C.系统中允许有多条PCI总线D.PCI设备一定是主设备8、假定机器M的时钟频率为200MHz,程序P在机器M上的执行时间为12s。

对P优化时,将其所有乘4指令都换成了一条左移两位的指令,得到优化后的程序P。

若在M上乘法指令的CPl为102,左移指令的CPl为z,P的执行时间是P”执行时间的1.2倍,则P中的乘法指令条数为()。

A.200万B.400万C.800万D.1600万9、在计算机系统中,表明系统运行状态的部件是()。

2021年北京理工大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下列关于ROM和RAM的说法中,错误的是()。

I.CD-ROM是ROM的一种,因此只能写入一次ⅡFlash快闪存储器属于随机存取存储器,具有随机存取的功能Ⅲ.RAM的读出方式是破坏性读出,因此读后需要再生IV.SRAM读后不需要刷新,而DRAM读后需要刷新A.I、ⅡB.I、Ⅲ、ⅣC.Ⅱ、ⅢD.I、Ⅱ、lⅢ2、若单译码方式的地址输入线为6,则译码输出线有()根,那么双译码方式有输出线()根。

A.64,16B.64,32C.32,16D.16,643、关于浮点数在IEEE754标准中的规定,下列说法中错误的是()。

I.浮点数可以表示正无穷大和负无穷大两个值Ⅱ.如果需要,也允许使用非格式化的浮点数Ⅲ.对任何形式的浮点数都要求使用隐藏位技术IⅣ.对32位浮点数的阶码采用了偏移值为l27的移码表示,尾数用原码表示4、对于相同位数(设为N位,且各包含1位符号位)的二进制补码小数和十进制小数,(二进制小数所表示的数的个数)/(十进制小数所能表示的数的个数)为()。

A.(0.2)NB. (0.2)N-1C. (0.02)ND. (0.02)N-15、有如下C语言程序段:()short si=-32767;unsigned short usi=si;执行上述两条语句后,usi的值为A.-32767B.32767C.32768D.327696、总线的数据传输速率可按公式Q=Wf/N计算,其中Q为总线数据传输速率,W为总线数据宽度(总线位宽/8),f为总线时钟频率,N为完成一次数据传送所需的总线时钟周期个数。

若总线位宽为16位,总线时钟频率为8MHz,完成一次数据传送需2个总线时钟周期,则总线数据传输速率Q为()。

A.16Mbit/sB.8Mbit/sC.16MB/sD.8MB/s7、在下面描述的PCI总线的基本概念中,不正确的表述是()。