cmos实验详解

- 格式:doc

- 大小:4.43 MB

- 文档页数:48

计算机科学与技术系

实验报告

课程名称:计算机组装与维护实训实验名称:系统cmos参数设置

姓名:王欢学号************ 日期:10.23-24 地点:十二机房

成绩:教师:张毓福

一、实验目的

掌握cmos参数设置。

二、实验内容

1.电脑开机时根据提示按键进入BIOS设置界面

2.根据课本和资料了解BIOS功能

3.查看cmos参数,掌握修改cmos基本参数,来对时间、日期、等修改,查看硬盘、内存配置情况,设置密码等。

三、实验原理

Cmos参数设置的作用及功能、BIOS功能

四、实验设备

一台运行正常的计算机

五、实验过程及分析

1.根据开机提示进入BIOS设置界面

2.掌握BIOS设置的功能

3.实际操作设置cmos参数,调整时间、日期、设置密码等

4. 了解装系统时设置的启动顺序

六、实验小结

在本次实验中,我通过对计算机的cmos参数设置,知道了怎样修改计算机的时间、日期、设置密码等,怎样更改计算机启动顺序,如何查看计算机硬盘、内存的配置。

实验二 C MOS 、TTL 逻辑门电路测试一、实验目的1、掌握C MOS 、TTL 逻辑门电路特性测试的方法。

2、掌握CMOS 、TTL 逻辑门电路的主要技术指标。

3、比较CM OS 门和TT L门的特点。

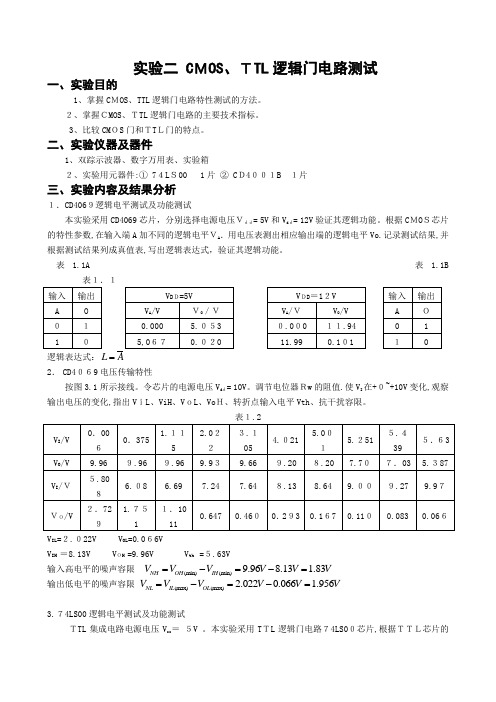

二、实验仪器及器件1、双踪示波器、数字万用表、实验箱2、实验用元器件:① 74L S00 1片 ② C D4001B 1片三、实验内容及结果分析1.CD4069逻辑电平测试及功能测试本实验采用CD4069芯片,分别选择电源电压Vdd= 5V 和V d d= 12V 验证其逻辑功能。

根据C MO S芯片的特性参数,在输入端A 加不同的逻辑电平VA .用电压表测出相应输出端的逻辑电平Vo.记录测试结果,并根据测试结果列成真值表,写出逻辑表达式,验证其逻辑功能。

表 1.1A 表 1.1B逻辑表达式:L =2. CD4069电压传输特性按图3.1所示接线。

令芯片的电源电压V d d= 10V 。

调节电位器Rw 的阻值.使V I 在+0~+10V 变化,观察输出电压的变化,指出V iL 、ViH 、V oL 、Vo H、转折点输入电平Vth 、抗干扰容限。

V IL =2.022V V OL =0.066VV IH =8.13V V OH =9.96V V th =5.63V输入高电平的噪声容限 (min)(min)9.968.13 1.83NH OH IH V V V V V V =-=-= 输出低电平的噪声容限 (max)(max) 2.0220.066 1.956NL IL OL V V V V V V =-=-=3.74LS00逻辑电平测试及功能测试TTL 集成电路电源电压V cc = 5V 。

本实验采用T TL 逻辑门电路74LS00芯片,根据TTL芯片的特性参数,在输入端A 、B 加不同的逻辑电平V A 、V B .用电压表测出相应输出端的逻辑电平Vo.记录测试结果,并根据测试结果列成真值表,写出逻辑表达式,验证其逻辑功能。

CMOS集成逻辑门的逻辑功能与参数测试实验报告实验目的:1.了解CMOS集成逻辑门的逻辑功能和参数;2.掌握用示波器测试CMOS集成逻辑门的方法;3.了解逻辑门的工作特性。

实验仪器和器材:1.CMOS集成逻辑门芯片;2.示波器;3.线路连接线;4.双电源供电器。

实验原理:实验过程:1.将CMOS集成逻辑门芯片插入实验台上提供的插槽中,并确保插入位置正确;2.将线路连接线分别连接到CMOS集成逻辑门芯片的输入端和输出端,并另一端连接至示波器的输入端;3.将双电源供电器的正极和负极分别连接到CMOS集成逻辑门芯片的VDD和VSS端;4.启动双电源供电器,并将VDD设置为高电平(一般为5V),VSS设置为低电平(一般为0V);5.依次测试CMOS集成逻辑门芯片中的各个逻辑门的功能和参数,将输入信号引至对应的输入端,并利用示波器观察输出信号的波形。

实验数据:以CMOS集成逻辑门中的与门(AND gate)为例,测试其逻辑功能和参数。

逻辑功能测试:根据与门的真值表,输入A、B两个信号,输出结果与输入信号直接相与的结果一致。

参数测试:1.高电平输出电压(VOH):在输入信号全为高电平的情况下,测量输出信号的高电平电压值。

一般要求VOH>4.5V。

2.低电平输出电压(VOL):在输入信号全为低电平的情况下,测量输出信号的低电平电压值。

一般要求VOL<0.5V。

3.高电平输入电压(VIH):测量输入信号被识别为高电平的最小电压值。

一般要求VIH>3.5V。

4.低电平输入电压(VIL):测量输入信号被识别为低电平的最大电压值。

一般要求VIL<1.5V。

5.高电平供电电压(VDD):测量供电电压的高电平值。

6.低电平供电电压(VSS):测量供电电压的低电平值。

实验结果:根据实验测量数据,以及对比逻辑功能和参数测试的要求,可以得出实验结果。

结论:CMOS集成逻辑门具有低功耗、高DV/DDP性能以及防静电能力强等优点。

CMOS实验报告模拟集成电路设计实验报告学院:班级:学号:姓名:班内序号:实验一:共源级放大器性能分析一、实验目的1、掌握synopsys 软件启动和电路原理图(schematic )设计输入方法;2、掌握使用synopsys 电路仿真软件custom designer对原理图进行电路特性仿真;3、输入共源级放大器电路并对其进行DC 、AC 分析,绘制曲线;4、深入理解共源级放大器的工作原理以及mos 管参数的改变对放大器性能的影响二、实验要求1、启动synopsys ,建立库及Cellview 文件。

2、输入共源级放大器电路图。

3、设置仿真环境。

4、仿真并查看仿真结果,绘制曲线。

三、实验结果1、电路图2、幅度和相位曲线3、部分参数四、实验结果分析器件参数:NMOS 管的宽长比为10,栅源之间所接电容1pF ,Rd=10K。

实验结果:由仿真结果有:gm=173u,Rd=10k,所以增益Av=173*10/1000=1.73=4.76dB实验二:差分放大器设计一、实验目的1. 掌握差分放大器的设计方法;2. 掌握差分放大器的调试与性能指标的测试方法。

二、实验要求1. 确定放大电路;2. 确定静态工作点Q ;3. 确定电路其他参数。

4. 电压放大倍数大于20dB ,尽量增大GBW ,设计差分放大器;5.对所设计电路调试;6. 对电路性能指标进行测试仿真,并对测量结果进行验算和误差分析。

三、实验原理平衡态下的小信号差动电压增益AV 为:四、实验结果改变W/L和栅极电阻,可以看到,R 一定时,随着W/L增加,增益增加,W/L一定时,随着R 的增加,增益也增加。

但从仿真特性曲线我们可以知道,这会限制带宽的特性,W/L增大时,带宽会下降。

为保证带宽,选取W/L=25,R=20K的情况下的数值,保证了带宽约为500MHZ ,可以符合系统的功能特性,实验结果见下图。

1. 电路图2. 幅频特性曲线该图增益为26.9Db, 采用W/L为25,R 取30k ,带宽约为300M五、思考题根据计算公式,为什么不能直接增大R 实现放大倍数的增大?答:若直接增加Rd ,则Vd 会增加,增加过程中会限制最大电压摆幅;如果VDD —Vd=Vin—VTH ,那MOS 管处于线性区的边缘,此时仅允许非常小的输出电压摆幅。

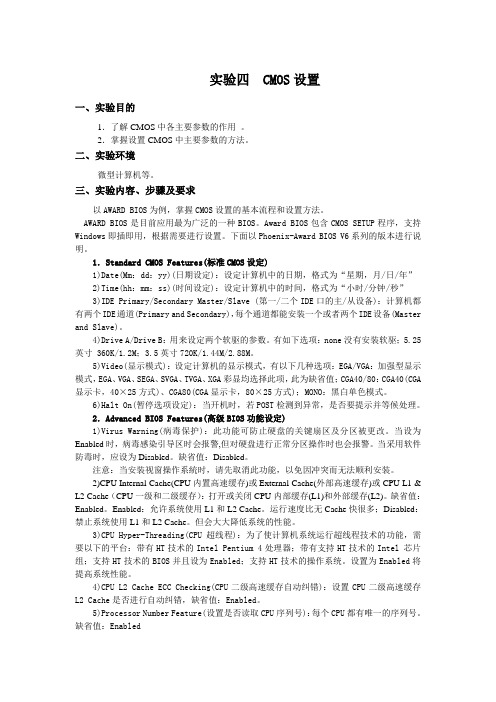

实验四 CMOS设置一、实验目的1.了解CMOS中各主要参数的作用。

2.掌握设置CMOS中主要参数的方法。

二、实验环境微型计算机等。

三、实验内容、步骤及要求以AWARD BIOS为例,掌握CMOS设置的基本流程和设置方法。

AWARD BIOS是目前应用最为广泛的一种BIOS。

Award BIOS包含CMOS SETUP程序,支持Windows即插即用,根据需要进行设置。

下面以Phoenix-Award BIOS V6系列的版本进行说明。

1.Standard CMOS Features(标准CMOS设定)1)Date(Mm:dd:yy)(日期设定):设定计算机中的日期,格式为“星期,月/日/年”2)Time(hh:mm:ss)(时间设定):设定计算机中的时间,格式为“小时/分钟/秒”3)IDE Primary/Secondary Master/Slave (第一/二个IDE口的主/从设备):计算机都有两个IDE通道(Primary and Secondary),每个通道都能安装一个或者两个IDE设备(Master and Slave)。

4)Drive A/Drive B:用来设定两个软驱的参数。

有如下选项:none没有安装软驱;5.25英寸 360K/1.2M;3.5英寸720K/1.44M/2.88M。

5)Video(显示模式):设定计算机的显示模式,有以下几种选项:EGA/VGA:加强型显示模式,EGA、VGA、SEGA、SVGA、TVGA、XGA彩显均选择此项,此为缺省值;CGA40/80:CGA40(CGA 显示卡,40×25方式)、CGA80(CGA显示卡,80×25方式);MONO:黑白单色模式。

6)Halt On(暂停选项设定):当开机时,若POST检测到异常,是否要提示并等候处理。

2.Advanced BI0S Features(高级BI0S功能设定)1)Virus Warning(病毒保护):此功能可防止硬盘的关键扇区及分区被更改。

(1) 输出高低电压OH U 和OL U输出端不带任何负载时,当输入端全部接高电平OH U 时,测得的输出电平就是OL U (=)0;当输入端有一个为低电平时,测得的低电平就是OH U (=DD U ) (2) 拉电流和灌电流负载能力图2.2-3所示电路中,输入端接低电平,输出端接拉电流负载L R ,调节L R ,当OL U 上升到0.5V 时所对应的负载电流,即为OL I 。

3、 电压传输特性CMOS 门电路电压传输特性的测试方法类似于TTL 门电路。

图2-4为逐点测量电压传输特性的实验电路。

oHoL(a )(b )图2.2-2(a )(b )图2.2-3ΩK由示波CMOS 与非门CD4011的主要参数规范(DD U =10V )(1) 静态电源电流≤5uA;(2).输出低电平0.1V;(3).输出高电平9.5V ;(4).输出驱动电流OL I >300uA,OH I >300uA;(5).最大允许电压18V ;(6). 最小允许电压3V ;(7).输出延迟时间pdH t =300~150ns,pdL t = 300~150ns ;(8).输入电容5pF5、 CMOS 电路使用注意事项(1)DD U 接电源正极,SS U 接电源负极(通常接地),电源绝对不容反接。

(2)电源电压使用范围+3V ~+18V ,实验中一般要求使用+12V 或+5V 电源。

工作在不同电源电压下的器件,其输出阻抗、工作速度和功耗等参数也会不同,在设计、使用中应引WR K 100图2.2-4起注意。

(3)器件输入信号i U ,要求DD i SS U U U <<范围内。

(3) 闲置输入端一律不准悬空,输入端悬空,不仅会造成逻辑混乱,而且容易损坏器件。

闲置输入端的处理方法:a. 按照逻辑要求,直接接DD U 或SS U .b. 工作速度不高的电路中允许与有用输入端并联使用。

(4) 输出端不允许直接与DD U 或SS U 连接,否则将导致器件损坏。

cmos反向器电路设计实验报告CMOS反向器电路设计实验报告摘要:本实验通过设计和实现CMOS反向器电路,验证其基本功能和性能。

通过实验测试,我们评估了反向器的输入电压和输出电压之间的关系,以及其延迟时间和功耗等性能指标。

实验结果表明,所设计的CMOS反向器电路具有较高的性能和可靠性。

引言:CMOS(互补金属氧化物半导体)技术是集成电路设计中最常用的工艺之一,其具有功耗低、噪声抑制能力强等优点,在现代电子设备中得到广泛应用。

反向器是CMOS电路中最基本的逻辑门,其功能是将输入信号反转输出。

本实验旨在通过设计和实现CMOS反向器电路,验证其基本功能和性能。

材料与方法:1. 实验所需材料:- 电路设计软件(如LTspice)- CMOS反向器电路元件(晶体管、电阻、电容等)- 直流电源- 示波器2. 实验步骤:1) 在电路设计软件中绘制CMOS反向器电路原理图。

2) 根据设计要求,选择合适的晶体管、电阻和电容等元件。

3) 连接电路并进行仿真测试,调整电阻和电容等参数,以满足设计要求。

4) 使用直流电源为电路供电,并使用示波器测量输入和输出信号的波形。

5) 记录和分析实验数据,并评估反向器的性能。

结果与讨论:通过实验测试,我们得到了CMOS反向器电路的输入和输出电压之间的关系。

我们观察到,当输入电压为高电平时,输出电压为低电平;而当输入电压为低电平时,输出电压为高电平。

这验证了反向器的基本功能。

我们还测试了反向器的延迟时间和功耗。

延迟时间是指输入信号从发生变化到输出信号发生变化之间的时间。

实验结果显示,CMOS 反向器的延迟时间较短,具有较高的响应速度。

功耗是指电路在工作过程中消耗的能量。

实验结果显示,CMOS反向器的功耗较低,符合低功耗设计的要求。

结论:通过本次实验,我们成功设计和实现了CMOS反向器电路,并验证了其基本功能和性能。

实验结果表明,所设计的反向器具有较高的性能和可靠性。

CMOS技术的广泛应用将进一步推动集成电路的发展,为现代电子设备的制造和应用提供了有力支持。

1.实验目的1.1了解Schematic设计环境1.2掌握反相器电路原理图输入方法1.3掌握逻辑符号创建方法2实验原理在Schematic设计环境中本实验所用的主要菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。

其中常用菜单有:Tool菜单提供设计工具以及辅助命令。

比如,lab4、lab5所使用的仿真工具ADE,就在Tool下拉菜单中。

Window菜单中的各选项有调整窗口的辅助功能。

比如,Zoom选项对窗口放大(Zoom in)与缩小(Zoom out),fit选项将窗口调整为居中,redraw选项为刷新。

Edit菜单实现具体的编辑功能,主要有取消操作(Undo)、重复操作(Redo)、拉伸(Stretch)、拷贝(copy)、移动(Move)、删除(Delete)、旋转(Rotate)、属性(Properties)、选择(Select)、查找(Search)等子菜单,在以下实验中将大量应用。

Add菜单用于添加编辑所需要的各种素材,比如元件(Instance)或输入输出端点(pin)等。

3实验步骤3.1在ic5141中设计的管理以库的方式进行。

库管理器中包含有设计使用的工艺库和ic5141软件提供的一些元件库。

无论画电路图还是设计版图,都和建库有关,所以首先建立一个库文件,方法如下:CIW界面点击File菜单,出现下拉菜单,选命令File→New→Library,出现“New Library”对话框,填入合适的信息,如图1所示。

新建库后面还将用于版图绘制,选第二个选项,即“Attach to an existing techfile”,单击“OK”按钮,完成新库的建立。

3.2电路原理图输入设计库建好后,就可以开始画电路原理图,具体过程如下。

建立设计原理图:在CIW中选菜单单项File→New→Cellview,出现“Create new File”对话框,如图所示填写、选择相应的选项,点击OK按钮,进入原理如编辑器。

实验二CMOS模拟集成电路设计与仿真实验二 CMOS 模拟集成电路设计与仿真CMOS(Complementary Metal-Oxide-Semiconductor)模拟集成电路(Analog Integrated Circuits)是一种基于金属-氧化物-半导体结构的集成电路技术。

在本实验中,我们将学习并实践CMOS模拟集成电路的设计和仿真,以加深对其原理和应用的理解。

通过此实验,我们将能够熟练掌握CMOS模拟集成电路设计与仿真的基本流程与方法。

一、实验目的本实验旨在通过设计和仿真CMOS模拟集成电路,加深对其工作原理的理解,掌握电路设计与仿真的基本方法。

二、实验原理CMOS模拟集成电路是一种基于n型和p型MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)的电路。

通过调节不同MOS管的工作状态,可以实现不同的电路功能。

其中,n型MOS管的主要特点是电导率高,适用于放大增益较大的部分;p型MOS管的主要特点是电导率低,适用于控制电流流动的部分。

三、实验步骤1. 电路设计:根据实际需求,确定设计所需的CMOS模拟集成电路。

在设计前,应先详细了解电路的功能、性能及工作原理,确定所需的器件数目和性能参数。

2. 电路布局:根据设计要求,将设计的各个电路模块在模拟集成电路上进行布局,合理安排电路的位置和空间,以保证电路的稳定性和性能。

3. 电路连接:按照布局图,将所需的电路模块进行连接,确保各个模块之间信号的正确传输和电路功能的正常实现。

4. 电路仿真:使用专业的仿真软件,将设计好的CMOS模拟集成电路进行仿真,验证其电路性能和功能。

在仿真过程中,应注意选择合适的仿真参数和验证方法,以保证仿真结果的准确性和可靠性。

5. 仿真分析:根据仿真结果,对电路的性能和功能进行分析和评估。

如果发现问题或改进的空间,可以根据分析结果进行相应的调整和优化。

6. 总结与展望:根据实验结果和分析,总结实验过程中的经验和教训,提出可能的改进和未来的研究方向。