第7章TMS320C54XDSP片内外设—09.11

- 格式:pdf

- 大小:815.62 KB

- 文档页数:40

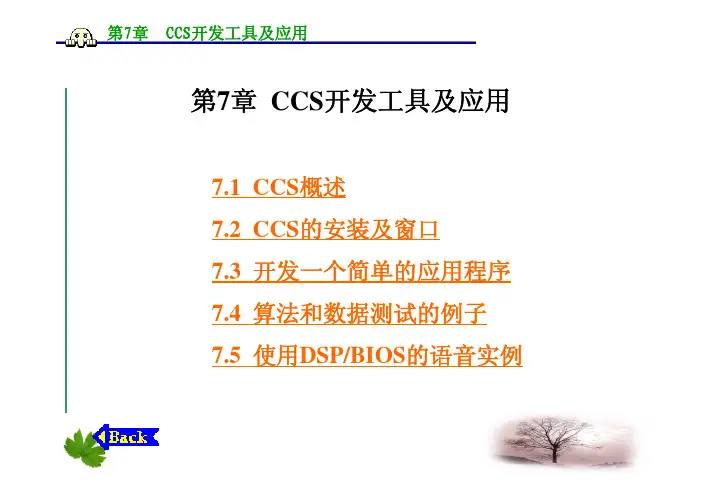

第7章CCS开发工具及应用7.1 CCS概述7.2 CCS的安装及窗口7.3 开发一个简单的应用程序7.4 算法和数据测试的例子7.5 使用DSP/BIOS的语音实例7.1 CCS 概述7.1.1 CCS的发展CCS提供了基本代码生成工具,它具有一系列的调试、分析能力。

CCS支持如图7-1所示的开发周期中的所有阶段。

设计概念性规划编程和编译创建工程文件,编写源程序和配置文件调试语法检查,探测点设置和日志保存等分析实时调试、统计和跟踪图7-1 CCS开发周期在学习本章之前,读者需要完成下述工作:●安装好目标板和相应的驱动程序。

安装时请参考硬件厂商提供的安装说明书。

●安装CCS软件。

安装时也根据安装说明书安装。

如果你已经有了CCS仿真器和TMS320C54x代码生成工具,但是没有完整的CCS,可按照7.2节的步骤进行安装。

●运行CCS安装程序。

安装程序为目标板提供驱动程序,安装完成后就可以使用目标板上所提供的设备。

Code Composer Studio(CCS)是TI公司推出的一个集成性DSP软件开发工具。

在一个开放式的插件(Plug-In)结构下,CCS内部集成了以下软件工具:●TMS320C54x代码生成工具(参见7.1.2节);●CCS集成开发环境(IDE)(参见7.1.3节);●DSP/BIOS插件程序和API(参见7.1.4节);●RTDX插件、主机接口和API(参见7.1.5节)。

CCS的构成及其在主机和目标系统中的接口如图7-2所示。

图7-2 CCS 构成及其接口ConfigurationToolCode Composer EditorSource Files .c.h.asmDSP/BIOS APICode Composer Project.cdb (Config Database)cfg.cmd cfg.s54cfg.h54Code Generation Tools Compiler.Assembler.Linker…OLEApplication Using RTDX RTDX Plug-in DSP/BIOS Plug -ins 3rd party Plug -ins Code Composer Debugger Host Emulation SupportCode Composer StudioHostDSP TargetDSP Application ProgramTarget HardwareJTAGRTDXDSP/BIOS Executable7.1.2 代码生成工具代码生成工具是CCS开发环境的基础部分。

第一章:1、数字信号处理的实现方法一般有哪几种?答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。

(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4)用通用的可编程 DSP 芯片实现。

与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现( 6)用基于通用 dsp 核的asic 芯片实现。

2、简单的叙述一下 dsp 芯片的发展概况?答:第一阶段, DSP 的雏形阶段( 1980 年前后)。

代表产品: S2811。

主要用途:军事或航空航天部门。

第二阶段, DSP 的成熟阶段( 1990 年前后)。

代表产品: TI 公司的 TMS320C20主要用途:通信、计算机领域。

第三阶段, DSP 的完善阶段( 2000 年以后)。

代表产品:TI 公司的 TMS320C54 主要用途:各个行业领域。

3、可编程 dsp 芯片有哪些特点?答: 1、采用哈佛结构( 1)冯。

诺依曼结构,( 2)哈佛结构( 3)改进型哈佛结构2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗4、什么是哈佛结构和冯。

诺依曼结构?它们有什么区别?答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯。

诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

第1章绪论TMS320C54x TM DSP是TMS320TM系列DSP产品中的定点数字信号处理器。

C54x DSP 满足了实时嵌入式应用的一些要求,例如通信方面的应用。

C54x的中央处理单元(CPU)具有改进的哈佛结构,它的特点是最小化的功耗和高度的并行性。

除此之外,C54x中多样化的寻址方式和指令集也大大提高了整个系统的性能。

1.1 TMS320系列DSP简介TMS320TM系列DSP包括定点DSP、浮点DSP和多处理器DSP(也称DSPs),其结构是专门为实时的信号处理设计的。

TMS320系列DSP有以下一些特性使得该系列的产品有着广阔的应用领域:❑非常灵活的指令集。

❑固有的操作灵活性。

❑高速运行的性能。

❑创新的并行结构。

❑成本效率高。

❑对C语言的友好的结构。

1.1.1 TMS320系列DSP的历史、发展和优势1982年,德州仪器公司(TI)推出了TMS320系列中第一代定点DSP产品——TMS320C10。

在这一年年末,《电子产品》杂志赠予TMS320C10“年度产品”的称号。

TMS320C10成为后续的TMS320系列DSP的模型。

今天,TMS320 DSP系列包括三大DSP平台:TMS320C2000TM、TMS320C5000TM和TMS320C6000TM。

在C5000TM DSP平台中又包含三代产品:TMS320C5x TM、TMS320C54x TM 和TMS320C55x TM系列。

C5000 DSP平台中的器件都采用了相同的CPU结构,但结合了不同的片内存储器和外设结构。

这些不同的结构满足了世界范围内电子市场的很多领域的需要。

当把存储器、外设和CPU结合起来集成到单个芯片上时,整个系统的费用就大大地降低了,电路板的体积也减小了。

图1-1所示为TMS320系列器件的演化过程。

TMS320C54x系列DSP的CPU与外设2控制最优化平台高效益平台高性能平台图1-1 TMS320系列DSP的演化过程1.1.2 TMS320系列DSP的典型应用表1-1列出了TMS320系列DSP的一些典型的应用。

TMS320C54x DSP CPU与外设第一章综述1 总线结构C54x包括8条16比特宽度的总线,其中:●一条程序总线(PB)●三条数据总线(CB、DB、EB)●四条地址总线(PAB、CAB、DAB、EAB)2CPUC54x的CPU结构包括:●40比特的ALU,其输入来自16比特立即数、16比特来自数据存储器的数据、暂时存储器、T中的16比特数、数据存储器中两个16比特字、数据存储器中32比特字、累加器中40比特字。

●2个40比特的累加器,分为三个部分,保护位(39-32比特)、高位字(31-16比特)、低位字(15-0比特)。

●桶型移位器,可产生0到31比特的左移或0到16比特的右移。

●17×17比特的乘法器●40比特的加法器●比较选择和存储单元CSSU●数据地址产生器DAGEN●程序地址产生器PAGEN3设C54x包括:通用I/O引脚,XF和定时器●定时器●PLL时钟产生器●HPI口,8比特或16比特●同步串口●带缓存串口,BSP●多路带缓存串口,McBSP●时分复用串口,TDM●可编程等待状态产生器●可编程bank-switching模块●外部总线接口●IEEE1149.1标准JTAG口第二章存储器一般而言,C54x 的存储空间可达192K16比特字,64K 程序空间,64K 数据空间,64KI/O 空间。

依赖其并行的工艺特性和片上RAM 双向访问的性能,在一个机器周期内,C54x 可以执行4条并行并行存储器操作:取指令,两操作数读,一操作数写。

使用片内存储器有三个优点:高速执行(不需要等待),低开销,低功耗。

1 存储空间分配图(以C549为例)复位后,中断矢量表位于程序区FF80H 位置,可重新定位于程序空间任何一个128字的页面(其地址高9比特即页号由PMST 中IPTR 确定)。

2 程序存储区C54x 有片内ROM 、DARAM 、SARAM ,这些区域可以通过软件配置到程序空间。

第二章3、处理器工作方式状态寄存器PMST 中的MP/MC、OVLY 和DROM 三个状态位对C54x的存储空间结构各有何影响?当OVLY= 0 时,程序存储空间不使用内部RAM。

当OVLY= 1 时,程序存储空间使用内部RAM。

内部RAM 同时被映射到程序存储空间和数据存储空间。

当MP/ MC=0 时,4000H~EFFFH 程序存储空间定义为外部存储器;F000H~FEFFH 程序存储空间定义为内部ROM;当MP/ MC=1 时,4000H~FFFFH 程序存储空间定义为外部存储。

DROM=0:0000H~3FFFH——内部RAM ;4000H~FFFFH——外部存储器;DROM=1 :0000H~3FFFH——内部RAM;4000H~EFFFH——外部存储器;F000H~FEFFH——片内ROM;FF00H~FFFFH——保留。

4 、TMS320C54x 芯片的片内外设主要包括哪些电路?①通用I/O 引脚②定时器③时钟发生器④主机接口HPI⑤串行通信接口⑥软件可编程等待状态发生器⑦可编程分区转换逻辑5、TMS320C54x 芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?六个操作阶段:①预取指P;将PC 中的内容加载PAB ②取指F; 将读取到的指令字加载PB③译码D; 若需要,数据1 读地址加载DAB;若需要,数据2 读地址加载CAB;修正辅助寄存器和堆栈指针④寻址A; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB⑤读数R; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB;⑥执行X。

执行指令,写数据加载EB。

6、TMS320C54x 芯片的流水线冲突是怎样产生的?有哪些方法可以避免流水线冲突?答:’C54x 的流水线结构,允许多条指令同时利用CPU 的内部资源。

由于CPU 的资源有限,当多于一个流水线上的指令同时访问同一资源时,可能产生时序冲突。