DSPTMS320LF240x片内外设

- 格式:pptx

- 大小:6.28 MB

- 文档页数:122

TMS320LF240X系列DSP使用时,在掌握了其工作原理和过程之后,就要熟练使用DSP自带的一些资源如:IO口、DSRM、SRAM、EVA、,EVB、SCI、SPI、ADC和WD等等;对这些资源的使用很重要的一点就是对其合理配置和初始化,初始化的关键就是对其相关寄存器的设置,设置寄存器必须了解各位的含义,记住每位的含义是不大现实的;为此,我们专门设计了DSP初始化子程序,注明每个模块所用到的寄存器以及每位的含义,以方便设计。

;Init_DSP.asm.text;----------------------------------------------------------; function: Init DSP DSP初始化子程序; input: ------; output: ------; usege: aCC;==========================================================DSP_Init:;==========================================================; DSP系统初始化;----------------------------------------------------------;ST0------; 15~~13 12 11 10 9 8~~0;ST0 ARP OV OVM 1 INTM DP; 15~13 12 11 10 9 8~5 4 3~2 1~0;ST1 ARB CNF TC SXM C 1 XF 1 PM; ARB---辅助寄存器指针缓冲器:当ARP被加载到ST0,除了使用LST指令外,原有的; ARP值被复制到ARB中;当通过LST#1指令加载ARB时,也把相同的ARB; 值复制到ARP ;; ARP----辅助寄存器指针:ARP选择间接寻址时当前的辅助寄存器AR;当ARP被加载; 时,原有的ARP值被复制到ARB寄存器中;在间接寻址时,ARP可由存储器; 相关指令改变,也可由LARP,MAR,和LST指令改变;当执行LST#1指令; 时,ARP也可加载每ARB相同的值; C---- 进位位:此位在加法结果产生进位时被置为1,或在减法结果产生借位时被清0; 否则,除了执行带有16位移位的ADD或SUB指令外,C在加法后被清除或在减; 法后被设置;在ADD或USB指令时,ADD仅可对进位位进行置位而SUB仅可; 对进位位进行清除,而不会对进位位产生其他影响;移1位和循环指令也可影响; 进位位C,以及SETC、CLRC和LST指令也可影响C;条件转移、调用和返回; 指令可以根据C的状态进行执行;复位时C被置1; CNF----片内DARAM配置位:若CNF=0,可配置的双口RAM区被映射到数据存储空; 间;若CNF=I,可配置的双口RAM区被映射到程序存储空间;CNF位可通过; SETC CNF,CLRC CNF和LST指令修改;R/S/复位时CNF置为0; DP---- 数据存储器页指针:9位的DP寄存器与一个指令字的低七位一起形成一个16; 位的直接寻址地址; INTM---中断模式位:当INTM被置为0时,所有的未屏蔽中断使能;当它被置1,; 所有可屏蔽中断禁止;; OV---- 溢出标志位:该位保存一个被锁存的值,用以指示CALU中是否有溢出发生;; 一旦发生溢出,OV位保持为1直到下列条件中的一个发生时才能被清除; OVM----溢出方式位:当OVM=0时,累加器中结果正常溢出;当OVM=1时,根据; 遇到溢出的情况,累加器被设置为它的最大正值或负值;SETC指令和; CLRC指令分别对该位进行置位和复位;; PM----乘积移位方式:; 若PM=00,乘法器的32位乘积结果不移位直接装入CALU;; 若PM=01,PREG输出左移1位后装入CALU,最低位LSB以0填充;; 若PM=10,PREG输出左移4位后装入CALU,最低位LSB以0填充;; 若PM=11,时PREG输出进行符号扩展右移六位; SXM----符号扩展方式位:当SXM一1时,数据通过定标移位器传送到累加器时将产; 生符号扩展;SXM=0将抑制符号扩展;SXM位对某些指令没有影响;; TC---- 测试/控制标志位:在下述情况之一,TC位被置1:由BIT或BITT指令测; 试的位为1;当利用NORM指令测试时,累加器的两个最高有效位"异或"; 功能为真;条件转移、调用和返回指令可根据TC位的条件来执行;; BIT、BITT、CMPR、LST和NORM指令影响TC位; XF---- XF引脚状态位:该位决定XF引脚的状态;SETCXF指令可对位XF进行置位,; 而CLRCXF指令可对其进行清0;复位时XF置1;SCSR1------系统控制和状态寄存器1---地址7018H ; D15---保留位; D14---CLKSRC。

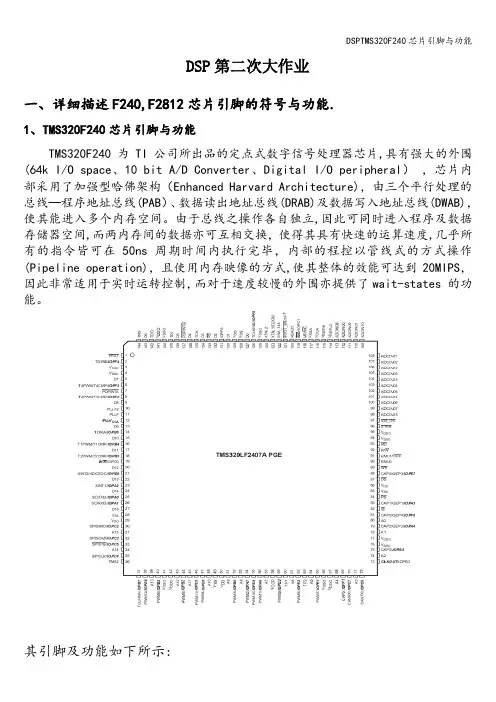

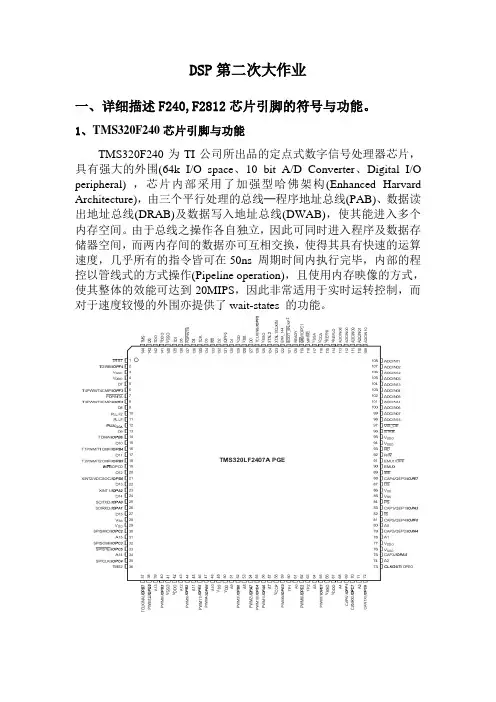

DSP第二次大作业一、详细描述F240,F2812芯片引脚的符号与功能.1、TMS320F240芯片引脚与功能TMS320F240为TI公司所出品的定点式数字信号处理器芯片,具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O peripheral),芯片内部采用了加强型哈佛架构(Enhanced Harvard Architecture),由三个平行处理的总线─程序地址总线(PAB)、数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能进入多个内存空间。

由于总线之操作各自独立,因此可同时进入程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其具有快速的运算速度,几乎所有的指令皆可在50ns 周期时间内执行完毕,内部的程控以管线式的方式操作(Pipeline operation),且使用内存映像的方式,使其整体的效能可达到20MIPS,因此非常适用于实时运转控制,而对于速度较慢的外围亦提供了wait-states 的功能。

其引脚及功能如下所示:2、TMS320F2812芯片引脚与功能德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motorcontrol, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。

针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C语言的环境中搭配汇编语言来撰写程序。

值得一提的是,F28xDSP核心支持特殊的IQ—math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。

F28x 系列DSP预计发展至400MHz,目前已发展至150MHz的Flash型式。

DSP常见问题解答如何选择外部时钟?DSP的内部指令周期较高,外部晶振的主频不够,因此DSP大多数片内均有PLL。

但每个系列不尽相同。

1)TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部时钟可以为5MHz-40MHz。

TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部时钟可以为2.22MHz-40MHz。

TMS320F241/C242/F243:PLL可以×4,因此外部时钟为5MHz。

TMS320LF24xx:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

TMS320LF24xxA:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

2)TMS320C3x系列:TMS320C3x:没有PLL,因此外部主频为工作频率的2倍。

TMS320VC33:PLL可以÷2,×1,×5,因此外部主频可以为12MHz -100MHz。

3)TMS320C5000系列:TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为0.625MHz-50MHz。

TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为6.25MHz-300MHz。

4)TMS320C6000系列:TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主频可以为11.8MHz-300MHz。

TMS320C67xx:PLL可以×1和×4,因此外部主频可以为12.5MHz-230MHz。

DSP第二次大作业一、详细描述F240,F2812芯片引脚的符号与功能。

1、TMS320F240芯片引脚与功能TMS320F240为TI公司所出品的定点式数字信号处理器芯片,具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O peripheral) ,芯片内部采用了加强型哈佛架构(Enhanced Harvard Architecture),由三个平行处理的总线─程序地址总线(PAB)、数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能进入多个内存空间。

由于总线之操作各自独立,因此可同时进入程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其具有快速的运算速度,几乎所有的指令皆可在50ns 周期时间内执行完毕,内部的程控以管线式的方式操作(Pipeline operation),且使用内存映像的方式,使其整体的效能可达到20MIPS,因此非常适用于实时运转控制,而对于速度较慢的外围亦提供了wait-states 的功能。

其引脚及功能如下所示:2、TMS320F2812芯片引脚与功能德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motor control, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。

针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C语言的环境中搭配汇编语言来撰写程序。

值得一提的是,F28xDSP 核心支持特殊的IQ-math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。

F28x 系列DSP预计发展至400MHz,目前已发展至150MHz的Flash型式。

DSP 基本知识引言TI公司在1982年成功推出其第一代DSP芯片之后,相继推出了多种适合不同应用、不同规格的DSP系列。

TMS320F240x DSP是为了满足控制应用而设计的,属于TMS320C2xx系列。

通过把一个高性能的DSP内核和微处理器的片内外部设备集成在一个芯片的方案,TMS320LF240x DSP成为传统微控制器和昂贵的多片设计的一种廉价替代产品。

3OMIPS的处理速度,使TMS320IF240x DSP可以远远超过传统的16位微控制器和微处理器的性能。

笔者曾用该系列芯片中的TMS320F2406开发过电动执行机构,得到了满意的结果。

结合自己的开发经验,笔者简要介绍TMS320LF240xDSP的硬件结构、C程序开发过程中若干关键的问题。

其中很多包括笔者的心得和体会。

1 TMS320LF240X DSP硬件结构特点TMS320LF240x DSP有以下一些特点:采用高性能静态CMOS技术,使得供电电压降为3.3V,减少了功耗;基于TMS320C2xxDSP的CPU核,保证与TMS320系列DSP代码兼容;片内有高达32K字的Flash程序存储器,544字的双口RAM(DARAM)和2K字的单口RAM(SARAM);两个事件管理器模块EVA和EVB,适用于控制各类电机;看门狗定时器模块(WDT);控制器局域网络(CAN)2.0B模块;串行通信接口(SCI)模块;16位的串行外设接口(SPI)模块;JTAG接口,使得在系统编程(ISP,)很容易实现;10位A/D转换器最小的转换时间为500ns,可选择由两个事件管理器来触发2个8通道输入A/D转换器或1个16通道输入A/D转换器,而每次要转换的通道都可通过编程来选择。

需要说明的是,TMS320LF240x DSF是定点l6位芯片,存储数据的最小单位是16位的字,每个地址(包括程序地址、数据地址及I/O地址)所存的数据都是16位。

1.1 改进的哈佛结构和流水线操作DSP采用程序空间和数据空间完全分开的哈佛(Havard)结构,允许同时取指令和操作数,而且允许在程序空间和数据空间之间相互传递数据,即改进的哈佛结构。

一、填空题1.命令文件用.cmd扩展名表示。

2.TMS320LF2407 DSP共有144引脚。

3.与C语言相比,汇编语言的可移植性较差4. 在数的定标中,如果采用Q表示法,一个Q8定点数的精度为1/165. TMS320LF2407 DSP内部含有8 个辅助寄存器。

6.TMS320LF240X DSP微处理器采用的是哈佛结构7. 采用DSP进行数字信号处理属于软硬件结合实现方法。

8. 一般情况下,下列器件在工作时,功耗最小的是小液晶块9. TMS320LF2407 DSP中,累加器的位数为:32位10.可编程数字信号处理器简称DSP11.看门狗的作用是PC受到干扰而跑飞时产生复位12.TMS320LF240X DSP有1个累加器。

13.输出比较功能一般用于在规定的时刻输出需要的电平14. TMS320LF240X DSP共有86条指令,分为6大类。

15.一般情况下,TMS320LF240X系列DSP内的用户程序存储在Flash存储器中16. TMS320LF240X DSP具有 4 个通用定时器,都采用16位计数器,计数范围是0-65535个脉冲。

17.ADD *+,8,AR4含义是:以当前AR中的内容为地址的数据存储单元内容左移8位后与ACC中内容相加,结果送与ACC,且AR中内容加一,并指定AR4为下一个当前AR。

18.在数的定标中,如果采用Q表示法,Q越大,数值范围越大,但精度越低。

19.LF240X中断源分为__软件______中断和__硬件______中断。

20. 在TMS320LF240X DSP中,优先级最高的中断是__复位______。

21.TMS320LF240X DSP共有__3____种基本的数据寻址方式,分别是立即、直接、间接。

22.按数据格式分类,DSP芯片可分为定点式芯片和浮点式芯片。

23.TMS320LF2407A DSP有3种低功耗模式。

24.DSP执行一条指令,需要通过取指、译码和执行等阶段。

1、DSP原理DSP数字信号处理器,是以数字信号来处理大量信息的器件,是一种适合于实现各种数字信号处理运算的伪处理器,也是嵌入式处理器的一种。

它具有丰富的硬件资源,改进的并型结构,高效的数据处理能力以及强大的指令系统等特点。

以其强大的功能优势,DSP已经成为世界半导体产业中,紧随微处理器和单片机之后的又一热点,并且广泛应用于通信、航天、家电、网络、工业自动化以及自动控制领域之中。

DSP与单片机都是嵌入式处理器的一种,最大区别在于DSP能够高速、实时地进行数字信号处理运算。

而单片机,也称为微处理器,主要用于中、低成本的控制领域,其位控制能力强,I/O接口种类繁多,片内外设和控制功能丰富、价格低、使用方便。

但与DSP相比,处理速度较慢。

此外,单片机没有DSP具有的高速并行结构及指令、多总线。

DSP处理的算法的复杂度和大的数据处理流量更是单片机不可企及的。

TMS320LF2407x系列DSP是专门为数字电机控制和其他控制系统设计的,该系列的芯片具有高度的集成性,因此,一片芯片即可构成一个测控系统的控制器。

该系列采用诸如自适应控制。

TMS320LF240x系列的DSP具有如下的片内外设及存储器资源:1)双8路或单16路的10位A/D转换器,转换时间为375ns,其自动排序功能使多达16次转换课在一个转换过程内完成而不会给CPU增加额外的开销;2)片内存储器:32K字闪存、2.5K字RAM,其中包含544字的双端口RAM,2K字的单端口SARAM;3)41个可独立编程的多路复用I/O引脚;4)两个事件管理器EVA、EVB,适用于控制各种类型的电机,用于工业自动化;5)串行通信接口SCI模块;6)串行外设接口SPI模块;7)带锁相环PLL的时钟模块;8)5个外部中断(复位中断、两个驱动保护中断与两个可屏蔽中断)9)CAN 2.0B模块,即控制器局域网模块;10)看门狗定时器模块;11)可扩展的192K字的空间,分别为64K字的程序存储器空间、64K字的数据存储器空间、64K字的I/O空间;12)用于仿真的JTAG接口。

DSPDSP的结构特点:○1程序和数据总线分开的哈佛结构;采用双存储,独立编码,同时处理;一条程序总线,多条数据总线,允许程序存储器和数据存储器进行数据交流;增加cache,取指令、分析指令、执行指令可以并行进行;○2多总线结构:增加了具有自动增加地址功能的辅助寄存器,可以同时传送多组数据;○3采用先进的流水线技术:并行执行指令,在单个指令周期可以完成一次乘加或者加法;○4增加了专门的硬件乘法、累加器○5设计了专门的DSP指令○6设置了DMA总线及其控制器,快速的完成数据的读取和存储;○7多种类型的存储器寻址方式○8硬件配置强,功耗低;DSP的性能指标:1.数据格式:16位的定点芯片和32位的浮点芯片;2.用途:通用型/专用型3.基础特性:○1静态芯片○2一致性芯片(指令系统和信号引脚的相互兼容)4.评价指标:○1DSP芯片运算速度○2DSP芯片运算精度○3硬件资源○4功耗DSP的技术指标:1.运算速度:○1指令周期:执行一条指令所需的时间;○2MAC时间:一次乘加的时间;○3FFT时间:运行一个N点FFT程序所需的时间;○4MIPS :每秒执行百万条指令;○5MOPS :每秒执行百万次操作;○6MFLOPS :每秒执行百万次浮点运算;○7MACS :每秒执行乘加的次数;2.硬件资源:片内外RAM、ROM、总线接口、I/O接口等;3.运算精度:字长(16、32)、累加器位数;4.功耗TI公司TMS320系列DSP:1.TMS320C2000系列(将闪存、10位的A/D、CAN接口等片内外设集在一起)○1TMS320C20X (用于电话、数字相机、嵌入式家电)○2TMS320C240X (16位的定点DSP高集成,高速度的运动控制)○3TMS320C28X (32位定点,12位的A/D,用于高性能高可靠领域)2.TMS320C5000系列(片内外设多样,封装小,用于无线电通信,因特网)○1TMS320C54X (16位定点,低功耗,小封装,各种外设集中)○2TMS320C55X (8~48位浮点,低耗,快速)3.TMS320C6000系列(内部结构不同,多功能多通道,三维图像处理)○1TMS320C62X (定点)○2TMS320C64X (定点)○3TMS320C67X (浮点)TMS320LF240X产品简介:TMS320LF240X F 具有片内闪存TMS320LC240X C 具有片内ROMTMS320LF240X具有4级流水结构和改进型的哈佛结构。