C54x DSP片内外设

- 格式:pdf

- 大小:1.11 MB

- 文档页数:28

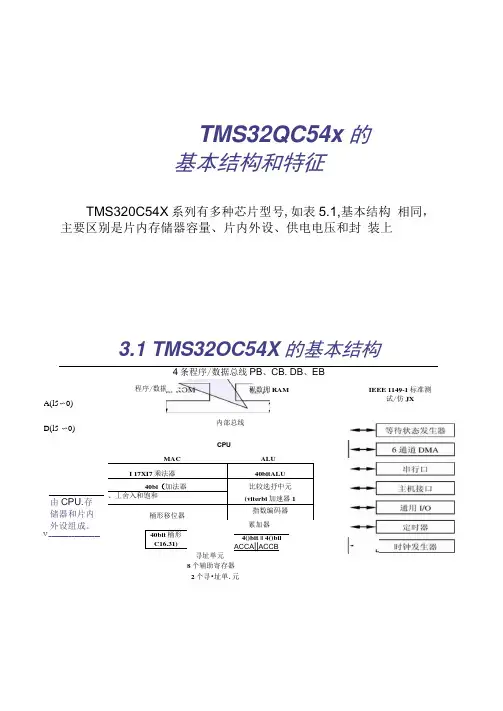

TMS32QC54x 的 基本结构和特征TMS320C54X 系列有多种芯片型号,如表5.1,基本结构 相同,主要区别是片内存储器容量、片内外设、供电电压和封 装上3.1 TMS32OC54X 的基本结构4条程序/数据总线PB 、CB. DB 、EB8个辅助寄存器 2个寻•址单.元程序/数据ROA(l5〜0) D(l5 〜0)由CPU.存 储器和片内 外设组成。

V __________________程数拥RAM内部总线I 17XI7乘法器 40bitALU 40bi (加法器比较选抒中元 、丄舍入和饱和 (viterbi 加速器1 桶形移位器 指数编码器40bit 桶形 C16.31)寻址单元 4()bit || 4()bil ACCA ||ACCBIEEE 1149-1 标准测试/仿JXCPUMACALU3.2 CPU结构TMS320C54X CPU包扌舌:40位算术逻辑运算单元ALU、40位累加器A 和B、移位-16-30位的40位柿形移位器、乘法器/加法器单元、寻址单元和状态和控制寄存器。

1、算术逻辑单元ALU使用算术逻辑单元(ALU)和两个累加器(A、B)能够完成二进制的补码运算,同时,ALU还能够完成布尔运算。

算术逻辑单元的输入操作数可以來自:• 16位的立即数;•数据存储器中的16位字;•暂存器T中的16位字;•数据存储器屮读出的2个16位字;•累加器A或B中的40位数;•移位寄存器的输出。

•即町完成双16位运算(C16=l),也町进行40位运算。

2、比较选择存储单元CSSU通信领域常常用到维持比(Viterbi)算法,该算法需要完成大量的加法/比较/选择(ACS)运算。

CSSU单元支持各种Viterbi 算法,其中加法由ALU单元完成,将ST1中的C16置1,所有的双字指令都会变成双16位算术运算指令,这样ALU就可以在一个机器周期内完成两个16位数的加/减法运算,其结果分别存放在累加器的高16位和低16位屮。

TMS320C54x系列DSP的CPU与外设——第3章存储器第3章存储器本章介绍了TMS320C54x DSP存储器的构成和操作。

⼀般来说,C54x器件共有192K 16位字的存储窨,这个空间分成3个专⽤的部分:64K字程序、64K字数据和64K字I/O⼝。

在某些C54x器件中,存储器结构已经通过重叠和分页的⽅法加以改变,这样就增加了存储器空间的容量。

C54x体系结构上的并⾏特点和⽚内RAM的双存取能⼒使C54x可以在任意给定的机器周期内同时进⾏4个存储器操作:⼀条指令的读取操作、两个操作数读操作以及⼀个操作数写操作。

在⽚内存储器中操作有如下⼏个优点:Higher performance because no wait states are requiredLower cost than external memoryLower power than external memoryThe main advantage of operating from off-chip memory is the ability to access a larger memory space.3.1 存储器空间C54x DSP的存储器划分成3种独⽴可选的空间:程序、数据和I/O。

这些空间中的RAM、ROM、EPROM、EEPROM或者存储器映射的外设可以位于⽚内或⽚外。

程序存储器中包含要执⾏的指令和执⾏指令时所需的表,数据存储器空间存储指令所需的数据,I/O存储空间连接外部的存储器映射外设,也可作外部数据存储空间。

按芯⽚各类的不同,C54x的⽚内存储器有这样⼏种类型:双存取RAM(DARAM)、单存取(SARAM)、双向共享RAM和ROM。

RAM总是映射到数据空间,但也可以映射到程序空间。

ROM可以被激活并映射到程序空间,也可部分映射到数据空间。

在CPU状态寄存器中有3位影响存储器的结构。

这3位产⽣的影响因器件不同⽽不同。