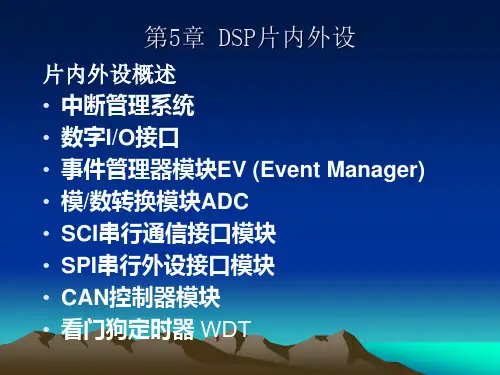

dsp片内外设

- 格式:ppt

- 大小:939.00 KB

- 文档页数:57

TI公司三大系列DSP芯片内部结构之比较班级:SJ1126 姓名:张晖学号:201120195012摘要:随着数字信号处理技术和集成电路技术的发展,以及数字系统的显著优越性,导致了DSP芯片的产生和迅速发展,DSP技术的地位凸显出来。

在世界上众多的DSP厂商中,德州仪器公司的DSP始终占据着较大的市场份额(45% ~60%),本文概略的介绍目前得到广泛应用的TI三大DSP处理器系列,TMS320C2000、TMS320C5000和TMS320C6000。

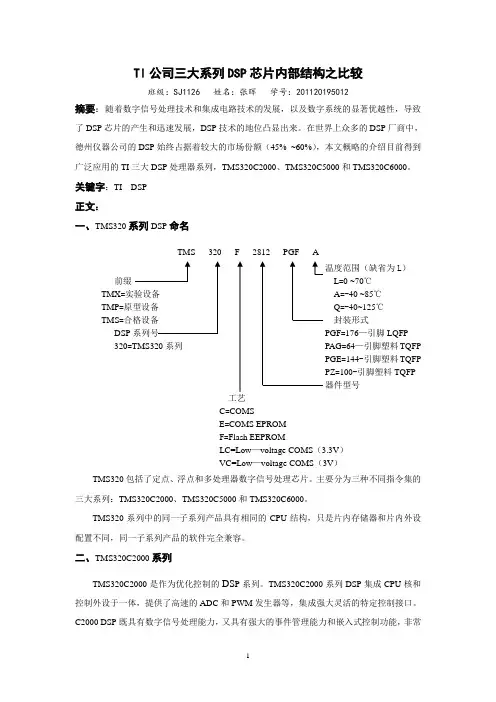

关键字:TI DSP正文:一、TMS320系列DSP命名TMS 320 F 2812 PGF A温度范围(缺省为L)前缀L=0 ~70℃TMX=A=-40 ~85℃TMP=Q=-40~125℃TMS=封装形式DSP PGF=176—引脚LQFP320=TMS320系列PAG=64—引脚塑料TQFPPGE=144-引脚塑料TQFPPZ=100-引脚塑料TQFP器件型号工艺C=COMSE=COMS EPROMF=Flash EEPROMLC=Low—voltage COMS(3.3V)VC=Low—voltage COMS(3V)TMS320包括了定点、浮点和多处理器数字信号处理芯片。

主要分为三种不同指令集的三大系列:TMS320C2000、TMS320C5000和TMS320C6000。

TMS320系列中的同一子系列产品具有相同的CPU结构,只是片内存储器和片内外设配置不同,同一子系列产品的软件完全兼容。

二、TMS320C2000系列TMS320C2000是作为优化控制的DS P系列。

TMS320C2000系列DSP集成CPU核和控制外设于一体,提供了高速的ADC和PWM发生器等,集成强大灵活的特定控制接口。

C2000 DSP既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,非常实用于工业、汽车、医疗和消费类市场中数字电机控制、数字电源和高级感应技术。

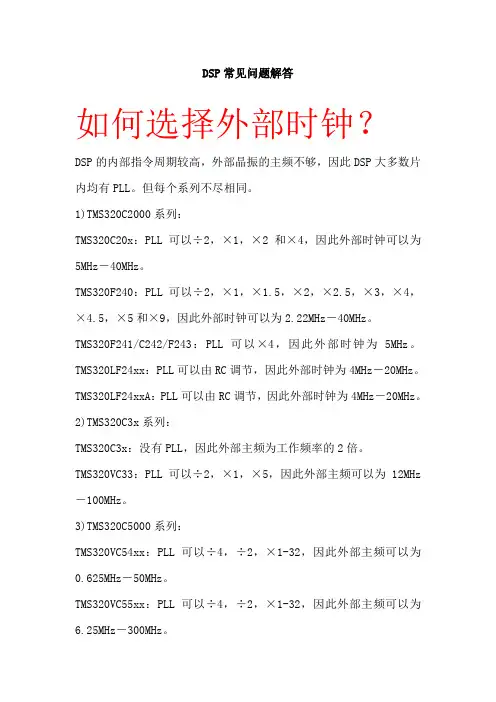

DSP常见问题解答如何选择外部时钟?DSP的内部指令周期较高,外部晶振的主频不够,因此DSP大多数片内均有PLL。

但每个系列不尽相同。

1)TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部时钟可以为5MHz-40MHz。

TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部时钟可以为2.22MHz-40MHz。

TMS320F241/C242/F243:PLL可以×4,因此外部时钟为5MHz。

TMS320LF24xx:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

TMS320LF24xxA:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

2)TMS320C3x系列:TMS320C3x:没有PLL,因此外部主频为工作频率的2倍。

TMS320VC33:PLL可以÷2,×1,×5,因此外部主频可以为12MHz -100MHz。

3)TMS320C5000系列:TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为0.625MHz-50MHz。

TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为6.25MHz-300MHz。

4)TMS320C6000系列:TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主频可以为11.8MHz-300MHz。

TMS320C67xx:PLL可以×1和×4,因此外部主频可以为12.5MHz-230MHz。

DSP原理与应用技术-考试知识点总结第一章1、DSP系统的组成:由控制处理器、DSPs、输入/输出接口、存储器、数据传输网络构成。

P2图1-1-12、TMS320系列DSPs芯片的基本特点:XXX结构、流水线操作、专用的硬件乘法器、特殊的DSP指令、快速的指令周期。

3、XXX结构:是一种将程序指令储存和数据储存分开的储存器结构。

特点:并行结构体系,是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

系统中设置了程序和数据两条总线,使数据吞吐率提高一倍。

4、TMS320系列在XXX结构之上DSPs芯片的改进:(1)允许数据存放在程序存储器中,并被算数运算指令直接使用,增强芯片灵活性(2)指令储存在高速缓冲器中,执行指令时,不需要再从存储器中读取指令,节约了一个指令周期的时间。

5、XXX结构:将指令、数据、地址存储在同一存储器中,统一编址,依靠指令计数器提供的地址来区分是指令、数据还是地址,取指令和去数据都访问同一存储器,数据吞吐率低。

6、流水线操作:TMS320F2812采用8级流水线,处理器可以并行处理2-8条指令,每条指令处于流水线的不同阶段。

解释:在4级流水线操作中。

取指令、指令译码、读操作数、执行操作可独立地处理,执行完全重叠。

在每个指令周期内,4条不同的指令都处于激活状态,每条指令处于不同的操作阶段。

7、定点DSPs芯片:定点格式工作的DSPs芯片。

浮点DSPs芯片:浮点格式工作的DSPs芯片。

(定点DSPs可以浮点运算,但是要用软件。

浮点DSPs 用硬件就可以)8、DSPs芯片的运算速度衡量标准:指令周期(执行一条指令所需时间)、MAC时间(一次乘法和加法的时间)、FFT执行时间(傅立叶运算时间)、MIPS(每秒执行百万条指令)、MOPS(每秒执行百万次操作)、MFLOPS (每秒执行百万次浮点操作)、BOPS(每秒十亿次操作)。

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

DSP的产生和发展世界上第一片DSP芯片是1978年AMI公司的S2811,1979年美国Intel公司宣布生产的商用可编程器件2920是DSP芯片的一个主要标志。

但是,这两种芯片内部都没有现代DSP芯片所必须的单周期乘法器。

1980年,日本NEC公司推出的μPD7720是第一片具有硬件乘法器的商用DSP芯片。

美国德州仪器公司(TI公司)在1982年成功推出其第一代DSP 芯片TMS32010及其系列产品。

第一个采用CMOS工艺生产浮点DSP芯片的是日本的日立(Hitachi)公司,该公司于1982年推出了浮点DSP芯片。

而第一片高性能的浮点DSP芯片是AT&T公司于1984年推出的DSP32。

飞思卡尔(Freescale)公司的前身摩托罗拉公司半导体部,1986年推出了定点处理器MC56001。

1990年推出了与IEEE浮点格式兼容的浮点DSP芯片MC96002。

到2005年,飞思卡尔公司推出了56F8300系列的定点DSP,如56F83367、56F8334等。

美国模拟器件公司(Analog Devices, 简称AD)也相继推出了一系列具有自己特点的DSP 芯片,其定点DSP 芯片有ADSP2101/2103/2105 、ASDP2111/2115 、ADSP2161/2162/2164 以及ADSP2171/2181 等。

经过30多年的不断技术创新,DSP芯片得到了突飞猛进的发展,主要表现在以下几个方面:(1) 制造工艺不断提高。

(2) 片内存储器容量不断加大。

(3) 内部结构日益完善,片内外设接口不断丰富。

(4) 处理速度不断加快。

(5) 运算精度不断提高。

(6) 开发工具更加智能化,功能也日益强大。

DSP处理器的结构和特点为了实现高速数字信号处理以及实时地进行系统控制,DSP芯片一般都采用了不同于通用CPU和MCU的特殊软硬件结构。

尽管不同公司的DSP其结构不尽相同,但是在处理器结构、指令系统等方面有许多共同点。