VHDL语言与数字集成电路设计

- 格式:ppt

- 大小:368.50 KB

- 文档页数:26

数字逻辑原理与VHDL设计课程设计一、课程设计背景数字逻辑原理与VHDL设计是数字集成电路设计专业中的一门重要基础课程,内容涵盖数字电路基础知识、组合逻辑电路设计、时序逻辑电路设计以及数字电路综合和优化等方面。

本课程设计旨在以实践为主,巩固和加深学生的理论知识,提高学生综合运用数字逻辑原理和VHDL语言进行数字电路设计的能力。

二、实验目的通过本次课程设计,要求学生对数字逻辑原理及其应用有更加深入的认识,并掌握以下专业能力:1.掌握数字逻辑电路的基本知识与方法,以及基于VHDL设计数字电路的基本步骤与方法;2.能够运用数字逻辑原理及VHDL语言进行简单数字电路的设计、仿真、综合和下载;3.能够独立进行数字电路设计并解决设计过程中遇到的问题。

三、实验设备和工具1.Xilinx Vivado软件,用于数字电路的综合和仿真;2.FPGA开发板,用于数字电路的下载和实现;3.电脑,用于Vivado软件的安装和使用。

四、实验内容和步骤实验一函数计算器的设计与实现实验目的通过设计一个函数计算器,深入理解组合逻辑电路的设计、实现和仿真过程,同时练习使用VHDL语言进行数字电路的编写、仿真和下载。

实验内容设计一个函数计算器,能够计算并显示四个前缀表达式,包括:–23 45–11 + 22 * 33–23 - 45 / 561./ 45 + 67 - 89其中,加减乘除的运算需要满足基本的优先级规则,即在没有括号的情况下,先乘除后加减。

实验步骤1.设计并编写函数计算器的VHDL代码,包括各种运算模块、数字选择器、显示器控制器等;2.在Vivado软件中进行仿真,验证函数计算器设计的正确性;3.将函数计算器设计综合成比特流文件,下载到FPGA开发板上进行实现和测试。

实验二五位计数器的设计与实现实验目的通过设计一个五位同步加法计数器,深入理解时序逻辑电路的原理、设计和实现过程,同时掌握VHDL语言对时序电路进行设计、仿真和下载的方法。

VHDL数学运算VHDL是一种硬件描述语言,可以用于实现数字电路和系统级集成电路设计。

在数字电路和系统级集成电路中,数学运算是一个非常重要的部分。

VHDL可以支持各种数学运算,包括加、减、乘和除等基本运算,以及三角函数、指数函数和对数函数等高级运算。

在VHDL中,基本的加、减、乘和除运算可以使用算术运算符实现。

例如,加法可以使用“+”运算符实现,如下所示:signal a, b, c : std_logic_vector(3 downto 0);c <= a + b;这个代码片段将a和b两个信号相加,并将结果存储在c信号中。

类似地,减法可以使用“-”运算符实现,乘法可以使用“*”运算符实现,除法可以使用“/”或“mod”运算符实现。

除此之外,VHDL还支持各种高级数学函数,例如三角函数、指数函数和对数函数等。

这些函数可以通过VHDL中提供的库函数来实现。

例如,可以使用“sin”函数来计算正弦值,如下所示:signal angle : real;signal sine : real;sine <= sin(angle);此外,VHDL还支持各种数学库函数,例如幂函数、平方根函数和绝对值函数等。

这些函数可以帮助设计人员轻松地实现各种复杂的数学运算和算法。

例如,可以使用“pow”函数来计算任意数的幂,如下所示:signal base : real;signal exponent : integer;signal result : real;result <= pow(base, exponent);总之,VHDL的数学运算功能非常强大,可以帮助设计人员轻松地实现各种数字电路和系统级集成电路的数学运算和算法。

设计人员应该熟练掌握VHDL的数学运算功能,以便能够高效地进行设计和开发工作。

VHDL与Verilog语言VHDL(VHSIC hardware description language)和Verilog是用于电子系统设计的硬件描述语言(HDL)。

这两种语言被广泛应用于数字逻辑设计和仿真,以及硬件描述、验证和综合。

1. VHDL(VHSIC hardware description language)VHDL是一种结构化的硬件描述语言,最初由美国国防部高速集成电路计划办公室(VHSIC,Very High Speed Integrated Circuits)开发。

VHDL以其强大的功能和灵活性而闻名,并被广泛用于数字系统的设计和验证。

VHDL的编写包括实体(Entity)和体(Architecture)两个主要部分。

实体部分描述了数字系统的输入输出接口、信号和组件的声明,而体部分描述了实体的内部结构、信号处理和逻辑功能。

VHDL具有丰富的数据类型、运算符和控制结构,可以方便地描述数字电路的行为和结构。

它还提供了强大的仿真和验证功能,使设计人员能够在开发和测试阶段快速迭代和调试设计。

2. VerilogVerilog是一种硬件描述语言,最初由Gateway Design Automation公司(现在是Cadence Design Systems的一部分)开发。

Verilog以其简洁的语法和易学易用的特性而受到广泛欢迎,并成为工业界标准。

Verilog的设计由模块(Module)组成,每个模块描述了一个黑盒子,包含输入和输出端口以及内部的逻辑功能。

模块可以进行层次化组合,从而实现较复杂的系统级设计。

Verilog的语法类似于C语言,具有类似的数据类型、运算符和控制结构。

它还提供了时序建模的能力,使设计人员能够描述数字电路的时序行为。

3. VHDL与Verilog的比较VHDL和Verilog在语法和功能上有一些区别,但它们都可以用于数字电路的设计和仿真。

以下是它们之间的一些比较:3.1 语法风格VHDL采用结构化的编程风格,需要明确的体、过程和信号声明,可以更好地控制和描述系统的结构和行为。

数字集成电路分析与设计深亚微米工艺第三版课程设计一、概述本文主要介绍数字集成电路分析与设计深亚微米工艺第三版课程设计。

本设计主要涉及数字集成电路设计的各个方面,包括数字逻辑设计、计算机组成原理、数字信号处理等。

本设计旨在深入探究数字电路和集成电路的设计和工艺细节,从而提高学生的专业技能和实践能力。

二、设计内容本次设计主要分为以下几个部分:1. 数字逻辑电路设计在本部分中,学生需要根据题目要求,设计数字逻辑电路的电路图和真值表,同时需要手动编写数字逻辑电路的代码,并利用VHDL语言进行编程实现。

本部分要求学生熟练掌握数字逻辑电路的设计方法和VHDL语言的编程技巧。

2. 计算机组成原理在本部分中,学生需要设计一个基于FPGA的计算机组成原理的电路图和真值表,并利用VHDL语言进行编程实现。

本部分要求学生深入理解计算机组成原理的设计思想,并熟练掌握FPGA电路设计和VHDL编程的技巧。

3. 数字信号处理在本部分中,学生需要设计一个数字信号处理的电路图和真值表,并利用Python语言进行编程实现。

本部分要求学生掌握数字信号处理的基本原理和算法,以及Python语言的编程技巧。

三、课程目标通过本次课程设计,学生应该达到以下目标:1. 掌握数字电路和集成电路的设计和工艺细节本设计涉及数字电路和集成电路的多个方面,要求学生深入理解电路设计和工艺细节,从而能够熟练掌握数字电路和集成电路的设计方法和实现流程。

2. 提高学生的专业技能和实践能力本设计要求学生进行实际的电路设计和编程实现,从而加深对数字电路和集成电路的理解和掌握。

通过实践,学生能够提高自己的专业技能和实践能力,为将来的工作打下坚实的基础。

3. 培养学生的团队合作和创新能力本设计要求学生分组进行合作,通过协作和交流,提高团队合作和创新能力。

学生需要思考如何在电路设计和编程实现中,发挥个人和团队的优势,提高工作效率。

四、总结数字集成电路分析与设计深亚微米工艺第三版课程设计,旨在提高学生的数字电路和集成电路设计能力,同时培养学生的实际操作能力和团队合作能力。

VHDL语言简介VHDL(VHSIC Hardware Description Language)即可高速集成电路硬件描述语言,是一种用于描述数字系统和电路的硬件描述语言。

它在1981年由美国国防部的高速集成电路联合委员会(VHSIC)开发,用于设计大规模集成电路。

VHDL是一种面向对象的语言,可以用于描述各种数字系统,从简单的逻辑门到复杂的处理器。

它提供了丰富的语法和语义,使得设计人员可以准确地描述他们的电路和系统。

VHDL的优势VHDL作为一种硬件描述语言,在数字系统设计中具有许多优势。

1.可重用性:VHDL允许设计人员创建可重用的模块和子系统,这些模块和子系统可以在不同的项目中重复使用,提高了设计效率和可维护性。

2.仿真和验证:VHDL具有强大的仿真和验证能力,可以在设计之前对系统进行全面的仿真和验证。

这有助于检测和纠正潜在的问题,并确保系统在硬件实现之前达到预期的功能。

3.抽象级别:VHDL允许设计人员在不同的抽象级别上描述系统,从高级的行为级别到底层的结构级别。

这使得设计人员可以根据需要在不同的级别上工作,并且可以更容易地进行系统级别的优化。

4.灵活性和可扩展性:VHDL支持灵活的设计方法和工作流程,并允许设计人员在设计过程中进行迭代和修改。

它还可以与其他常用的设计工具和方法集成,以满足特定的需求。

VHDL语言的基本结构VHDL语言由模块、实体、架构以及信号和过程等基本元素组成。

模块(Module)模块是VHDL中描述数字系统的最基本单位。

一个模块可以包含多个实体和架构,并通过连接信号进行通信。

每个模块都有一个顶层实体和一个或多个架构。

实体(Entity)实体是描述模块的接口和行为的抽象。

它定义了输入输出端口,以及模块对外部环境的接口。

一个实体可以有一个或多个架构。

架构(Architecture)架构描述模块的具体行为和内部结构。

它定义了模块的内部信号和过程,以及对外部信号和过程的接口。

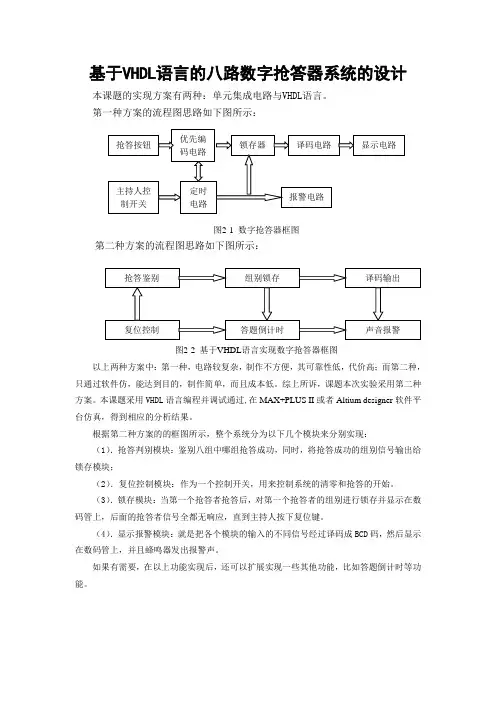

基于VHDL 语言的八路数字抢答器系统的设计 本课题的实现方案有两种:单元集成电路与VHDL 语言。

第一种方案的流程图思路如下图所示:图2-1 数字抢答器框图第二种方案的流程图思路如下图所示:图2-2 基于VHDL 语言实现数字抢答器框图 以上两种方案中:第一种,电路较复杂,制作不方便,其可靠性低,代价高;而第二种,只通过软件仿,能达到目的,制作简单,而且成本低。

综上所诉,课题本次实验采用第二种方案。

本课题采用VHDL 语言编程并调试通过,在MAX+PLUS II 或者Altium designer 软件平台仿真,得到相应的分析结果。

根据第二种方案的的框图所示,整个系统分为以下几个模块来分别实现:(1).抢答判别模块:鉴别八组中哪组抢答成功,同时,将抢答成功的组别信号输出给锁存模块;(2).复位控制模块:作为一个控制开关,用来控制系统的清零和抢答的开始。

(3).锁存模块:当第一个抢答者抢答后,对第一个抢答者的组别进行锁存并显示在数码管上,后面的抢答者信号全都无响应,直到主持人按下复位键。

(4).显示报警模块:就是把各个模块的输入的不同信号经过译码成BCD 码,然后显示在数码管上,并且蜂鸣器发出报警声。

如果有需要,在以上功能实现后,还可以扩展实现一些其他功能,比如答题倒计时等功能。

优先编码电路 抢答按钮 锁存器 译码电路 显示电路主持人控制开关 定时电路 报警电路抢答鉴别 复位控制 组别锁存 声音报警答题倒计时译码输出1 系统的设计平台概述此次设计是按照"自顶向下"的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(VHDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件。

1.1 传统和现代的数字系统设计方法比较传统的数字系统设计方法:基于电路板的设计方法,采用固定功能的器件(通用型器件),通过设计电路板来实现系统功能,在系统硬件设计的后期进行仿真和调试。

vhdl共阴极数码显示电路VHDL共阴极数码显示电路数码显示器是一种常见的电子显示设备,它能够将数字信息以可视化的方式呈现给用户。

VHDL共阴极数码显示电路是一种使用VHDL 语言设计的共阴极数码显示器电路。

本文将详细介绍VHDL共阴极数码显示电路的原理和设计过程。

共阴极数码显示器是一种常见的数码显示器类型,它由多个共阴极数码管组成。

每个共阴极数码管由7个LED灯组成,可显示0到9的数字。

共阴极数码管的工作原理是,当给定特定的电压时,相应的LED灯会点亮,形成所需的数字。

其中,共阴极表示数码管的阴极端口是连接在一起的,而阳极端口则是分别连接的。

VHDL语言是一种用于描述数字系统的硬件描述语言,它可以对数字电路进行建模和仿真。

使用VHDL语言进行设计,可以使得电路的功能更加清晰明了,并且可以方便地进行验证和修改。

在设计VHDL共阴极数码显示电路时,首先需要定义输入和输出信号。

输入信号通常包括一个4位的二进制数,用于表示要显示的数字。

输出信号是连接到共阴极数码管的引脚,用于控制数码管的亮灭。

接下来,需要编写VHDL代码来描述共阴极数码显示电路的行为。

代码主要包括两部分:数码管驱动模块和顶层模块。

数码管驱动模块是用来控制数码管显示的核心模块。

它根据输入的二进制数,将对应的数字显示在数码管上。

在这个模块中,需要定义一个包含数字对应的真值表,以便根据输入的二进制数选择对应的数字。

顶层模块是将数码管驱动模块和输入输出信号连接起来的模块。

它负责接收输入信号,将其传递给数码管驱动模块,并将输出信号连接到数码管的引脚上。

设计完成后,可以使用VHDL仿真工具对设计的电路进行验证。

通过输入不同的二进制数,观察数码管上显示的数字是否与预期相符。

如果一切正常,可以将设计的电路下载到FPGA或其他可编程逻辑器件中进行实际的硬件测试。

VHDL共阴极数码显示电路具有简单、可靠、易于实现等优点。

它在数字电子系统中得到广泛应用,例如计数器、时钟、测量仪器等。

IC,这些微小但强大的芯片,是我们电子设备的无名英雄,从我们口袋里的光滑智能无线终端,到我们桌子上的强大的截肢者,甚至我们车上最先进的汽车系统。

当它到数字集成电路时,全部是创建顶尖的系统,来传递心跳的性能,而吸电就像一个花哨的鸡尾酒,永远,永远,投球在可靠性上。

这些电路是数据处理、信号处理和控制系统的摇滚巨星,使得我们技术精湛的世界开始运转。

但是,在所有的滑翔和魅力背后,工作上有大量的脑力。

设计数字集成电路就像开始一个令人惊叹的冒险,任务包括设定舞台有规格,通过模型化将人物带入生命,在模拟中通过脚步化,通过合成来伤害它们的存在,最后通过彻底的验证确保一切的平稳航行。

就像是数字交响乐的策划者,进行电路,系统和设计技术的和谐混合,在区块上创建最高效和可靠的集成电路。

这是一个疯狂的旅程,但有人必须做到这一点!设计数字集成电路需要使用不同的工具和方法来开发和改进数字系统。

首先要弄清楚数字系统需要做什么以及它需要多好的表现我们用维利洛格和VHDL等特殊语言创建模型并测试数字系统。

接下来,我们把模型变成逻辑门列表,我们努力确保设计符合所有要求。

我们用半导体制造来制造实际的电路。

这涉及到根据设计创建布局和建造电路。

数字集成电路领域是一个不断发展和动态的研究领域,其特点是设计方法、技术和应用方面不断取得进展。

随着数字系统继续在各种电子装置和系统中发挥重要作用,对数字集成电路设计专业人才的需求日益增加。

对这一领域感兴趣的个人必须在数字电路、系统和设计原则方面奠定坚实的基础,并随时了解数字集成电路技术的最新发展。

只要具备必要的知识和技能,就能够有助于创造创新的数字集成电路,推动技术进步,提高电子系统的性能。

本文由风中思念7贡献pdf文档可能在WAP端浏览体验不佳。

建议您优先选择TXT,或下载源文件到本机查看。

一、概述VHDL与数字电路设计一、概述二、VHDL语言三、用VHDL设计逻辑电路传统数字电路设计方法 EDA设计方法 PLD器件设计流程文本设计输入—VHDL程序设计数字电子技术的基本知识回顾组合逻辑电路编码器、译码器、数据选择器、加法器、数值比较器等传统设计方法传统的设计方法是基于中小规模集成电路器件进行设计(如74系列及其改进系列、CC4000系列、 74HC系列等都属于通用型数字集成电路),而且是采用自底向上进行设计:(1)首先确定可用的元器件;(2)根据这些器件进行逻辑设计,完成各模块;(3)将各模块进行连接,最后形成系统;(4)而后经调试、测量观察整个系统是否达到规定的性能指标。

时序逻辑电路同步时序逻辑电路异步时序逻辑电路寄存器、移位寄存器、计数器、序列信号发生器 EDA设计方法EDA(Electronics Design Automation)即电子设计自动化技术,是利用计算机工作平台,从事电子系统和电路设计的一项技术。

EDA技术为电子系统设计带来了这样的变化:(1)设计效率提高,设计周期缩短;(2)设计质量提高;(3)设计成本降低;(4)能更充分地发挥设计人员的创造性;(5)设计成果的重用性大大提高,省去了不必要的重复劳动。

自顶向下的设计方法数字电路的EDA设计是基于PLD进行设计的,支持自顶向下的设计方法:(1)首先从系统设计入手,在顶层进行功能划分和结构设计;(2)然后再逐级设计底层的结构;(3)并在系统级采用仿真手段验证设计的正确性;(4)最后完成整个系统的设计,实现从设计、仿真、测试一体化。

传统设计方法 vs EDA设计方法传统设计方法自底向上手动设计软硬件分离原理图设计方式系统功能固定不易仿真难测试修改模块难移植共享设计周期长PLD器件设计流程(1)PLD开发系统包括硬件和软件两部分。

VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language,诞生于1982年。

1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。

自IEEE-1076(简称87版)之后,各EDA公司相继推出自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。

1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本,简称93版。

VHDL 和Verilog作为IEEE的工业标准硬件描述语言,得到众多EDA公司支持,在电子工程领域,已成为事实上的通用硬件描述语言。

1.vhdl是什么意思VHDL语言是一种用于电路设计的高级语言。

它在80年代的后期出现。

最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。

VHDL翻译成中文就是超高速集成电路硬件描述语言,主要是应用在数字电路的设计中。

它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。

当然在一些实力较为雄厚的单位,它也被用来设计ASIC。

VHDL主要用于描述数字系统的结构,行为,功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

2.vhdl的作用功能强大、设计灵活VHDL具有功能强大的语言结构,可以用简洁明确的源代码来描述复杂的逻辑控制。

VLSI 电路和系统设计设计题 2:CMOS数字集成电路设计用 VHDL 语言实现十六位全加器:托列吾别克·马杰尼班级:电路与系统 01 班学号: 12013/11/24基于 VHDL 的 16 位全加器的设计1.1设计题目的容及要求1.1.1目的:CMOS 数字集成电路设计流程及数字集成电路自动化设计,包括功能验证、 VHDL/Verlog建模、同步电路设计、异步数据获取、能耗与散热、信号完整性、物理设计、设计验证等技术1.1.2容:主要实验容是用0.18μm 数字 CMOS 工艺, VHDL或 Verlog 设计一个16 位全加器,用 Synthesis仿真工具验证功能,电路合成,及性能检测。

1.1.3主要测试参数及指标围:16 位的全加器主要的设计指标是高于1GHz 的频率,功耗,物理面积大小等参数。

1.2全加器的组成和原理分析全加器是常用的组合逻辑模块中的一种,对全加器的分析和对组合逻辑电路的分析一样。

组合逻辑电路的分析,就是找出给定电路输入和输出之间的逻辑关系,从而了解给定逻辑电路的逻辑功能。

组合逻辑电路的分析方法通常采用代数法,一般按下列步骤进行:(1)根据所需要的功能,列出真值表。

(2)根据真值表,写出相应的逻辑函数表达式。

(3)根据真值表或逻辑函数表达式,画出相应的组合逻辑电路的逻辑图[1]。

(4)用 VHDL 编写程序在 QUARTUSⅡ上进行模拟,并分析结果的正确性。

1.3 全加器简介全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运算就是全加运算,实现全加运算的电路称为全加器。

它主要实现加法的运算,其中分为并行全加器和串行全加器,所谓并行就是指向高位进位时是并行执行的,而串行就是从低位到高位按顺序执行,为了提高运算,必须设法减小或消除由于进位信号逐级传递所消耗的时间,为了提高运算速度,制成了超前进位加法器,这是对全加器的一种创新[2]。

1.3.1半加器的基本原理如果不考虑有来自低位的进位将两个 1 位二进制数相加,称为半加。