VHDL语言描述语句报告

- 格式:ppt

- 大小:799.00 KB

- 文档页数:38

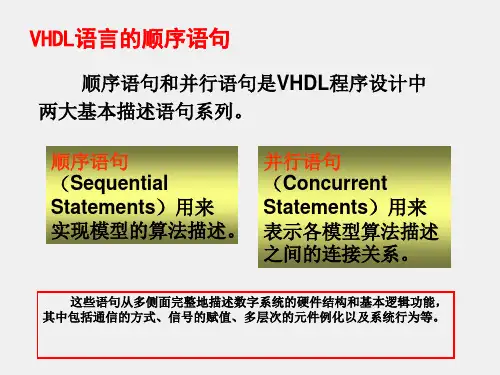

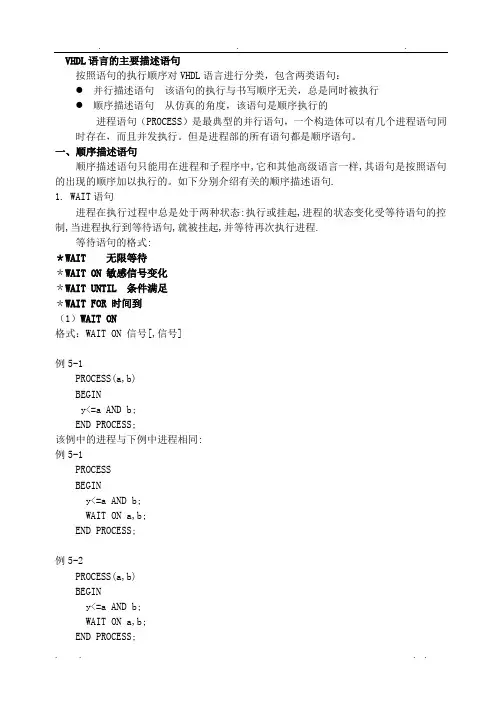

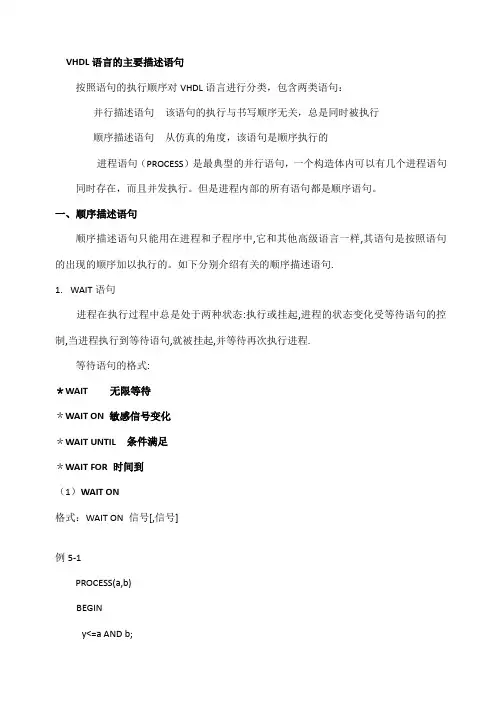

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:●并行描述语句该语句的执行与书写顺序无关,总是同时被执行●顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体可以有几个进程语句同时存在,而且并发执行。

但是进程部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR 等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

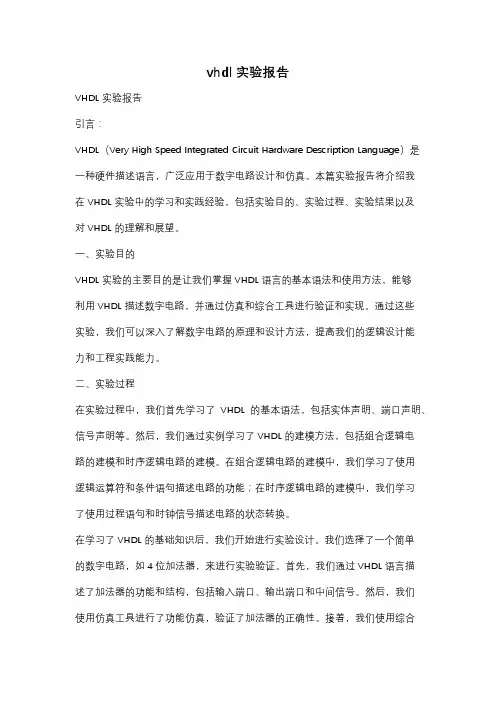

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:并行描述语句该语句的执行与书写顺序无关,总是同时被执行顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体内可以有几个进程语句同时存在,而且并发执行。

但是进程内部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

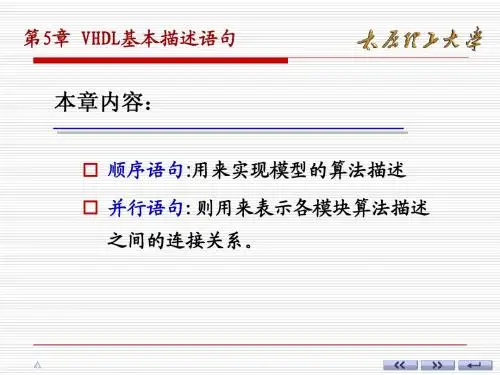

VHDL的基本描述语句有并行语句(Concurrent Statements)和顺序语句(Sequential Statements)两大类(如表8-3所示)。

在系统设计中,这些基本描述语句从不同侧面完整地描述了数字系统的硬件结构和基本逻辑功能。

表8-3VHDL的并行语句和顺序语句并行语句用于表示算法模块间的连接关系,相互之间无次序关系,它们是并行执行的,与书写顺序无关。

VHDL的结构体由若干相互联系的并行描述语句组成,如图8-3所示。

并行描述语句在结构体中的语法格式如下:ARCHITECTURE 结构体名OF 实体名IS{说明语句}BEGIN{并行语句}END ARCHITECTURE 结构体名;并行描述语句主要有:并行信号赋值语句(Concurrent Signal Assignments)、进程语句(Process Statements)、块语句(Block Statements) 、元件例化语句(Component Instantiations)、生成语句(Generate Statements) 及并行过程调用语句(Concurrent Procedure Calls)等六种。

其中,进程语句和块语句是两种最主要、最常用的并行描述语句。

本节介绍这六种并行描述语句及其功能。

一、进程语句(TOP)进程PROCESS语句本身是并行描述语句,但却包含一系列顺序描述语句。

所以,设计中各个进程是并行执行,而各进程内的顺序描述语句却是按顺序执行。

进程与其他部分的通信,是通过从进程外的信号或端口中读取或者写入值来完成。

进程语句的语法格式如下:[进程名称:]PROCESS [(敏感表)]{进程声明}BEGIN{顺序语句}END PROCESS [进程名称];其中,进程声明是对子程序、类型、常量和变量等的说明;敏感表(Sensitivity_list)是所有敏感信号(包括端口)的列表;敏感表的语法格式为:信号名称{,信号名称}所谓进程对信号敏感,是指当信号发生变化时,能够触发进程中语句的执行。