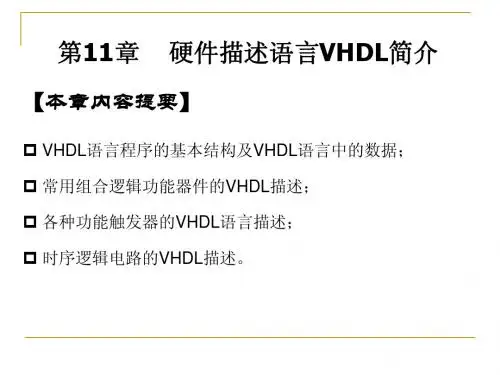

VHDL硬件描述语言基础

- 格式:ppt

- 大小:262.50 KB

- 文档页数:88

VHDL语言教程VHDL是一种硬件描述语言,用于描述数字电路和系统,并进行硬件的设计和仿真。

它被广泛应用于数字电路设计、嵌入式系统开发和可编程逻辑控制器等领域。

本教程将介绍VHDL语言的基本概念和语法,帮助您了解和学习这门强大的硬件描述语言。

一、VHDL概述VHDL是Very High Speed Integrated Circuit Hardware Description Language的缩写,意为高速集成电路硬件描述语言。

它是一种硬件描述语言,用于描述数字电路和系统。

与传统的电路设计方法相比,使用VHDL可以更加方便、高效地进行电路设计和测试。

1.VHDL的起源和发展VHDL最早由美国国防部为了解决数字电路设计复杂、效率低下的问题而研发。

后来,VHDL成为了一种IEEE标准(IEEE1076)并被广泛应用于数字电路设计和仿真。

2.VHDL的优点VHDL具有以下几个优点:-高级抽象:VHDL提供了一种高级描述电路的方法,使得设计者能够更加方便地表达复杂的电路结构和行为。

-可重用性:VHDL支持模块化设计,使得设计者可以将电路的不同部分进行抽象和封装,提高了电路的可重用性。

-高效仿真:VHDL可以进行高效的电路仿真和测试,有助于验证电路设计的正确性和可靠性。

-灵活性:VHDL可以应用于各种不同类型和规模的电路设计,从小规模的数字逻辑电路到大规模的系统级设计。

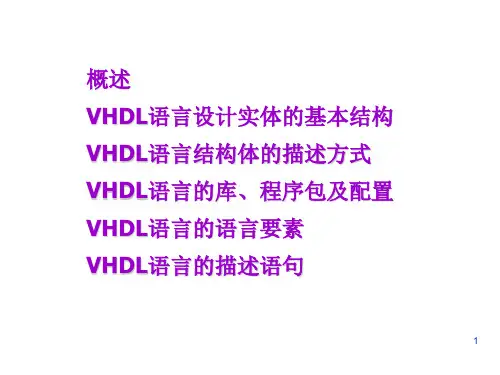

二、VHDL语法和基本概念1.VHDL的结构VHDL程序由程序单元(unit)组成,程序单元是VHDL描述的最小单元。

程序单元包括实体(entity)、结构(architecture)、过程(process)和包(package)等。

2. 实体(entity)实体是VHDL描述电路模块的一个部分,包括输入输出端口、信号声明和实体标识符等。

3. 结构(architecture)结构描述了实体的具体电路结构和行为,包括组件声明、信号赋值和行为描述等。

VHDL入门教程VHDL(Very High-Speed Integrated Circuit HardwareDescription Language)是一种硬件描述语言,用于设计数字电路和系统。

它是由美国国防部在20世纪80年代早期开发的,并由IEEE 1076标准化。

VHDL可以用于描述电路结构、电路行为和模拟。

一、VHDL概述VHDL是一种硬件描述语言,它允许工程师以更高级的语言编写硬件描述。

它可以描述电路结构、电路行为和模拟。

VHDL可以应用于各种电子系统的设计,从简单的数字逻辑门到复杂的处理器。

二、VHDL基本结构VHDL的基本结构包括实体声明、体声明和结构化代码。

实体声明描述了电路的接口,包括输入和输出。

主体声明描述了电路的行为。

结构化代码定义了电路的结构。

三、VHDL数据类型VHDL提供了多种数据类型,包括标量类型(比如整数和实数)、数组类型和记录类型。

每种类型都有其特定的操作和范围。

四、VHDL信号VHDL中的信号用于在电路中传递信息。

信号可以在过程中赋值,并且具有各种延迟属性。

信号还可以连接到模块的输入和输出端口,以实现电路之间的通信。

五、VHDL实体和体VHDL设计包含实体和体。

实体描述了电路的接口和连接,而体描述了电路的行为。

实体和体之间使用端口来传递信息。

六、VHDL组件VHDL中的组件用于将电路模块化,以实现更高层次的设计和复用。

组件可以在实体中声明,并在体中实例化。

七、VHDL并发语句VHDL中的并发语句用于描述电路中多个同时运行的过程。

并发语句包括并行语句、过程、并行块和并行时钟。

八、VHDL测试VHDL测试包括自动测试和手动测试。

自动测试使用测试工具和仿真器来验证电路的正确性。

手动测试包括使用仿真器进行手工测试和调试。

九、VHDL实例以下是一个简单的VHDL实例,实现了一个4位二进制加法器:```vhdllibrary IEEE;use IEEE.STD_LOGIC_1164.all;entity binary_adder isporta : in std_logic_vector(3 downto 0);b : in std_logic_vector(3 downto 0);sum : out std_logic_vector(4 downto 0);carry : out std_logicend binary_adder;architecture behavior of binary_adder isbeginprocess(a, b)variable temp_sum : std_logic_vector(4 downto 0);variable temp_carry : std_logic;begintemp_sum := ("0000" & a) + ("0000" & b);temp_carry := '0' when temp_sum(4) = '0' else '1';sum <= temp_sum;carry <= temp_carry;end process;end behavior;```上述VHDL代码定义了一个名为`binary_adder`的实体,它有两个4位输入`a`和`b`,一个5位输出`sum`和一个单一位输出`carry`。

VHDL与硬件描述语言VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,被广泛应用于数字电路和系统的设计、仿真和验证中。

本文将介绍VHDL的基本概念、语法和应用,以及其在硬件设计中的重要性和优势。

一、VHDL的基本概念与语法VHDL是由美国国防部下属的VHSIC(Very High Speed Integrated Circuits)计划发起的硬件描述语言标准化工作中发展起来的,它源于Ada语言,并在此基础上进行了修改和扩展。

VHDL采用了面向对象的设计思想,通过描述硬件的结构和行为,实现了对数字系统的高层次抽象。

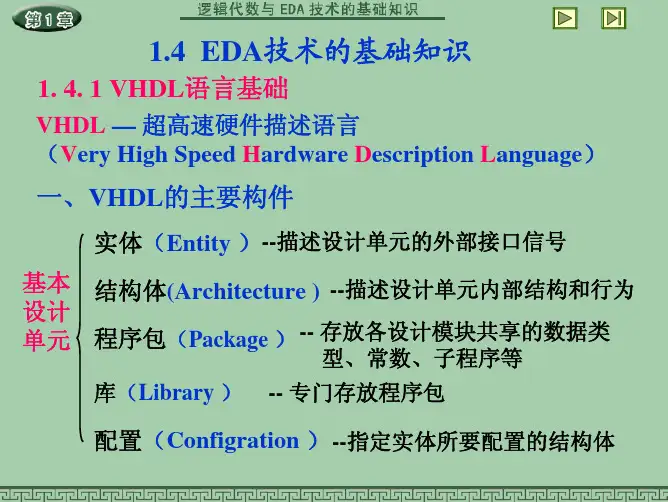

VHDL的基本元素包括实体(entity)、结构(architecture)和配置(configuration)。

实体定义了模块的接口和信号,结构描述了模块内部的组织和连接关系,配置用于将不同实体和结构进行绑定。

此外,VHDL还提供了丰富的数据类型、控制结构和函数库,以支持复杂的逻辑运算和算术操作。

VHDL代码的编写需要遵循一定的语法规则,如正确使用关键字、语句结束符号等。

此外,注释和缩进等规范的使用可以提高代码的可读性和可维护性。

二、VHDL的应用1. 数字电路设计VHDL在数字电路设计中被广泛应用,通过使用VHDL语言,设计人员可以描述和验证各种数字逻辑电路,包括组合逻辑电路和时序逻辑电路。

借助VHDL仿真工具,可以进行功能仿真、时序仿真和行为仿真,验证设计的正确性和性能。

2. 系统级设计除了用于电路级设计,VHDL还可以用于系统级设计。

通过对模块的整合和功能描述,可以搭建更为复杂的系统,并在此基础上进行仿真和验证。

VHDL支持高级抽象和层次化设计,使得系统级设计更加灵活和可重用。

3. ASIC和FPGA设计VHDL在应用特定的集成电路(ASIC)和现场可编程门阵列(FPGA)的设计中,具有非常重要的地位。

ASIC是在集成电路制造厂中进行定制化设计和生产的芯片,而FPGA则是可以在现场进行编程和配置的可重构芯片。

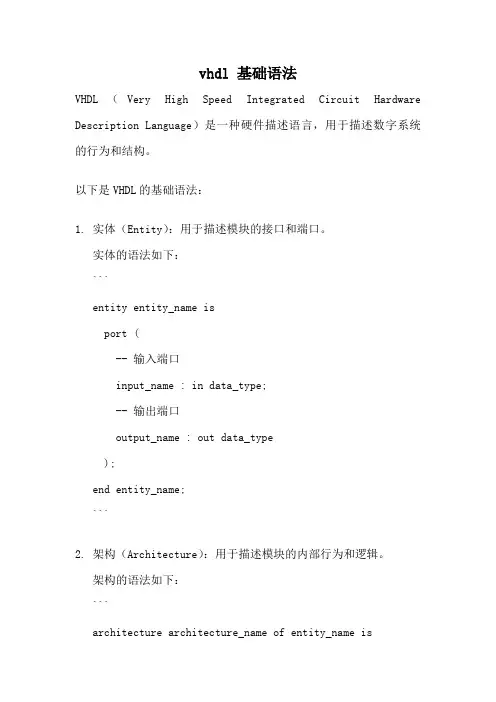

vhdl 基础语法VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字系统的行为和结构。

以下是VHDL的基础语法:1. 实体(Entity):用于描述模块的接口和端口。

实体的语法如下:```entity entity_name isport (-- 输入端口input_name : in data_type;-- 输出端口output_name : out data_type);end entity_name;```2. 架构(Architecture):用于描述模块的内部行为和逻辑。

架构的语法如下:```architecture architecture_name of entity_name issignal signal_name : data_type;begin-- 逻辑实现end architecture_name;```3. 信号(Signal):用于在模块内部传递数据。

信号的语法如下:```signal signal_name : data_type;```4. 过程(Process):用于描述模块的并发行为。

过程的语法如下:```process (sensitivity_list)begin-- 逻辑实现end process;```5. 语句(Statement):用于描述模块的具体操作。

常见的语句包括:- 赋值语句:```signal_name <= value;```- 选择语句:```case expression iswhen value1 =>-- 逻辑实现1when value2 =>-- 逻辑实现2when others =>-- 默认逻辑实现end case;```- 循环语句:```for i in range loop-- 逻辑实现end loop;```这些是VHDL的基础语法,可以用于描述数字系统的行为和结构。

VHDL语言入门教程VHDL是一种硬件描述语言,主要用于设计数字电路和系统。

它是由美国国防部门于1980年代初开发的,目的是为了改进电子设计自动化(EDA)工具的开发效率和设计文档的可重复性。

VHDL广泛应用于数字信号处理(DSP)、嵌入式系统、通信系统和各种ASIC(专用集成电路)和FPGA(现场可编程门阵列)的设计。

本教程将介绍VHDL的基础知识,包括语法、数据类型和常见的建模技术。

一、VHDL的语法VHDL的语法由标识符、关键字、运算符和分隔符组成。

其中,标识符用于给变量、信号和实体命名,关键字用于定义语言特定的操作,运算符用于数学和逻辑运算,分隔符用于分隔语句。

VHDL中的代码以一个实体(entity)的声明开始,然后是体(architecture)的声明,最后是信号声明和进程(process)的描述。

以下是一个简单的例子:```vhdlentity AND_gate isportA, B: in std_logic;C: out std_logicend entity AND_gate;architecture Behavior of AND_gate isbeginC <= A and B;end architecture Behavior;```在这个例子中,我们声明了一个名为AND_gate的实体,它有两个输入信号A和B,一个输出信号C。

然后我们定义了一个名为Behavior的体,它描述了AND门的行为:C等于A与B的逻辑与运算结果。

二、VHDL的数据类型VHDL支持许多数据类型,包括标量类型、数据类型、自定义类型和引用类型。

标量类型包括bit、bit_vector、integer、real、std_logic和std_ulogic等。

其中,bit_vector是一组连续的位,std_logic和std_ulogic用于表示单个信号。

数据类型是由标量类型和数组类型组成的。

数组类型可以是一维、二维或更高维的,用于存储多个数据。