第四章 VHDL语言构造体的描述

- 格式:ppt

- 大小:979.00 KB

- 文档页数:69

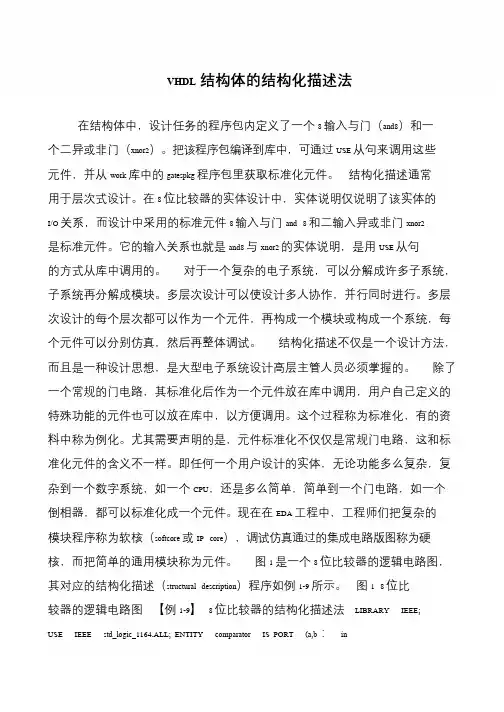

VHDL结构体的结构化描述法在结构体中,设计任务的程序包内定义了一个8 输入与门(and8)和一个二异或非门(xnor2)。

把该程序包编译到库中,可通过USE 从句来调用这些元件,并从work 库中的gatespkg 程序包里获取标准化元件。

结构化描述通常用于层次式设计。

在8 位比较器的实体设计中,实体说明仅说明了该实体的I/O 关系,而设计中采用的标准元件8 输入与门and 8 和二输入异或非门xnor2 是标准元件。

它的输入关系也就是and8 与xnor2 的实体说明,是用USE 从句的方式从库中调用的。

对于一个复杂的电子系统,可以分解成许多子系统,子系统再分解成模块。

多层次设计可以使设计多人协作,并行同时进行。

多层次设计的每个层次都可以作为一个元件,再构成一个模块或构成一个系统,每个元件可以分别仿真,然后再整体调试。

结构化描述不仅是一个设计方法,而且是一种设计思想,是大型电子系统设计高层主管人员必须掌握的。

除了一个常规的门电路,其标准化后作为一个元件放在库中调用,用户自己定义的特殊功能的元件也可以放在库中,以方便调用。

这个过程称为标准化,有的资料中称为例化。

尤其需要声明的是,元件标准化不仅仅是常规门电路,这和标准化元件的含义不一样。

即任何一个用户设计的实体,无论功能多么复杂,复杂到一个数字系统,如一个CPU,还是多么简单,简单到一个门电路,如一个倒相器,都可以标准化成一个元件。

现在在EDA 工程中,工程师们把复杂的模块程序称为软核(softcore 或IP core),调试仿真通过的集成电路版图称为硬核,而把简单的通用模块称为元件。

图1 是一个8 位比较器的逻辑电路图,其对应的结构化描述(structural description)程序如例1-9 所示。

图1 8 位比较器的逻辑电路图【例1-9】8 位比较器的结构化描述法LIBRARY IEEE; USE IEEE std_logic_1164.ALL; ENTITY comparator IS PORT(a,b:in。

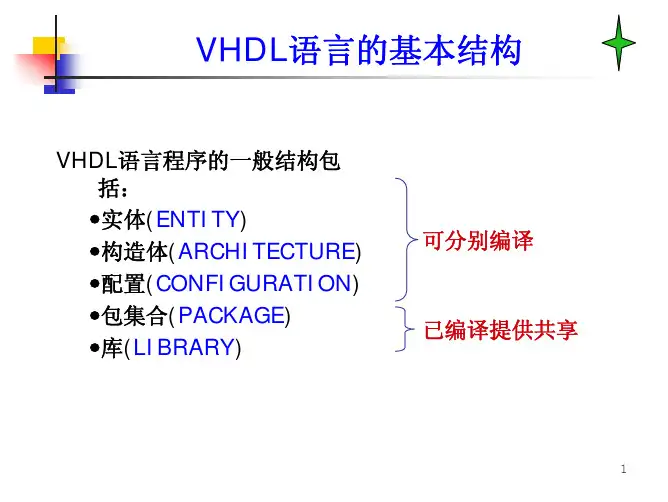

简述VHDL的基本结构及每部分的基本功能。

1.1. 简述VHDL的基本结构及每部分的基本功能。

(1)库库是经编译后的数据集合,库中存放的是各种程序包、实体定义、结构体描述等。

设计人员在用VHDL 语言设计系统时,库中内容有的可作为标准,有的可作为资源被引用。

库的作用就在于使设计者可以共享已经编译过的设计文件及有用数据。

(2)程序包程序包是VHDL程序的公共存储区,在程序包内说明的数据对实体是透明的。

程序包由程序包说明和程序包体组成。

(3)实体实体可以表示小到一个与门,也可以大到一个数字系统,这个系统可以像微处理器一样的复杂。

在实体的说明部分主要完成设计对象的输入输出端口名称、传输方向、数据类型的定义,即端口的定义。

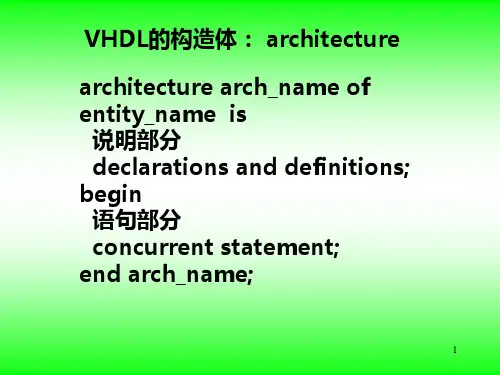

(4)结构体结构体是设计实体的具体描述,如果把设计实体抽象为一个功能方块图,结构体则描述这个功能方块图内部的具体逻辑实现细节。

一个设计实体的内部实现细节通过结构体的具体描述表现出来。

(5)配置配置是用于描述设计不同层次之间的关系和实体与结构体之间的连接关系。

在实体与结构体之间的连接关系配置说明中,设计者可以利用配置语句为实体提供不同的结构体与之相匹配。

在仿真设计中,可以利用不同配置方式选择不同结构体,分别对不同结构体进行仿真测试。

2. 简述VHDL语言实体申明中:IN、OUT、BUFFER和INOUT 等端口模式各自的特点。

IN:输入型,只读模式。

OUT:输出型,只写。

BUFFER:缓冲型,带有读功能的输出模式,即输出并向内部反馈,out相似,但可读。

INOUT:输入输出型,可读可写,可以通过该端口读入或写出信息。

3. 在VHDL语言中,标识符必须遵循一些规则,有哪些规则?(1)标示符的第一个字母必须是英文字母。

(2)标示符的最后一个字母不能使下划线字符。

(3)标示符不允许连续出现两个下划线字符。

(4)标示符不区分字母的大小写。

(5)VHDL的保留字不能用于作为标示符使用。

4. VHDL的数据对象有哪几种,它们之间有什么不同?答:VHDL的数据对象包括信号、常量、变量和文件4类。

VHDL语言构造体的描述方式4.1 构造体的行为描述方式4.2 构造体的寄存器传输描述方式4.3 构造体的结构描述方式4.1 构造体的行为描述方式●可并行信号赋值是VHDL的特点。

●简单与门(AND)模块如下:ENTITY and2 ISPORT (a,b,:IN BIT;c: OUT BIT);END and2;ARCHITECTURE and2_behav OF and2 ISBEGINc<= a AND b AFTER 5 ns;END and2_behav;2.延时语句●惯性延时*用于系统或器件的惯性描述;*语句:a < = b after 5 ns ;说明可以缺省;*惯性延时说明在仿真时有意义,综合时忽略●传输延时*用于总线、连接线或芯片中路径的延时;*语句:B < = transport A after 5 ns ;说明不可缺省;3.多驱动器描述语语句(略)4.GENERIC 语句●用于不同层次之间的信息传送例如,在数据说明中用于位矢量长度、数组长度、器件延时等参数的传递。

例:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ascount isgeneric(countsize:integer :=3);port(clk,areset,enable: in std_logic;count: buffer std_logic_vector(countsize-1 downto 0)); end ascount;4.2 构造体的寄存器传输描述方式1.描述方式的特点●寄存器描述方法:与硬件一一对应的描述或寄存器之间的功能描述(p56-57)●VHDL语言的限制2.描述方式应注意的问题●"X"状态传递●寄存器RTL描述的限制:*在一个进程中不能有多于一个寄存器的描述*IF语句中不能有ELSE●关联性强的信号应放在一个进程中4.3 构造体的结构描述方式●多层次设计,高层次设计调用低层次设计模块1.COMPONENT 语句●元件说明COMPONENT 元件名[GENERIC(类属说明)][PORT(端口说明)]END COMPONENT;●可以在结构体、包集合和BLOCK的说明中使用●例1:component AND2port(I1,I2 : in BIT;Z: out BIT);end component;●例2:component ADDgeneric(N:POSITIVE);port(X,Y : in BIT_VECTOR(N-1 downto 0);z : out BIT_VECTOR(N-1 downto 0);CARRY: out BIT);end component;元件例化语句*将现成元件的端口信号映射成高层次设计电路中的信号;*格式:例化名:元件名[generic map (类属名=>表达式{,类属名=>表达式})]port map ([端口信号名=>]信号{,[端口信号名=> ]信号})*类属映射为可选项,类属名与元件说明语句中的相同,每个表达式要计算出一个值。