FPGA第三天实验——有限状态机

- 格式:pdf

- 大小:834.14 KB

- 文档页数:7

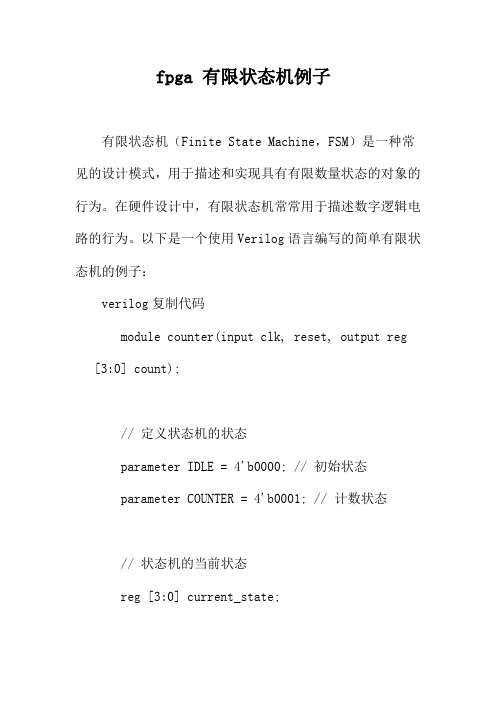

fpga 有限状态机例子有限状态机(Finite State Machine,FSM)是一种常见的设计模式,用于描述和实现具有有限数量状态的对象的行为。

在硬件设计中,有限状态机常常用于描述数字逻辑电路的行为。

以下是一个使用Verilog语言编写的简单有限状态机的例子:verilog复制代码module counter(input clk, reset, output reg [3:0] count);// 定义状态机的状态parameter IDLE = 4'b0000; // 初始状态parameter COUNTER = 4'b0001; // 计数状态// 状态机的当前状态reg [3:0] current_state;// 状态转移逻辑always @(posedge clk or posedge reset) begin if (reset) begincurrent_state <= IDLE; // 如果reset信号为高,则进入IDLE状态end else begincase (current_state)IDLE: beginif (count == 4'b1000) current_state <= COUNTE R; // 如果计数达到8,则进入COUNTER状态endCOUNTER: begincurrent_state <= IDLE; // 在COUNTER状态下,计数完成后回到IDLE状态enddefault: begincurrent_state <= IDLE; // 如果状态机处于未知状态,则强制回到IDLE状态endendcaseendend// 计数逻辑always @(posedge clk) beginif (current_state == COUNTER) count <= count + 1; // 在COUNTER状态下,计数器递增endendmodule在这个例子中,我们定义了一个简单的4位计数器。

集成电路实验状态机设计实验报告专业:电子信息工程姓名:江燕婷学号:2011301200025状态机设计(实验五)实验报告一.实验目的1. 掌握状态机设计的基本方法2.学习利用状态机的方法实现控制电路二.实验原理有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。

有限状态机非常适合用FPGA器件实现,用Verilog HDL的case语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。

有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。

根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。

摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。

米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。

图1-1 摩尔型状态机图1-2 米里型状态机状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。

状态机的状态实现上,可采用符号编码或显式数字编码。

编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。

顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。

三. 实验设备与软件平台微型计算机,GW48-CK,QuartusII v5.0。

南京理工大学泰州科技学院FPGA系统设计实验报告教材名称:FPGA系统设计与应用开发指导教师:周莉莉实验室:4401学院(系):电子电气工程学院专业班级:10电信(1)班姓名:周根生朱守超学号:1002040149 1002040150实验学期:2013-2014学年第一学期总评成绩:教师签字:南京理工大学泰州科技学院FPGA系统设计实验报告目录实验一Max+plusII原理图设计输入 (1)实验二简单逻辑电路设计与仿真 (6)实验三组合逻辑电路设计(一) (11)实验四组合逻辑电路设计(二) (16)实验五有限状态机的设计 (26)实验六数字频率计 (32)南京理工大学泰州科技学院FPGA系统设计实验报告课程: FPGA系统设计班级:10电信1班姓名:周根生朱守超学号:10020401491002040150指导教师:周莉莉实验日期:实验题目:Max+plusII原理图设计输入成绩:一、设计任务采用原理图设计输入法,设计一个具有四舍五入功能的电路,其输入为4位二进制数,要求输入大于或等于0101时,电路输出为高电平,小于0101时电路输出为低电平。

二、设计过程根据设计要求列出四舍五入的真值表,如图1.1所示。

图1.1 四舍五入真值表由图1.1可得化简的表达式为OUT=A+BD+BC,由逻辑表达式可知,要设计的电路图有四个输入端(A,B,C,D)和一个输出端OUT,整个电路由两个2输入端的与门和一个3输入的或门组成。

启动MAX+plusII,新建Graphic Editor file文件,后缀为.gdf。

在编辑界面空白处双击左键,出现输入元件对话框如图1.2所示,在Symbol Name栏中直接输入元件的符号名OK,输入端(input),输出端(output),连接电路如图1.3所示。

图1.2 操作图1.3 原理图芯片型号选择单击Assign,选择Device,如图1.4所示。

图1.4 型号引脚命名双击PIN_NAME,使其变黑后输入引脚名,并保存文件然后编译,如图1.5所示。

Verilog学习----有限状态机的设计的⼀般步骤有限状态机的设计的⼀般步骤:(1)逻辑抽象,得出状态转换图。

就是把给出的⼀个实际逻辑关系表⽰为时序逻辑函数,可以⽤状态转换表来描述,也可以⽤状态转换图来描述。

这就需要:1)分析给定的逻辑问题,确定输⼊变量、输出变量以及电路的状态数。

通常是取原因(或条件)作为输⼊变量,取结果作为输出变量。

2)定义输⼊、输出逻辑状态的含意,并将电路状态顺序编号。

3)按照要求列出电路的状态转化表或画出状态图。

这样,就把给定的逻辑问题抽象到⼀个时序逻辑函数了。

(2)状态简化。

如果在状态转换图中出现这样两个状态,它们在相同的的输⼊下转换到同⼀状态去,并得到⼀样的输出,则称为等价状态。

显然等价状态是重复的,可以合并为⼀个。

电路的状态数越少,存储电路也就越简单。

状态化简的⽬的就在于将等价状态尽可能地合并,以得到最简状态图。

(3)状态分配。

状态分配⼜称状态编码。

通常有很多编码⽅法,编码⽅案选择得当,设计的电路可以简单,反之,选择的不好,则设计的电路就会复杂的多。

在实际设计中,须综合考虑电路的复杂度与电路性能之间的折衷。

在触发器资源丰富的FPGA设计中,采⽤独热码既可以使电路性能得到保障⼜可以充分利⽤其触发器数量多的优势,也可以采⽤输出编码的状态指定来简化电路结构,并提⾼状态机的运⾏速度。

(4)选定触发器的类型并求出状态⽅程、驱动⽅程和输出⽅程。

(5)按照⽅程得出逻辑图。

⽤Verilog来描述有限状态机,可以充分发挥硬件描述语⾔的抽象建模能⼒,使⽤always块语句和case(if)等条件语句及赋值语句即可⽅便实现。

实验五有限状态机一、实验目的:本次实验通过Verilog 硬件语言编写摩尔型有限状态机和米勒型有限状态机,掌握采用有限状态机产生各种控制信号的原理,熟悉如何选用合适的有限状态机进行电路设计,通过实验进一步了解原理图编辑方法和仿真方法。

二、实验要求:1、利用Verilog 硬件语言,参考提供的源程序,设计一个采用摩尔型有限状态机实现的流水灯控制程序;2、利用Verilog 硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的串行口发送程序;3、利用Verilog 硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的串行口接收程序;4、利用原理图编辑方法,将串行口发送和接收模块进行连接,实现完整的串行通信电路,并对该电路进行仿真。

摩尔型有限状态机实现的流水灯源程序module sled(clk,led);input clk;output [7:0] led;reg [7:0] led;reg[2:0] state;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100,s5=3'b101,s6=3'b110,s7=3'b111;always @(posedge clk)case(state)s0: begin state<=s1; led<=8'b00000001; end s1: begin state<=s2; led<=8'b00000010; end s2: begin state<=s3; led<=8'b00000100; end s3: begin state<=s4; led<=8'b00001000; end s4: begin state<=s5; led<=8'b00010000; end s5: begin state<=s6; led<=8'b00100000; end s6: begin state<=s7; led<=8'b01000000; end s7: begin state<=s0; led<=8'b10000000; end endcaseendmodule米勒型有限状态机实现的串行口发送源程序module s_tx(clk,en,dain,txd);input clk,en;input[7:0] dain;output txd;reg [7:0] da_temp;reg txd;reg [3:0] state;parameter swait=4'b0000,star=4'b0001,s1=4'b0010,s2=4'b0011,s3=4'b0100,s4=4'b0101,s5=4'b0110,s6=4'b0111,s7=4'b1000,s8=4'b1001,stop=4'b1010;always @(posedge en)da_temp<=dain;always @(posedge clk)if (!en) beginstate<=swait;txd<=1;endelsecase(state)swait: begin state<=star;txd<=1; endstar: begin state<=s1; txd<=0; ends1: begin state<=s2; txd<=da_temp[7]; ends2: begin state<=s3; txd<=da_temp[6]; ends3: begin state<=s4; txd<=da_temp[5]; ends4: begin state<=s5; txd<=da_temp[4]; ends5: begin state<=s6; txd<=da_temp[3]; ends6: begin state<=s7; txd<=da_temp[2]; ends7: begin state<=s8; txd<=da_temp[1]; ends8: begin state<=stop; txd<=da_temp[0]; endstop: begin state<=stop; txd<=1; endendcaseendmodule米勒型有限状态机实现的串行口接收源程序module s_rx(clk,dain,daout);input clk,dain;output [7:0] daout;reg [7:0] daout;reg [7:0] da_temp;reg [3:0] state;parameter star=4'b0000,s1=4'b0010,s2=4'b0011,s3=4'b0100,s4=4'b0101,s5=4'b0110,s6=4'b0111,s7=4'b1000,s8=4'b1001,stop=4'b1010;always @(negedge clk)case (state)star: if (dain)state<=star;elsestate<=s1;s1:begin state<=s2; da_temp[7]<=dain; ends2:begin state<=s3; da_temp[6]<=dain; ends3:begin state<=s4; da_temp[5]<=dain; ends4:begin state<=s5; da_temp[4]<=dain; ends5:begin state<=s6; da_temp[3]<=dain; ends6:begin state<=s7; da_temp[2]<=dain; ends7:begin state<=s8; da_temp[1]<=dain; ends8:begin state<=stop;da_temp[0]<=dain; end stop:if (!dain)state<=stop;elsebeginstate<=star;daout<=da_temp;endendcaseendmodule串行口通信系统原理图电路。

实验项目名称:有限状态机指导教师:实验日期:实验概述:【实验目的及实验设备】实验目的:(1)掌握有限状态机的应用方法。

(2)掌握有限状态机的静态测试方法,能够进行程序设计。

(3)学习测试模块的编写,综合和不同层次的仿真。

(4)用有限状态机设计一个自动售货机(饮料价格为2.5元)。

实验设备及仪器名称:CPU型号:英特尔*****************************操作系统类型:Windows XP SP3仿真软件:MAX Plus 2软件、Modelsim SE-64 10.0c实验内容及步骤:【实验原理及电路图】系统能够根据用户输入的硬币,判断钱币是否足够,当所投硬币达到或者超过购买者所选面值时,则根据顾客的要求自动售货,并找回剩余的硬币,然后回到初始状态,当所投硬币面值不够时,则给出提示,并通过一个复位键退回所投硬币。

然后回到初始状态。

该实验输入有4个clk,reset,表示投一元币y,表示投五角币w。

输出有2个,表示饮料出现的out和找五角钱的w_out.该实验共5个状态,s0:表示投币为0的状态,s1:表示投入5角的,s2:表示投入1元,s3:表示投入1.5元,s4:表示投入2元。

当投入2.5时out输出1,状态回到s0,当投入3元时out 和w_out都输出1,状态回到s0.【实验方案】(实验步骤,记录)1、打开Modelsim SE-64 10.0c软件。

else beginout=0;w_out=0;s=s4;endendcaseendendmodule测试程序:module shou;wire y;reg w;reg reset;reg clk;paramerer clkperiod=100;shouhuoji shou(y,w,reset,clk)initial beginw=0;clk=0;reset=1;#150 reset=0;#100 reset=1;endalways#(clkperiod/2) clk=~clk;always#(clkperiod+30) $random;initial $monitor(Stime, “y=%b”,y);endmodule3、编译并调试程序,出现错误立即修改直至无错误出现。

一.状态机1.实验内容:输入序列识别状态机:检测序列中是否连续出现四个或者四个以上的1或0,当满足以上情况时,输出变为1,当输入数据改变时,输出变为0。

2.实验目的:设计状态机,熟悉FPGA工具的使用,进行硬件功能仿真。

3.设计要求:输入:时钟KEY0,复位SW0,输入数据w输出:输出z LEDG0,输出显示:LEDR8-LEDR0。

4.设计方案设计采用9个状态的状态机,分别为IDLE,S1—出现一个0,S2出现两个0,S3出现3个0,S4出现4个0,K1—出现一个1,K2出现两个1,K3出现3个1,K4出现4个1一共9个状态。

时钟上升沿跳变,同步复位reset高电平有效,上电复位后状态state为IDLE。

5.验证方案验证主要侧重于在连续输入4个或4个以上0或1时,输出能否正确输出1,而在状态转换过程中程序是否如同设计时所预想的进行。

变化输入值,观察输出值。

`timescale `timescale 1ns/100psmodule tb_fsm;reg clk;reg reset,w;wire[8:0] outled;wire z;wire [2:0] state,NEXT_state;fsm dut(.clk(clk),.reset(reset),.w(w),.outled(outled),.z(z));initial beginclk=0;endalways #5 clk=~clk;initial beginreset=0;w=0;#4 reset=1;#3 reset=0;#12 w=0;// @(posedge clk)#12 w=0;#12 w=0;#13 w=0;#12 w=0;#12 w=0;#13 w=1;#200 $finish;Endendmodule6.仿真结果下面是通过ModelSim的仿真波形二.LPM参数化模块1.实验内容及目的实验内容:片内RAM块实验目的:使用LPM参数化模块库,片上RAM块显式例化与自动推导2.设计要求分别用模块库,生成宽度为8,深度为32位的RAM块。

《FPGA系统设计》实验报告》有限状态机的设计一、设计任务了解有限状态机的概念;掌握Moore型有限状态机的特点和其VHDL语言的描述方法掌握Mealy型有限状态机的特点和其VHDL语言的描述方法二、设计过程1.单进程Moore型有限状态机程序代码这是一个单进程的Moore状态机, 其特点是组合进程和时序进程在同一个进程中, 此进程可以认为是一个混合进程。

2.该状态机时一个2进程Mealy型状态机, 进程COMREG是时序与组合混合型进程;进程COM1负责根据状态和输入信号给出不同的输出信号。

library ieee;use ieee.std_logic_1164.all;entity MEALY1 isport(clk,datain,reset : in std_logic;q : out std_logic_vector(4 downto 0));end MEALY1;architecture one of MEALY1 istype states is (st0,st1,st2,st3,st4);signal stx : states;begincomreg : process(clk,reset,datain,stx) --主控时序进程beginif reset = '1' then stx <= st0;elsif clk'event and clk = '1' thencase stx iswhen st0 => if datain = '1' then stx <= st1;end if;when st1 => if datain = '0' then stx <= st2;end if;when st2 => if datain = '1' then stx <= st3;end if;when st3 => if datain = '0' then stx <= st4;end if;when st4 => if datain = '1' then stx <= st0;end if;when others => stx <= st0;end case;end if;end process comreg;com1 : process(stx,datain) --主控组合进程begincase stx iswhen st0 => if datain = '1' then q <= "10000"; else q <= "01010"; end if;when st1 => if datain = '0' then q <= "10111"; else q <= "10100"; end if;when st2 => if datain = '1' then q <= "10101"; else q <= "10011"; end if;when st3 => if datain = '0' then q <= "11011"; else q <= "01001"; end if;when st4 => if datain = '1' then q <= "11101"; else q <= "01101"; end if;when others => q <= "00000";end case;end process com1;end one;3.该状态机属于Moore型状态机, 由两个主控进程构成, 其中进程REG是主控时序进程, COM是主控组合进程。

试验一有限状态机的综合,采用Gray码

夏宇闻教材P171

//这是有限状态机的第一次实验,一共有四个版本

module fsm (clock,reset,a,k2,k1,state);

input clock,reset,a;

output k2,k1;

output[1:0] state;

reg k2,k1;

reg[1:0] state;

parameter

Idle = 2`b00,

Start = 2'b01,

Stop = 2`b10,

Clear = 2`b11;

always @(posedge clock)

if(!reset)

begin

state <= Idle;

k2 <= 0;

k1 <= 0;

end

else

case (state)

Idle:

if(a)

begin

state <= Start;

k1 <= 0;

end

else

begin

state <= Idle;

k2 <= 0;

k1 <= 0;

end

Start:

if(! a)

state <= Stop;

else

state <= Start;

Stop:

if(a)

begin

state <= Clear;

k2 <= 1;

end

else

begin

state <= Stop;

k2 <= 0;

k1 <= 0;

end

Clear:

if (! a)

begin

state <= Idle;

k2 <= 0;

k1 <= 1;

end

else

begin

state <= Clear;

k2 <= 0;

k1 <= 1;

end

default: state <= 2'bxx;

endcase

endmodule

RTL图:

此程序不能生成状态机时序图。

试验二有限状态机的综合,采用独热码

//只是在参数这里吧Gary码改为了独热码,其它与上述程序相同

parameter

Idle = 2`b1000,

Start = 2'b0100,

Stop = 2`b0010,

Clear = 2`b0001;

一般的编码方式有:二进制码,独热码,格雷码

编写状态机的时候应尽量使用独热码编码

此程序不能生成状态机时序图。

试验三有限状态机,用输出指定的码表示

状态

module fsm (clock,reset,a,k2,k1,state);

input clock,reset,a;

output k2,k1;

output[4:0] state;

reg[4:0] state;

assign k2 = state[4];

assign K1 = state[0];

parameter

Idle = 5`b00000,

Start = 5'b00010,

Stop = 5`b00100,

StopToClear = 5`b11000,

Clear = 5`b01010,

ClearToIdle = 5`b00111;

always @(posedge clock)

if(!reset)

begin

state <= Idle;

end

else

case (state)

Idle:

if(a)

state <= Start;

else

state <= Idle;

Start:

if(! a)

state <= Stop;

else

state <= Start;

Stop:

if(a)

state <= StopToClear;

else

state <= Stop;

StopToClear:

state <= Clear;

Clear:

if (! a)

state <= ClearToIdle;

else

state <= Clear;

ClearToIdle:

state <= Idle;

default: state <= Idle;

endcase

endmodule

此程序不能生成状态机时序图。

适合于高速电路使用。

试验四有限状态机,实现了RTL图输出和MODELSIM的时序仿真

module fsm (clock,reset,a,k2,k1);

input clock,reset,a;

output k2,k1;

reg k1,k2;

reg[1:0] state,nextstate;

parameter

Idle = 2`b00,

Start = 2'b01,

Stop = 2`b10,

Clear = 2`b11;

//----------------每个时钟沿产生一次状态变化————————————————

always @(posedge clock)

if(!reset)

state <= Idle;

else

state <= nextstate;

//---------------产生下一个状态的组合逻辑-------------------- always @( state or a )

case (state)

Idle:

if(a)

nextstate <= Start;

else

nextstate <= Idle;

Start:

if(! a)

nextstate <= Stop;

else

nextstate <= Start;

Stop:

if(a)

nextstate <= Clear;

else

nextstate <= Stop;

Clear:

if (! a)

nextstate <= Idle;

else

nextstate <= Clear;

default: nextstate <= 2`bxx;

endcase

//---------产生K1路的组合逻辑输出-----------

always @( state or reset or a)

if (! reset)

k1 = 0;

else

if (state == Clear && !a)

k1 = 1;

else k1 = 0;

//-----产生输出K2的组合逻辑--------------------

always @(state or reset or a)

if (! reset )

k2 = 0;

else

if (state == Stop && !a)

k2 = 1;

else k2 = 0;

endmodule

RTL图:。