有限状态机设计

- 格式:doc

- 大小:468.50 KB

- 文档页数:6

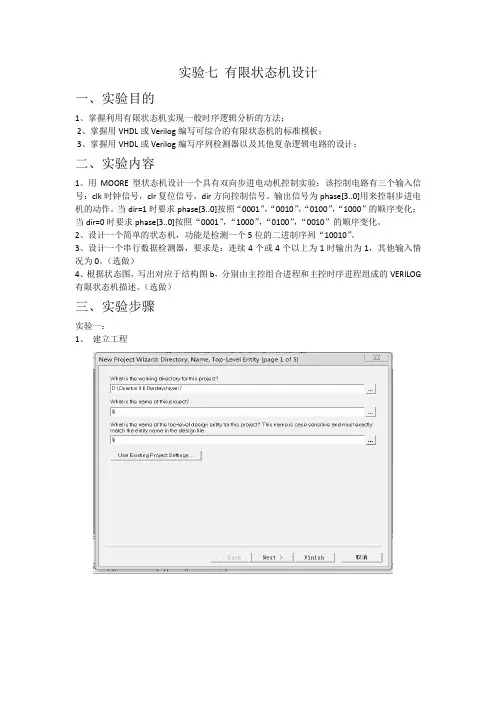

实验七有限状态机设计一、实验目的1、掌握利用有限状态机实现一般时序逻辑分析的方法;2、掌握用VHDL或Verilog编写可综合的有限状态机的标准模板;3、掌握用VHDL或Verilog编写序列检测器以及其他复杂逻辑电路的设计;二、实验内容1、用MOORE型状态机设计一个具有双向步进电动机控制实验:该控制电路有三个输入信号:clk时钟信号,clr复位信号,dir方向控制信号。

输出信号为phase[3..0]用来控制步进电机的动作。

当dir=1时要求phase[3..0]按照“0001”,“0010”,“0100”,“1000”的顺序变化;当dir=0时要求phase[3..0]按照“0001”,“1000”,“0100”,“0010”的顺序变化。

2、设计一个简单的状态机,功能是检测一个5位的二进制序列“10010”。

3、设计一个串行数据检测器,要求是:连续4个或4个以上为1时输出为1,其他输入情况为0。

(选做)4、根据状态图,写出对应于结构图b,分别由主控组合进程和主控时序进程组成的VERILOG 有限状态机描述。

(选做)三、实验步骤实验一:1、建立工程2、创建Verilog HDL文件3、输入程序代码并保存module moore1(clk,clr,dir,phase);input clk,clr,dir;output[3:0] phase;reg[3:0] phase;reg[1:0] state;parameter s0='b00,s1='b01,s2='b10,s3='b11;always@(posedge clk)beginif(clr)beginphase<='b0000;state<=s0;endelsebegincase(state)s0:if(dir) beginphase<='b0010;state<=s1;endelsebeginphase<='b1000;state<=s3;ends1:if(dir) beginphase<='b0100;state<=s2;endelse beginphase<='b0001;state<=s0;ends2:if(dir) beginphase<='b1000;state<=s3;endelse beginphase<='b0010;state<=s1;ends3:if(dir) beginphase<='b0001;state<=s0;endelse beginphase<='b0100;state<=s2;endendcaseendendendmodule4、进行综合编译5、新建波形文件6、导入引脚,设置信号源并保存7、功能仿真,结果分析由仿真波形图可以看出当dir=1时,phase[3..0]按照0001,0010,0100,1000的顺序变化,当dir=0时phase[3..0]按照0001,1000,0100,0010的顺序变化。

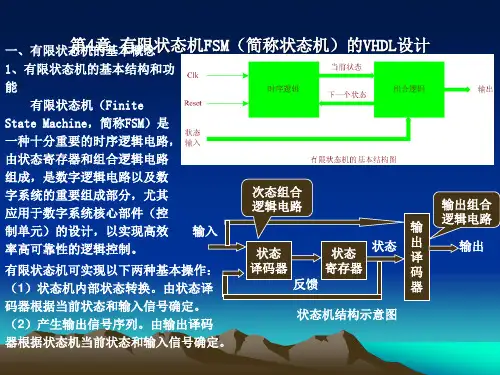

集成电路实验状态机设计实验报告专业:电子信息工程姓名:江燕婷学号:2011301200025状态机设计(实验五)实验报告一.实验目的1. 掌握状态机设计的基本方法2.学习利用状态机的方法实现控制电路二.实验原理有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。

有限状态机非常适合用FPGA器件实现,用Verilog HDL的case语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。

有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。

根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。

摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。

米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。

图1-1 摩尔型状态机图1-2 米里型状态机状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。

状态机的状态实现上,可采用符号编码或显式数字编码。

编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。

顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。

三. 实验设备与软件平台微型计算机,GW48-CK,QuartusII v5.0。

基于有限状态机的工控系统软件设计 (1)通过分析工控系统的特性,提出采用状态机的思想进行工控软件设计。

详细论述了高速状态机的错步问题以及控制层中状态机的状态划分问题。

结合具体的应用实例,给出了基于状态机的实现方法。

实验表明,采用状态机的设计方法有助于准确描述受控对象的行为,软件的健壮性和可靠性得到显著提高。

1. 引言1.1 工控软件的一般问题工控软件设计可分为基于控制环和基于实时操作系统两大类。

控制环是把各个功能模块连接成首尾相接的环状结构。

其特点为任何一个功能模块都不能出现死循环,甚至循环次数太多的循环语句都应避免出现。

以保证能够在实时意义上尽可能快地遍历各功能模块,从而满足实时多任务的需求。

在各功能模块中一般用状态机来描述模块所处的状态。

而实时操作系统则可以通过一套底层机制根据优先级和各任务状态调度各功能模块。

此时各功能模块就以“任务”作为表现形式。

但是在每个任务内部仍然为一个独立的控制环结构,仍然需要用状态机描述。

本文将结合工程实践论述状态机在工控中的应用,给出通用模型和注意要点。

1.2 有限状态机有限状态机是一种重要的思想方法。

从数学的角度看,它实际是一个五元组M = (I, O, S, δ,λ),其中I,O分别表示输入输出,S为状态向量,δ为次态方程(δ: S×I ->S),表示输出方程(λ: S×I -> O)。

有限状态机从结构体系上有层级状态机,并发状态机等。

层级状态机类似于软件中的子程序调度:更高层的一个状态对应于较低层的一个状态机。

这个高层的状态处于底层状态机的某个状态中。

这个低层状态称为子状态。

与子程序调用受到系统堆栈深度制约不一样,层级状态机可以由开发者根据控制对象的层次性运动规律任意指定深度。

与子程序的目的一样,层级状态机也是为了提高控制软件的模块化程度,降低状态分析的复杂度。

并发状态机偏重于描述状态机的调度。

状态机本身不能实现什么并发功能,并发的实现是通过软件调度的。

双蒸米酒是一种传统的中国白酒工艺,主要流行于四川、贵州、湖南等地。

下面是双蒸米酒的工艺流程:

1. 原料选择:双蒸米酒的原料主要是高粱、小麦和糯米。

这些原料经过清洗和浸泡后,进行蒸煮,使其成为发酵的基础物质。

2. 发酵:将蒸煮好的原料放入发酵缸中,加入酒曲(酒曲是一种含有酵母和发酵细菌的混合物),开始进行发酵。

发酵的时间一般为7-10天,发酵后的原料被称为酒糟。

3. 蒸馏:将酒糟放入蒸馏锅中进行蒸馏。

蒸馏锅分为上下两层,上层用来蒸馏原料,下层用来接收蒸馏后的酒。

这种双层蒸馏的工艺被称为“双蒸”,这也是双蒸米酒得名的原因。

4. 陈酿:经过蒸馏后的酒液被收集起来,放入陶罐或橡木桶中进行陈酿。

陈酿的时间一般为数月至数年不等,这个过程中酒液会逐渐变得更加醇厚。

5. 调配:经过陈酿后的酒液会进行调配,以确保口感和香气的均衡和稳定。

总的来说,双蒸米酒工艺注重原料的选择和发酵、蒸馏、陈酿等环节的精细操作,以生产出口感醇厚、香气独特的白酒。

这种工艺历史悠久,传统工艺的传承和创新是双蒸米酒得以保持独特风格的关键。

《FPGA系统设计》实验报告》有限状态机的设计一、设计任务a)了解有限状态机的概念;b)掌握Moore型有限状态机的特点和其VHDL语言的描述方法;c)掌握Mealy型有限状态机的特点和其VHDL语言的描述方法。

二、设计过程实验原理在数字电路系统中,有限状态机是一种重要的时序逻辑电路模块。

它对数字系统的设计具有十分重要的作用。

例如:全自动洗衣机,浸泡、洗涤、排水、脱水,流程状态无需手动操作,只要条件满足就自动进入下一工作个状态,并且工作流程可以灵活设定。

这种控制功能完全可用有限状态机来实现。

有限状态机( Finite State Machine, FSM)也是一种时序逻辑电路。

状态机从输出方式出发,可以分为Moore型和Mealy型;从状态机结构出发,可以分为单进程状态机和多进程状态机。

我们知道,任何数字系统都可以分为相互作用的控制单元(control unit)和数据通道(data path)两部分。

数据通道通常由组合逻辑构成,而控制单元通常由时序逻辑构成,任何时序电路都可以表示为有限状态机(Finite State Machine,FSM)。

在基本时序逻辑电路建模的基础上,本实验主要介绍有限状态机实现复杂时序逻辑电路的设计。

数字系统控制部分的每一个部分都可以看作一种状态,与每一控制相关的转换条件指定了状态的下一个状态和输出。

根据有限状态机的输出与当前状态和当前输入的关系,可以将有限状态机分成Moore 型有限状态机和Mealy型有限状态机两种。

从现实的角度,这两种状态机都可以实现同样的功能,但是它们的时序不同,选择使用哪种有限状态机要根据实际情况进行具体分析。

1.单进程Moore型有限状态机程序码图6.1 引脚分配图图6.2 Moore型实验箱现象2.该状态机时一个2进程Mealy型状态机,进程COMREG是时序与组合混合型进程;进程COM1负责根据状态和输入信号给出不同的输出信号。

图6.3 引脚分配图图6.4 Mealy型实验箱现象3.该状态机属于Moore型状态机,由两个主控进程构成,其中进程REG 是主控时序进程,COM是主控组合进程。

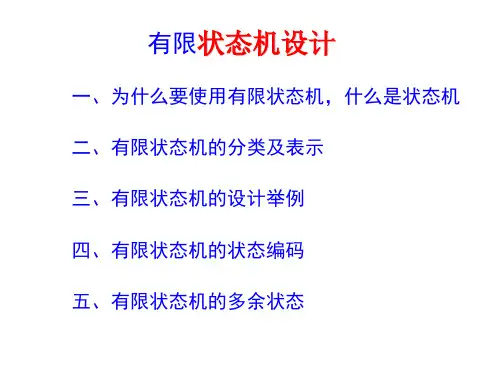

有限状态机设计

实验报告

一.实验题目

有机状态机设计

二.实验目的

掌握有机状态机设计的基本方法。

三.实验远离

状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。

有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。

四.实验内容

实验内容一:

状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。

有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。

根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。

Moore型电路中,输出信号仅仅取决于存储电路的状态。

Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。

图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。

假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。

图1 Mealy状态机

下面的程序中使用两个进程来描述该状态机。

第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。

请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态转移图和RTL原理图。

…

实验内容二:

论文《基于VHDL的一个简单Mealy状态机》中(见附件:基于VHDL的一个简单Mealy状态机.pdf)设计了一个Mealy状态机用来检测数据流“1101010”,用以验证状态机在数据检测上的应用。

请在读懂文中程序的基础上,在Quartus Ⅱ软件中通过编译、仿真得

到状态图和波形图,对该状态机的功能进行验证。

五.实验数据

1.实验一编译图

2.实验一状态转移图

3.实验二编译图

4.实验二状态转移图

5.实验二波形验证图。