有限状态机设计

- 格式:docx

- 大小:363.76 KB

- 文档页数:15

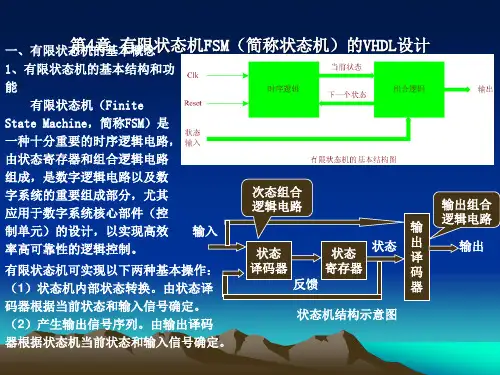

Verilog学习----有限状态机的设计的⼀般步骤有限状态机的设计的⼀般步骤:(1)逻辑抽象,得出状态转换图。

就是把给出的⼀个实际逻辑关系表⽰为时序逻辑函数,可以⽤状态转换表来描述,也可以⽤状态转换图来描述。

这就需要:1)分析给定的逻辑问题,确定输⼊变量、输出变量以及电路的状态数。

通常是取原因(或条件)作为输⼊变量,取结果作为输出变量。

2)定义输⼊、输出逻辑状态的含意,并将电路状态顺序编号。

3)按照要求列出电路的状态转化表或画出状态图。

这样,就把给定的逻辑问题抽象到⼀个时序逻辑函数了。

(2)状态简化。

如果在状态转换图中出现这样两个状态,它们在相同的的输⼊下转换到同⼀状态去,并得到⼀样的输出,则称为等价状态。

显然等价状态是重复的,可以合并为⼀个。

电路的状态数越少,存储电路也就越简单。

状态化简的⽬的就在于将等价状态尽可能地合并,以得到最简状态图。

(3)状态分配。

状态分配⼜称状态编码。

通常有很多编码⽅法,编码⽅案选择得当,设计的电路可以简单,反之,选择的不好,则设计的电路就会复杂的多。

在实际设计中,须综合考虑电路的复杂度与电路性能之间的折衷。

在触发器资源丰富的FPGA设计中,采⽤独热码既可以使电路性能得到保障⼜可以充分利⽤其触发器数量多的优势,也可以采⽤输出编码的状态指定来简化电路结构,并提⾼状态机的运⾏速度。

(4)选定触发器的类型并求出状态⽅程、驱动⽅程和输出⽅程。

(5)按照⽅程得出逻辑图。

⽤Verilog来描述有限状态机,可以充分发挥硬件描述语⾔的抽象建模能⼒,使⽤always块语句和case(if)等条件语句及赋值语句即可⽅便实现。

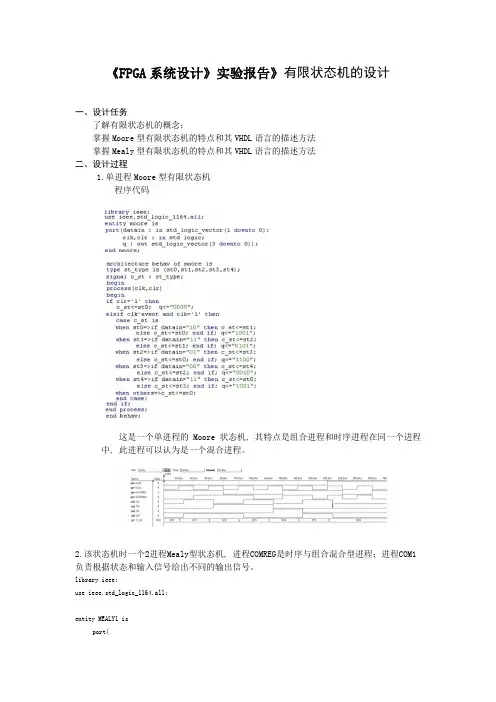

《FPGA系统设计》实验报告》有限状态机的设计一、设计任务了解有限状态机的概念;掌握Moore型有限状态机的特点和其VHDL语言的描述方法掌握Mealy型有限状态机的特点和其VHDL语言的描述方法二、设计过程1.单进程Moore型有限状态机程序代码这是一个单进程的Moore状态机, 其特点是组合进程和时序进程在同一个进程中, 此进程可以认为是一个混合进程。

2.该状态机时一个2进程Mealy型状态机, 进程COMREG是时序与组合混合型进程;进程COM1负责根据状态和输入信号给出不同的输出信号。

library ieee;use ieee.std_logic_1164.all;entity MEALY1 isport(clk,datain,reset : in std_logic;q : out std_logic_vector(4 downto 0));end MEALY1;architecture one of MEALY1 istype states is (st0,st1,st2,st3,st4);signal stx : states;begincomreg : process(clk,reset,datain,stx) --主控时序进程beginif reset = '1' then stx <= st0;elsif clk'event and clk = '1' thencase stx iswhen st0 => if datain = '1' then stx <= st1;end if;when st1 => if datain = '0' then stx <= st2;end if;when st2 => if datain = '1' then stx <= st3;end if;when st3 => if datain = '0' then stx <= st4;end if;when st4 => if datain = '1' then stx <= st0;end if;when others => stx <= st0;end case;end if;end process comreg;com1 : process(stx,datain) --主控组合进程begincase stx iswhen st0 => if datain = '1' then q <= "10000"; else q <= "01010"; end if;when st1 => if datain = '0' then q <= "10111"; else q <= "10100"; end if;when st2 => if datain = '1' then q <= "10101"; else q <= "10011"; end if;when st3 => if datain = '0' then q <= "11011"; else q <= "01001"; end if;when st4 => if datain = '1' then q <= "11101"; else q <= "01101"; end if;when others => q <= "00000";end case;end process com1;end one;3.该状态机属于Moore型状态机, 由两个主控进程构成, 其中进程REG是主控时序进程, COM是主控组合进程。

有限状态机设计与化简

在设计和实现有限状态机时,我们经常遇到的一个问题是状态机可能会变得复杂和冗长,导致难以管理和维护。

因此,我们需要一个方法来对有限状态机进行化简,以简化设计和提高可读性。

1.确定状态集合:首先,我们需要明确系统中可能的所有状态。

这些状态应该能够完整地描述系统的行为和状态。

2.确定输入符号集合:然后,我们需要确定能够影响状态转移的所有输入符号。

3.确定输出符号集合:接下来,我们需要确定状态机可以产生的所有输出符号。

4.确定转移函数:转移函数定义了从一个状态到另一个状态的转移条件。

我们需要根据系统要求确定转移函数的具体形式和条件。

5.绘制状态转移图:借助状态转移图,我们可以直观地表示状态之间的转移关系。

图中的节点表示状态,边表示状态之间的转移,边上的标记表示触发该转移的输入符号。

6.确定等价状态:等价状态是指在任何输入序列下,状态机的行为是相同的。

我们可以使用不同的方法(如等价关系、状态等价识别算法等)来确定等价状态。

7.合并等价状态:一旦我们确定了等价状态,我们可以将它们合并成一个新的等价状态。

通过合并等价状态,我们可以显著减少状态机的复杂性和冗余。

8.重绘状态转移图:最后,我们需要使用新的等价状态更新状态转移图。

新的状态转移图应该更简洁和易读,同时保留了原始状态机的行为。

通过以上步骤,我们可以对有限状态机进行设计和化简,从而简化复杂的状态机,并提高其可读性和可维护性。

这对于开发和设计各种自动控制系统、软件系统和电路系统等具有重要意义。

实验七有限状态机设计

一、实验目的

1、掌握利用有限状态机实现一般时序逻辑分析的方法;

2、掌握用VHDL或Verilog编写可综合的有限状态机的标准模板;

3、掌握用VHDL或Verilog编写序列检测器以及其他复杂逻辑电路的设计;

二、实验内容

1、用MOORE型状态机设计一个具有双向步进电动机控制实验:该控制电路有三个输入信号:clk时钟信号,clr复位信号,dir方向控制信号。

输出信号为phase[3..0]用来控制步进电机的动作。

当dir=1时要求phase[3..0]按照“0001”,“0010”,“0100”,“1000”的顺序变化;当dir=0时要求phase[3..0]按照“0001”,“1000”,“0100”,“0010”的顺序变化。

2、设计一个简单的状态机,功能是检测一个5位的二进制序列“10010”。

3、设计一个串行数据检测器,要求是:连续4个或4个以上为1时输出为1,其他输入情况为0。

(选做)

4、根据状态图,写出对应于结构图b,分别由主控组合进程和主控时序进程组成的VERILOG 有限状态机描述。

(选做)

三、实验步骤

实验一:

1、建立工程

2、创建Verilog HDL文件

3、输入程序代码并保存

module moore1(clk,clr,dir,phase);

input clk,clr,dir;

output[3:0] phase;

reg[3:0] phase;

reg[1:0] state;

parameter s0='b00,s1='b01,s2='b10,s3='b11;

always@(posedge clk)

begin

if(clr)begin

phase<='b0000;state<=s0;end

else

begin

case(state)

s0:if(dir) begin

phase<='b0010;state<=s1;end

else

begin

phase<='b1000;state<=s3;end

s1:if(dir) begin

phase<='b0100;state<=s2;end

else begin

phase<='b0001;state<=s0;end

s2:if(dir) begin

phase<='b1000;state<=s3;end

else begin

phase<='b0010;state<=s1;end

s3:if(dir) begin

phase<='b0001;state<=s0;end

else begin

phase<='b0100;state<=s2;end

endcase

end

end

endmodule

4、进行综合编译

5、新建波形文件

6、导入引脚,设置信号源并保存

7、功能仿真,结果分析

由仿真波形图可以看出当dir=1时,phase[3..0]按照0001,0010,0100,1000的顺序变化,当dir=0时phase[3..0]按照0001,1000,0100,0010的顺序变化。

所以设计正确。

实验二:

1、建立工程

2、创建Verilog HDL文件

3、输入程序代码并保存

module seqdet(x,z,clk,rst,state);

input x,clk,rst;

output z;

output [2:0] state;

reg [2:0] state;

wire z;

parameter IDLE='d0,A='d1,B='d2,C='d3,D='d4,E='d5,F='d6,G='d7;

assign z=(state==E&&x==0)?1:0;

always @(posedge clk)

if(!rst)

begin

state<=IDLE;

end

else

casex(state)

IDLE:if(x==1)

begin

state<=A;

end

A:if(x==0)

begin

state<=B;

end

B:if(x==0)

begin

state<=C;

end

else

begin

state<=F;

end

C:if(x==1)

begin

state<=D;

end

else

begin

state<=G;

end

D:if(x==0)

begin

state<=E;

end

else

begin

state<=A;

end

E:if(x==0)

begin

state<=C;

end

else

begin

state<=A;

end

F:if(x==1)

begin

state<=A;

end

else

begin

state<=B;

end

G:if(x==1)

begin

state<=F;

end

default:state<=IDLE; endcase

endmodule

//测试代码

`timescale 1ns/1ns module seqdet_Top;

reg clk,rst;

reg [23:0]data;

wire [2:0]state;

wire z,x;

assign x=data[23];

always #10 clk=~clk; always @(posedge clk) data={data[22:0],data[30]}; initial

begin

clk=0;

rst=1;

#2 rst=0;

#30 rst=1;

data='b1100_1001_0000_1001_0100;

#500 $stop; end

seqdet m(x,z,clk,rst,state);

endmodule

4、进行综合编译

5、新建波形文件

6、导入引脚

7、设置信号源并保存

8、功能仿真

9、仿真结果分析

由波形图可以看出状态由000->001->010->011->100,即对应IDLE->A->B->C->D->E的状态转换即10010.所以设计正确。

实验三:

1、建立工程

2、创建Verilog HDL文件

3、输入程序代码并保存

module jiance_ljj(clk,clr,a,out);

input clk,clr,a;

output out;

reg out;

reg[2:0] t;

always@(posedge clk or posedge clr)

begin

if (clr)

begin

t<=0;

out<=0;

end

else

begin

case(t)

'b000:begin

if(a)

t<='b001;

else

t<='b000;

out<=0;

end

'b001:begin

if(a)

t<='b010;

else

t<='b000;

out<=0;

end

'b010:begin

if(a)

t<='b011;

else

t<='b000;

out<=0;

end

'b011:begin

if(a)

t<='b100;

else

t<='b000;

out<=0;

end

'b100:begin

t<='b000;

if(a)

out<=1;

else

out<=0;

end

endcase

end

end

endmodule

4、进行综合编译

5、新建波形文件

6、导入引脚

7、设置信号源并保存

8、生成网表

9、仿真结果分析

由仿真波形可知结果正确。