有限状态机(FSM)的设计

- 格式:doc

- 大小:50.00 KB

- 文档页数:5

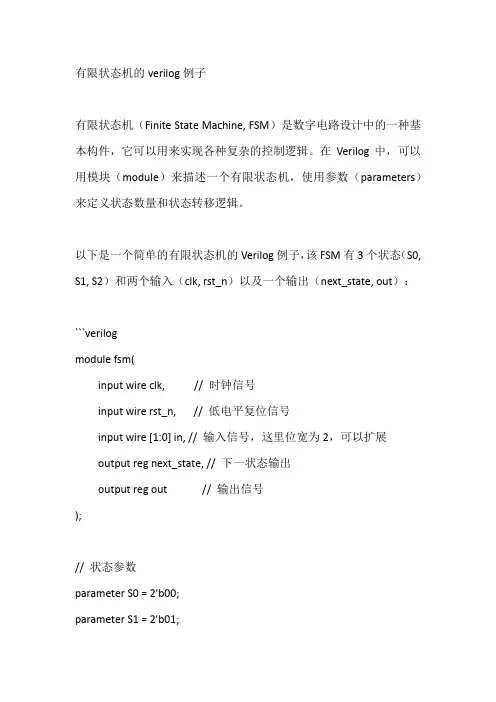

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

集成电路实验状态机设计实验报告专业:电子信息工程姓名:江燕婷学号:2011301200025状态机设计(实验五)实验报告一.实验目的1. 掌握状态机设计的基本方法2.学习利用状态机的方法实现控制电路二.实验原理有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。

有限状态机非常适合用FPGA器件实现,用Verilog HDL的case语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。

有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。

根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。

摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。

米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。

图1-1 摩尔型状态机图1-2 米里型状态机状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。

状态机的状态实现上,可采用符号编码或显式数字编码。

编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。

顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。

三. 实验设备与软件平台微型计算机,GW48-CK,QuartusII v5.0。

有限状态机FSM(FiniteStateMachine)及实现⽅式介绍⼀、为什么引⼊有限状态机? 最近做⼀个项⽬,项⽬中很多实体(Entity),每个实体都有很多状态(State),各状态会经过不同事件(Event)触发后转换到另⼀个状态。

这些事件包括但不限于:⽤户页⾯点击触发,⽣效时间或失效时间到达,其他依赖实体状态变更等。

在状态变更后还会有⼀系列动作(Action)处理。

⼀旦相互依赖实体或实体本⾝状态增多,状态转换变多,处理这些状态的业务代码也会分散在各处,代码处理很容易漏掉,维护成本很⾼。

所以考虑引⼊有限状态机。

⼆、什么是有限状态机? 有限状态机,也称为FSM(Finite State Machine),其在任意时刻都处于有限状态集合中的某⼀状态。

当其获得⼀个输⼊字符时,将从当前状态转换到另⼀个状态,或者仍然保持在当前状态。

任何⼀个FSM都可以⽤状态转换图来描述,图中的节点表⽰FSM中的⼀个状态,有向(⽅向表⽰从⼀个初态转换到次态)加权(权表⽰事件)边表⽰输⼊字符时状态的变化。

如果图中不存在与当前状态与输⼊字符对应的有向边,则FSM将进⼊“消亡状态(Doom State)”,此后FSM将⼀直保持“消亡状态”。

状态转换图中还有两个特殊状态:状态1称为“起始状态”,表⽰FSM的初始状态。

状态6称为“结束状态”。

在启动⼀个FSM时,⾸先必须将FSM置于“起始状态”,然后触发⼀系列时间,最终,FSM会到达“结束状态”或者“消亡状态”。

图1:状态转换图说明:在通常的FSM模型中,⼀般还存在⼀个“接受状态”,并且FSM可以从“接受状态”转换到另⼀个状态,只有在识别最后⼀个字符后,才会根据最终状态来决定是否接受所输⼊的字符串。

此外,也可以将“其实状态”也作为接受状态,因此空的输⼊序列也是可以接受的。

1. 状态机要素状态机可归纳为4个要素,即现态、条件、动作、次态。

“现态”和“条件”是因,“动作”和“次态”是果。

(完整版)FSM模型1. 引言有限状态机(Finite State Machine,简称FSM)是一种重要的数学模型和计算机科学的基础概念。

它被广泛应用于各种领域,如计算机程序设计、自动控制系统、人工智能等。

本文将介绍FSM 模型的基本概念、结构和应用。

2. FSM模型的基本概念FSM模型由状态、事件和转移函数组成。

在模型中,状态表示FSM的当前状态,事件表示FSM接收到的输入,转移函数则定义了FSM根据当前状态和事件进行状态转移的规则。

3. FSM模型的结构FSM模型通常包含以下几个要素:- 状态集合:所有可能的状态构成了状态集合。

- 开始状态:确定FSM的启动状态。

- 结束状态:定义了FSM的终止状态。

- 事件集合:FSM所接收的事件的集合。

- 转移函数:描述了FSM从一个状态根据接收到的事件进行状态转移的规则。

- 动作函数:定义了每个状态转移所执行的动作。

4. FSM模型的应用FSM模型在各个领域都有广泛的应用,以下是一些常见的应用场景:- 编译器设计:用于解析语法、词法分析和语义分析等阶段。

- 自动控制系统:用于描述控制器的行为和状态。

- 电信网络:用于描述通信协议的状态和行为。

- 游戏开发:用于角色行为的控制和状态管理。

- 自然语言处理:用于描述语言处理器的状态转移和行为。

5. FSM模型的优缺点FSM模型的优点包括:- 简单易懂:FSM模型的概念和结构相对简单,易于理解和实现。

- 易于调试:由于状态转移具有明确的规则,因此可以更容易地进行调试和错误排查。

- 可扩展性:FSM模型很容易新增状态和事件,支持系统的扩展和演化。

然而,FSM模型也存在一些缺点:- 复杂性限制:FSM模型适用于描述相对简单的系统,对于复杂系统的建模会变得非常困难。

- 状态爆炸:状态集合的规模可能会随着系统复杂性的增加而急剧增加,导致状态爆炸问题。

6. 总结FSM模型是一种强大的数学模型,被广泛应用于各种领域。

它具有简单易懂、易于调试和可扩展性的优点,但也存在复杂性限制和状态爆炸的缺点。

FSM( Finite State Machine 有限状态机)⏹状态机准备⏹状态机分类⏹Moore型状态机设计⏹状态机复位⏹Moore型状态机信号输出方法⏹Mealy型状态机⏹状态机容错设计为什么要使用状态机状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点状态机可以定义符号化枚举类型的状态状态机容易构成性能良好的同步时序逻辑模块状态机的VHDL表述丰富多样、程序层次分明,易读易懂在高速运算和控制方面,状态机更有其巨大的优势高可靠性FSM应用⏹FSM通过状态图描述状态转换过程⏹FSM:数字系统控制单元的建模⏹数字系统:❑受控模块:功能模块,设计较易❑控制模块实现⏹CPU⏹FSM❑执行耗费时间,执行时间的确定性方面,FSM优于CPUFSM 构成FSM用来解决一般时序逻辑电路问题,包括同步/异步时序逻辑⏹状态寄存器❑当前状态(现态)寄存器⏹组合逻辑电路❑下一状态(次态)组合逻辑❑输出组合逻辑FSM 分类⏹Moore 型:输出信号仅与现态相关⏹Mealy 型:输出信号与现态和输入相关DFFsOutput Comb. LogicFeedback Comb. Logic DFFsOutput Comb. LogicFeedback Comb. Logic 现态次态输入输出现态次态输出vhdl语言描述FSM的建立过程跟据具体要求分析控制过程,建立状态转移图后:⏹ 1. 定义枚举类型的信号描述状态⏹ 2. 建立第1个进程,描述次态组合逻辑,现态和输入信号作为敏感量,⏹ 3. 在进程中定义状态转移❑CASE WHEN语句的一条表示一个状态,状态转移通过IF THEN ELSE语句实现⏹4. 对于双进程FSM,建立第2个进程,现态寄存器描述进程,CLK,RST为敏感量;对于单进程FSM,则在一个进程中完成同步状态转移。

数据类型定义语句及状态机设计说明部分TYPE语句的用法如下:TYPE数据类型名IS数据类型定义OF基本数据类型;或TYPE 数据类型名IS 数据类型定义;TYPE m_state IS(st0,st1,st2,st3,st4,st5); SIGNAL present_state,next_state:m_state; ARCHITECTURE...ISTYPE FSM_ST IS(s0,s1,s2,s3);SIGNAL current_state,next_state:FSM_ST;...beginEDA 技术Stmch1.vhdlibrary ieee;use ieee.std_logic_1164.all;entity stmch1 is port(clk, in1, rst: in std_logic; out1: out std_logic);end stmch1;architecture behave of stmch1 istype state_values is (sx, s0, s1);signal state, next_state: state_values;beginprocess (clk, rst)beginif rst = '1' then state <= s0;elsif rising_edge(clk) then state <= next_state;end if;end process ;process (state, in1)begin--set defaults for output and stateout1 <= '0';next_state <= sx; --catch missing --assignments to --next_statecase state is when s0 =>if in1 = '0' then out1 <='1';next_state <= s1;elseout1 <= '0';next_state <= s0;end if ;when s1 =>if in1 = '0' then out1 <='0';next_state <= s0;else out1 <= '1';next_state <= s1;end if ;when sx =>next_state <= sx;end case;end process ;s0/0s1/1input=0Reset=1input=0input=1input=1Comb LogicDFFs in1state clkout1next_state Mealy 型:EDA 技术Mealy1.vhdlibrary ieee;use ieee.std_logic_1164.all;entity mealy1 is port(clk, rst: in std_logic;id: in std_logic_vector(3 downto 0);y: out std_logic_vector(1 downto 0));end mealy1;architecture archmealy of mealy1 istype states is (state0, state1, state2, state3, state4);signal state: states;beginMealy_proc: process (clk, rst) ……end process;end archmealy;Mealy_proc: process (clk, rst)beginif rst='1' thenstate <= state0;y <= "00";elsif (clk'event and clk='1') thencase state iswhen state0 =>if id = x"3" thenstate <= state1;y <= "10";elsestate <= state0;y <= "00";end if;when state1 =>state <= state2;y <= "11";when state2 =>if id = x"7" thenstate <= state3;y <= "10";elsestate <= state2;y <= "11";end if;when state3 =>if id < x"7" thenstate <= state0;y <= "00";elsif id = x"9" thenstate <= state4;y <= "11";elsestate <= state3;y <= "10";end if;when state4 =>if id = x"b" thenstate <= state0;y <= "00";elsestate <= state4;y <= "11";end if;DFFsOutput Comb. LogicFeedback Comb. LogicEDA技术statmach.vhdLibrary IEEE ;use IEEE.std_logic_1164.all ;ENTITY statmach ISPORT( clk : IN BIT;input : IN BIT;reset : IN BIT;output : OUT BIT);END statmach;ARCHITECTURE a OF statmach ISTYPE STATE_TYPE IS (s0, s1);SIGNAL state: STATE_TYPE;BEGINPROCESS(clk,reset)BEGINIF reset = '1' THENstate<= s0;ELSIF (clk'EVENT AND clk = '1') THEN CASE state ISWHEN s0=>state<= s1;WHEN s1=>IF input = '1' THENstate<= s0;ELSEstate<= s1;END IF;END CASE;END IF;END PROCESS;output<= '1' WHEN state= s1ELSE '0'; END a;s0/0s1/1input=1input=0 Reset=1FSM的复位⏹同步复位❑双进程状态机⏹在第1个进程的开始处用IF THEN 语句判断RESET,在其后的ELSE语句里用CASE语句定义状态转换⏹或者在第2个进程里定义同步复位❑单进程状态机⏹进程里定义同步复位⏹异步复位❑双进程状态机⏹在第2个进程里定义异步复位❑单进程状态机⏹进程里定义异步复位CASE_WHENIF …THENELSEPROCESS 1CLK’EVENTAND CLK=‘1’PROCESS 2次态现态输入输出Moore型有限状态机设(AD为例)多进程有限状态机Moore型有限状态机设多进程有限状态机控制ADC0809采样状态图多进程有限状态机LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADCINT ISPORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --来自0809转换好的8位数据CLK : IN STD_LOGIC; --状态机工作时钟EOC : IN STD_LOGIC; --转换状态指示,低电平表示正在转换ALE : OUT STD_LOGIC; --8个模拟信号通道地址锁存信号START : OUT STD_LOGIC; --转换开始信号OE : OUT STD_LOGIC; --数据输出3态控制信号ADDA : OUT STD_LOGIC; --信号通道最低位控制信号LOCK0 : OUT STD_LOGIC; --观察数据锁存时钟Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出END ADCINT;ARCHITECTURE behav OF ADCINT ISTYPE states IS (st0, st1, st2, st3,st4) ; --定义各状态子类型SIGNAL current_state, next_state: states :=st0 ;SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL LOCK: STD_LOGIC; --转换后数据输出锁存时钟信号BEGINADDA <= '1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1Q <= REGL; LOCK0 <= LOCK ;COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式CASE current_state ISWHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0';next_state <= st1; --0809初始化WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0';next_state <= st2; --启动采样WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0';IF (EOC='1') THEN next_state <= st3; --EOC=1表明转换结束ELSE next_state <= st2; END IF ; --转换未结束,继续等待WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1';next_state <= st4;--开启OE,输出转换好的数据WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1';next_state <= st0;WHEN OTHERS => next_state <= st0;END CASE ;END PROCESS COM ;REG: PROCESS (CLK)BEGINIF (CLK'EVENT AND CLK='1') THENcurrent_state<=next_state;END IF;END PROCESS REG ;--由信号current_state将当前状态值带出此进程:REG LATCH1: PROCESS (LOCK) --此进程中,在LOCK的上升沿,将转换好的数据锁入BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL <= D ; END IF;END PROCESS LATCH1 ;END behav;COM1:PROCESS(current_state,EOC)BEGINCASE current_state ISWHEN st0=>next_state<=st1;WHEN st1=>next_state<=st2;WHEN st2=>IF(EOC='1')THEN next_state<=st3;ELSE next_state<=st2;END IF;WHEN st3=>next_state<=st4;--开启OEWHEN st4=>next_state<=st0;WHEN OTHERS=>next_state<=st0;END CASE;END PROCESS COM1;COM2:PROCESS(current_state)BEGINCASE current_state ISWHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0';WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0';WHEN st2=>ALE<='0';START<='0';LOCK<='0';OE<='0';WHEN st3=>ALE<='0';START<='0';LOCK<='0';OE<='1';WHEN st4=>ALE<='0';START<='0';LOCK<='1';OE<='1';WHEN OTHERS=>ALE<='0';START<='0';LOCK<='0';END CASE;END PROCESS COM2;针对前面代码中的COM进程,把其中的状态及输出控制又分成双进程写ADC0809采样状态机工作时序单进程Moore型有限状态机LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MOORE1 ISPORT (DATAIN :IN STD_LOGIC_VECTOR(1 DOWNTO 0);CLK,RST : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END MOORE1;ARCHITECTURE behav OF MOORE1 ISTYPE ST_TYPE IS (ST0, ST1, ST2, ST3,ST4);SIGNAL C_ST : ST_TYPE ;BEGINPROCESS(CLK,RST)BEGINIF RST ='1' THEN C_ST <= ST0 ; Q<= "0000" ;ELSIF CLK'EVENT AND CLK='1' THEN(接下页)CASE C_ST ISWHEN ST0 => IF DATAIN ="10" THEN C_ST <= ST1 ;ELSE C_ST <= ST0 ; END IF;Q <= "1001" ;WHEN ST1 => IF DATAIN ="11" THEN C_ST <= ST2 ;ELSE C_ST <= ST1 ;END IF;Q <= "0101" ;WHEN ST2 => IF DATAIN ="01" THEN C_ST <= ST3 ;ELSE C_ST <= ST0 ;END IF;Q <= "1100" ;WHEN ST3 => IF DATAIN ="00" THEN C_ST <= ST4 ;ELSE C_ST <= ST2 ;END IF;Q <= "0010" ;WHEN ST4 => IF DATAIN ="11" THEN C_ST <= ST0 ;ELSE C_ST <= ST3 ;END IF;Q <= "1001" ;WHEN OTHERS => C_ST <= ST0;END CASE;END IF;END PROCESS;END behav;Moore型有限状态机设单进程状态机工作时序1.0μs2.0μs3.0μs4.0μs5.0μs6.0μs7.0μs8.0μs8.2 Moore型有限状态机设二进程状态机工作时序图Mealy型有限状态机设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MEALY1 ISPORT ( CLK ,DATAIN,RESET : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(4 DOWNTO 0));END MEALY1;ARCHITECTURE behav OF MEALY1 ISTYPE states IS (st0, st1, st2, st3,st4);SIGNAL STX : states ;BEGINCOMREG : PROCESS(CLK,RESET) BEGIN --决定转换状态的进程IF RESET ='1' THEN STX <= ST0;ELSIF CLK'EVENT AND CLK = '1' THEN CASE STX IS WHEN st0 => IF DATAIN = '1' THEN STX <= st1; END IF;WHEN st1 => IF DATAIN = '0' THEN STX <= st2; END IF;(接下页)WHEN st2 => IF DATAIN = '1' THEN STX <= st3; END IF;WHEN st3=> IF DATAIN = '0' THEN STX <= st4; END IF;WHEN st4=> IF DATAIN = '1' THEN STX <= st0; END IF;WHEN OTHERS => STX <= st0;END CASE ;END IF;END PROCESS COMREG ;COM1: PROCESS(STX,DATAIN) BEGIN --输出控制信号的进程CASE STX ISWHEN st0 => IF DATAIN = '1' THEN Q <= "10000" ;ELSE Q<="01010" ; END IF ;WHEN st1 => IF DATAIN = '0' THEN Q <= "10111" ;ELSE Q<="10100" ; END IF ;WHEN st2 => IF DATAIN = '1' THEN Q <= "10101" ;ELSE Q<="10011" ; END IF ;WHEN st3=> IF DATAIN = '0' THEN Q <= "11011" ;ELSE Q<="01001" ; END IF ;WHEN st4=> IF DATAIN = '1' THEN Q <= "11101" ;ELSE Q<="01101" ; END IF ;WHEN OTHERS => Q<="00000" ;END CASE ;END PROCESS COM1 ;Mealy型有限状态机设计1.5μs2.0μs 2.5μs3.0μs 3.5μs4.0μs 4.5μs双进程Mealy状态机工作时序图8.3 Mealy型有限状态机设计LIBRARY IEEE;--MEALY FSMUSE IEEE.STD_LOGIC_1164.ALL;ENTITY MEALY2ISPORT(CLK,DATAIN,RESET:IN STD_LOGIC;Q:OUT STD_LOGIC_VECTOR(4DOWNTO0));END MEALY2;ARCHITECTURE behav OF MEALY2ISTYPE states IS(st0,st1,st2,st3,st4);SIGNAL STX:states;SIGNAL Q1:STD_LOGIC_VECTOR(4DOWNTO0);BEGINCOMREG:PROCESS(CLK,RESET)--决定转换状态的进程BEGINIF RESET='1'THEN STX<=ST0;ELSIF CLK'EVENT AND CLK='1'THENCASE STX IS(接下页)WHEN st0=>IF DATAIN='1'THEN STX<=st1;END IF;WHEN st1=>IF DATAIN='0'THEN STX<=st2;END IF;WHEN st2=>IF DATAIN='1'THEN STX<=st3;END IF;WHEN st3=>IF DATAIN='0'THEN STX<=st4;END IF;WHEN st4=>IF DATAIN='1'THEN STX<=st0;END IF;WHEN OTHERS=>STX<=st0;END CASE;END IF;END PROCESS COMREG;COM1:PROCESS(STX,DATAIN,CLK)--输出控制信号的进程VARIABLE Q2:STD_LOGIC_VECTOR(4DOWNTO0);BEGINCASE STX ISWHEN st0=>IF DATAIN='1'THEN Q2:="10000";ELSE Q2:="01010";END IF; WHEN st1=>IF DATAIN='0'THEN Q2:="10111";ELSE Q2:="10100";END IF; WHEN st2=>IF DATAIN='1'THEN Q2:="10101";ELSE Q2:="10011";END IF; WHEN st3=>IF DATAIN='0'THEN Q2:="11011";ELSE Q2:="01001";END IF; WHEN st4=>IF DATAIN='1'THEN Q2:="11101";ELSE Q2:="01101";END IF; WHEN OTHERS=>Q2:="00000";END CASE;IF CLK‘EVENT AND CLK=’1‘THEN Q1<=Q2;END IF;//输出引入触发器END PROCESS COM1;8.3 Mealy型有限状态机设计1.5μs2.0μs 2.5μs3.0μs 3.5μs4.0μs 4.5μs输出引入触发器后的状态机工作时序图FSM信号输出方法⏹由状态编码位经组合译码后输出⏹并行输出寄存器的译码输出⏹状态位里的编码输出⏹一位有效编码方式FSM输出方法1由状态编码位经组合译码后输出delay并行输出寄存器的译码输出⏹状态位里的编码输出❑缩短输出延时❑要求状态位编码与输出信号要求的值相结合EDA 技术Moore1.vhdlibrary ieee;use ieee.std_logic_1164.all;entity moore1 is port(clk, rst: in std_logic;id: in std_logic_vector(3 downto 0);y: out std_logic_vector(1 downto 0));end moore1;architecture archmoore1 of moore1 is type states is (state0, state1, state2, state3, state4);signal state: states;begin moore: process (clk, rst)… …End process --assign state outputs concurrently;y <= "00" when (state=state0) else "10" when (state=state1 or state=state3) else"11";end archmoore1;moore: process (clk, rst) --this process defines the next state only beginif rst='1' thenstate <= state0;elsif (clk'event and clk='1') then case state iswhen state0 =>if id = x"3" thenstate <= state1;else state <= state0;end if;when state1 =>state <= state2;when state2 =>if id = x"7" then state <= state3;elsestate <= state2;end if;when state3 =>if id < x"7" thenstate <= state0;elsif id = x"9" then state <= state4;elsestate <= state3;end if;when state4 =>if id = x"b" then state <= state0;elsestate <= state4;end if;end case;DFFs Output Comb. LogicFeedback Comb. LogicEDA 技术Moore2.vhdlibrary ieee;use ieee.std_logic_1164.all;entity moore2 is port(clk, rst: in std_logic;id: in std_logic_vector(3 downto 0);y: out std_logic_vector(1 downto 0));end moore2;architecture archmoore2 of moore2 issignal state: std_logic_vector(2 downto 0);--State assignment is such that 2 LSBs are outputsconstant state0: std_logic_vector(2 downto 0) := "000";constant state1: std_logic_vector(2 downto 0) := "010";constant state2: std_logic_vector(2 downto 0) := "011";constant state3: std_logic_vector(2 downto 0) := "110";constant state4: std_logic_vector(2 downto 0) := "111";beginmoore: process (clk, rst)…end process;--assign state outputs (equal to state std_logics)y <= state(1 downto 0);end archmoore2;moore: process (clk, rst)beginif rst='1' thenstate <= state0;elsif (clk'event and clk='1') thencase state is when state0 =>if id = x"3" thenstate <= state1;elsestate <= state0;end if;when state1 =>state <= state2;when state2 =>if id = x"7" then state <= state3;else state <= state2;end if;when state3 =>if id < x"7" then state <= state0;elsif id = x"9" then state <= state4;else state <= state3;end if;when state4 =>if id = x"b" thenstate <= state0;elsestate <= state4;end if;when others =>state <= state0;DFFsFeedback Comb. LogicNo output comb.Logic, no race orhazardFSM输出方法4⏹ONE HOT编码⏹使用N位状态寄存器表达具有Ng 状态的FSM,每个状态具有独立的寄存器位。

【 】【游戏中有限状态机FSM的三种实现方法】有限状态机,英文Finite state machine,简称FSM。

至今在游戏中应用广泛,今天总结性地说说其三种实现方法(注意其中的代码系伪代码,主要为说明思想,并不一定能运行。

)(一)基本概念首先看看比较严格的定义:有限状态机(Finite State Machine)是具有离散输入和输出系统的一种数学模型。

表示有限个状态以及在条件输入下状态之间的转移行为。

具有有限个内部状态,随着信号(条件)的输入,内部状态不断地转移。

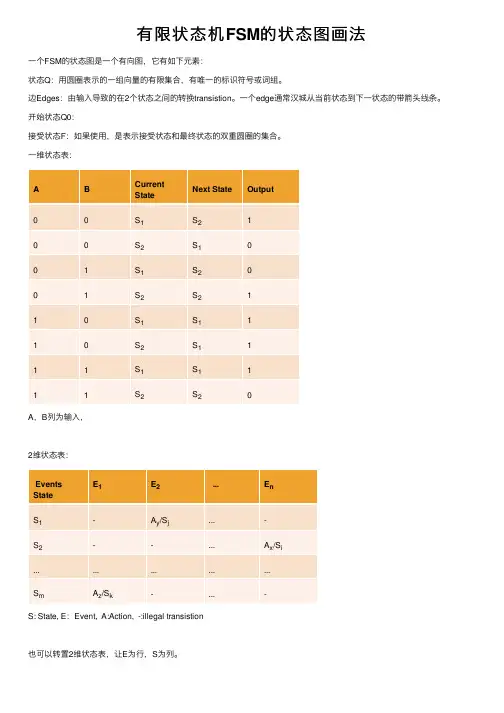

通常我们用状态迁移图或状态迁移表来表示:(请看以下示例)图b就是与图a等价的状态迁移表。

系统中可取得的状态=S1,S2,S3,事件=t1,t2,t3,t4。

事件t1将引起系统状态S1向状态S3迁移,事件t2将引起系统状态S3向状态S2迁移,等等另外,状态迁移图指明了作为特定事件的结果(状态)。

在状态中包含可能执行的行为。

(二)实现方法下面看看其三种实现方法:1)switch case/if else设计方法2)基于表结构的状态机设计方法3)状态设计模式下面分别说说其思想(主要基于C/C++伪码):1)switch case/if else设计方法enum StateType{state_RunAway,state_Patrol,state_attack};void Agent::UpdateState(StateType CurrentState){switch(CurrentState) {case state_RunAway:EvadeEnemy();if (Safe()) { ChangeState(state_ Patrol); }break;case state_Patrol:FollowPatrolPath();if (Threatened())if (StrongerThanEnemy()) { ChangeState(state_Attack); }else { ChangeState(state_ RunAway); }break;case state_Attack:if (WeakerThanEnemy()) { ChangeState(state RunAway); } else { BashEnemyOverHead(); }break;}//end switch}这个比较简单,不说鸟2)基于表结构的状态机设计方法/*状态1的动作表*/ACT_TABLE_T state1ActTable[] = {{EVENT1,state1Event1Fun},{EVENT3,state1Event3Fun},};/*状态2的动作表*/ACT_TABLE_T state2ActTable[] = {{EVENT2,state2Event2Fun},};/*状态表*/STATE_TABLE_T FsmTable[] = {{STATE1,state1ActTable},{STATE2,state2ActTable},};/*客户端提供的状态处理函数*/void state1Event1Fun(void* pFsm){FSM_MoveState((FSM_T*)pFsm,STATE2);return;}void state1Event3Fun(void* pFsm){FSM_MoveState((FSM_T*)pFsm,STATE3);return;}void state2Event2Fun(void* pFsm){FSM_MoveState((FSM_T*)pFsm,STATE3);return;}FSM_Regist(&fsm,FsmTable);...可以看出此种方式,可以实现状态机的热更新,因为这些表格是存在数组里面的。