异步二进制加法计数器

- 格式:ppt

- 大小:1.69 MB

- 文档页数:87

计数器的原理计数器是数字电路中广泛使用的逻辑部件,是时序逻辑电路中最重要的逻辑部件之一。

计数器除用于对输入脉冲的个数进行计数外,还可以用于分频、定时、产生节拍脉冲等。

计数器按计数脉冲的作用方式分类,有同步计数器和异步计数器;按功能分类,有加法计数器、减法计数器和既具有加法又有减法的可逆计数器;按计数进制的不同,又可分为二进制计数器、十进制计数器和任意进制计数器。

一、计数器的工作原理1、二进制计数器(1)异步二进制加法计数器图1所示为用JK触发器组成的4位异步二进制加法计数器逻辑图。

图中4个触发器F0~F3均处于计数工作状态。

计数脉冲从最低位触发器F0的CP端输入,每输入一个计数脉冲,F0的状态改变一次。

低位触发器的Q端与高位触发器的CP端相连。

每当低位触发器的状态由1变0时,即输出一负跳变脉冲时,高位触发器翻转。

各触发器置0端R D并联,作为清0端,清0后,使触发器初态为0000。

当第一个计数脉冲输入后,脉冲后沿使F0的Q0由0变1,F1、F2、F3均保持0态,计数器的状态为0001;当图1 4位异步二进制加法计数器第二个计数脉冲输入后,Q0由1变为0,但Q0的这个负跳变加至F1的CP端,使Q1由0变为1,而此时F3、F2仍保持0状态,计数器的状态为0010。

依此类推,对于F0来说,每来一个计数脉冲后沿,Q0的状态就改变,而对于F1、F2、F3来说,则要看前一位输出端Q是否从1跳到0,即后沿到来时,其输出端的状态才改变,否则Q1、Q2、Q3端的状态同前一个状态一样。

这样在第15个计数脉冲输入后,计数器的状态为1111,第16个计数脉冲输入,计数器恢复为0000。

由上述分析可知,一个4位二进制加法计数器有24=16种状态,每经过十六个计数脉冲,计数器的状态就循环一次。

通常把计数器的状态数称之为计数器的进制数(或称计数器的模),因此,4位二进制计数器也可称之为1位十六进制(模16)计数器。

表1所示为4位二进制加法计数器的状态表。

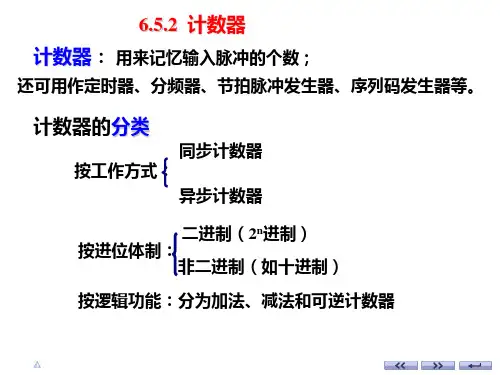

计数器原理计数器是数字系统中用的较多的基本逻辑器件,它的基本功能是统计时钟脉冲的个数,即实现计数操作,它也可用与分频、定时、产生节拍脉冲和脉冲序列等。

例如,计算机中的时序发生器、分频器、指令计数器等都要使用计数器。

计数器的种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;按计数过程中数字增减趋势的不同,可分为加法计数器、减法计数器和可逆计数器;还有可预制数和可编计数器等等。

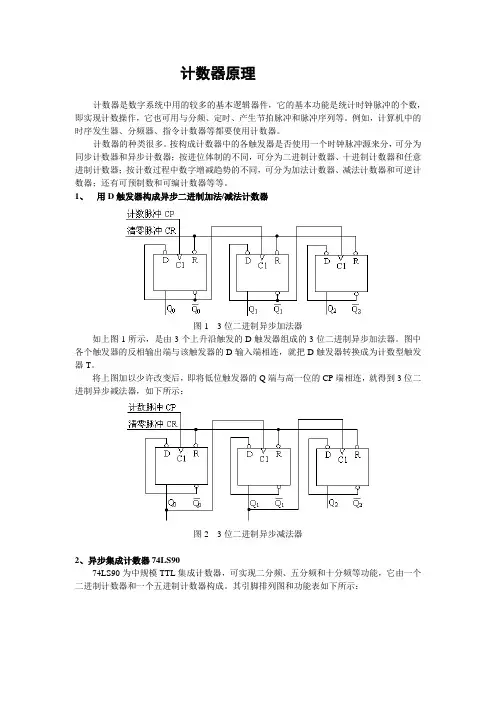

1、用D触发器构成异步二进制加法/减法计数器图1 3位二进制异步加法器如上图1所示,是由3个上升沿触发的D触发器组成的3位二进制异步加法器。

图中各个触发器的反相输出端与该触发器的D输入端相连,就把D触发器转换成为计数型触发器T。

将上图加以少许改变后,即将低位触发器的Q端与高一位的CP端相连,就得到3位二进制异步减法器,如下所示:图2 3位二进制异步减法器2、异步集成计数器74LS9074LS90为中规模TTL集成计数器,可实现二分频、五分频和十分频等功能,它由一个二进制计数器和一个五进制计数器构成。

其引脚排列图和功能表如下所示:图3 74LS90的引脚排列图表1 74LS90的功能表3、中规模十进制计数器74LS192(或CC40192)74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:图4 74LS192的引脚排列及逻辑符号(a )引脚排列 (b) 逻辑符号图中:PL 为置数端,U CP 为加计数端,D CP 为减计数端,U TC 为非同步进位输出端,TC为非同步借位输出端,P0、P1、P2、P3为计数器输入端,MR为清除端,Q0、Q1、DQ2、Q3为数据输出端。

其功能表如下:表2 74LS192的功能表4、4位二进制同步计数器74LS161该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端,可以串接计数器使用。

实验八计数器一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理。

2.熟悉掌握常用中规模集成电路计数器及其应用方法。

二、实验原理和电路所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。

根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。

根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的。

根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器异步二进制加法计数器是比较简单的。

图是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FF O(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的CP端接FF0的Q0端,因而当FF O(Q O)由1→ 0时,FF1翻转。

类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

从波形图可看到,Q0 的周期是CP周期的二倍;Q1 是Q0的二倍,CP的四倍;Q2是Q1 的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0的八倍,CP的十六倍。

所以Q0 、Q1、Q2、Q3分别实现了二、四、八、十六分频,这就是计数器的分频作用。

同步计数器和异步计数器的区别

同步异步计数器区分:同步计数器的触发信号是同一个信号。

具体来说,每一级的触发器接的都是同一个CLK信号。

异步计数器的触发信号时不同的,例如第一集的输出Q’作为第二级的触发信号。

几进制的区分:看数据输出端得接线方法,当接线满足拿个计数时会导致“清零”端或者是“置数端”满足工作状态。

导致这一计数状态之后回到零。

这样子就很容易的判定计数器是几进制的了。

异步计数器

在异步计数器中,有的触发器直接受输入计数脉冲控制,有的触发器则是把其它触发器的输出信号作为自己的时钟脉冲,因此各个触发器状态变换的时间先后不一,故被称为“ 异步计数器”。

同步计数器

在同步计数器中,各触发器受同一输入计数脉冲控制,计数脉冲同时接到各位触发器,各触发器状态的变换与计数脉冲同步,故称为“ 同步计数器”。

由于各触发器同步翻转,因此工作速度快,但接线较复杂。

异步二进制加法计数器线路联接简单,各触发器是逐级翻转,因而工作速度较慢。

计数器的原理计数器是数字电路中广泛使用的逻辑部件,是时序逻辑电路中最重要的逻辑部件之一。

计数器除用于对输入脉冲的个数进行计数外,还可以用于分频、定时、产生节拍脉冲等。

计数器按计数脉冲的作用方式分类,有同步计数器和异步计数器;按功能分类,有加法计数器、减法计数器和既具有加法又有减法的可逆计数器;按计数进制的不同,又可分为二进制计数器、十进制计数器和任意进制计数器。

一、计数器的工作原理1、二进制计数器(1)异步二进制加法计数器图1所示为用JK触发器组成的4位异步二进制加法计数器逻辑图。

图中4个触发器F0~F3均处于计数工作状态。

计数脉冲从最低位触发器F0的CP端输入,每输入一个计数脉冲,F0的状态改变一次。

低位触发器的Q端与高位触发器的CP端相连。

每当低位触发器的状态由1变0时,即输出一负跳变脉冲时,高位触发器翻转。

各触发器置0端R D并联,作为清0端,清0后,使触发器初态为0000。

当第一个计数脉冲输入后,脉冲后沿使F0的Q0由0变1,F1、F2、F3均保持0态,计数器的状态为0001;当图1 4位异步二进制加法计数器第二个计数脉冲输入后,Q0由1变为0,但Q0的这个负跳变加至F1的CP端,使Q1由0变为1,而此时F3、F2仍保持0状态,计数器的状态为0010。

依此类推,对于F0来说,每来一个计数脉冲后沿,Q0的状态就改变,而对于F1、F2、F3来说,则要看前一位输出端Q 是否从1跳到0,即后沿到来时,其输出端的状态才改变,否则Q1、Q2、Q3端的状态同前一个状态一样。

这样在第15个计数脉冲输入后,计数器的状态为1111,第16个计数脉冲输入,计数器恢复为0000。

由上述分析可知,一个4位二进制加法计数器有24=16种状态,每经过十六个计数脉冲,计数器的状态就循环一次。

通常把计数器的状态数称之为计数器的进制数(或称计数器的模),因此,4位二进制计数器也可称之为1位十六进制(模16)计数器。

表1所示为4位二进制加法计数器的状态表。