How to enable spidev for all SPI (1-5) for MX6 _ Freescale Community

- 格式:pdf

- 大小:392.15 KB

- 文档页数:11

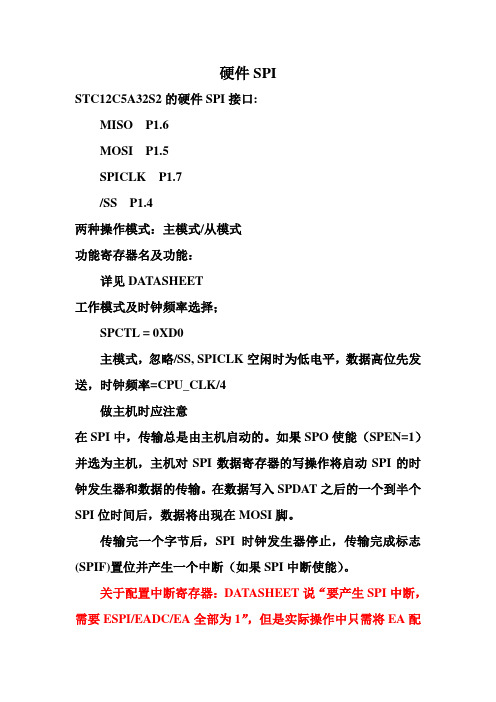

硬件SPISTC12C5A32S2的硬件SPI接口:MISO P1.6MOSI P1.5SPICLK P1.7/SS P1.4两种操作模式:主模式/从模式功能寄存器名及功能:详见DATASHEET工作模式及时钟频率选择;SPCTL = 0XD0主模式,忽略/SS, SPICLK空闲时为低电平,数据高位先发送,时钟频率=CPU_CLK/4做主机时应注意在SPI中,传输总是由主机启动的。

如果SPO使能(SPEN=1)并选为主机,主机对SPI数据寄存器的写操作将启动SPI的时钟发生器和数据的传输。

在数据写入SPDAT之后的一个到半个SPI位时间后,数据将出现在MOSI脚。

传输完一个字节后,SPI时钟发生器停止,传输完成标志(SPIF)置位并产生一个中断(如果SPI中断使能)。

关于配置中断寄存器:DATASHEET说“要产生SPI中断,需要ESPI/EADC/EA全部为1”,但是实际操作中只需将EA配置为1(总中断打开)就行了,而且ESPI是IE2中的寄存器关于这个问题,我认为是因为这里是MCU做主机,AD5612为从(AD5612只能为从)。

而DATASHEET上的例子为两个MCU,用/SS做主从选择时的应用方法具体程序:/**************************************************函数原型:void readMemoryArrayclock_SPI()功能:SPI发送数据。

***************************************************unsigned char readMemoryArrayclock_SPI(date){SPDAT = date;while(!(SPSTAT & 0x80)); //判断传输是否完成SPSTAT = 0Xc0; //清零(向该两个标志位写“1”,会将它们清零)return date;}/**************************************************函数原型:void writeMemoryArrayclock_SPI()功能:SPI接收数据。

© 2021 NXP B.V.S32G-VNP-GLDBOX User GuideNXP Semiconductors Document Number: S32G-VNP-GLDBOXUGUser's GuideRev. 0 , 03/2021Contents1.Get to know the S32G-VNP-GLDBOX (4)1.1 S32G-VNP-GLDBOX Reference Design Overview (4)1.2 S32G-VNP-GLDBOX Block Diagram (5)1.3 S32G-VNP-GLDBOX Hardware Resources (5)2.S32G-VNP-GLDBOX Hardware Packages (7)2.1 Hardware Package Overview (7)2.2 Hardware Connection Instruction (7)3.S32G-VNP-GLDBOX Switch Setting (8)3.1 Default Switch Setting (8)3.2 Switch Setting for Power Selection (8)3.3 Switch Setting for SD card Boot (9)3.4 Switch Setting for eMMC Boot (9)3.5 Switch Setting for NOR Flash Boot (10)3.6 Switch Setting for Serial Boot (10)4.S32G-VNP-GLDBOX Connectors (11)4.1 Connectors Overview (11)4.2 Specific Connector Instruction (13)5.S32G-VNP-GLDBOX Set Up (14)6.Appendix A (16)S32G-VNP-GLDBOX User Guide, Rev. 0, 03/20212NXP SemiconductorsS32G-VNP-GLDBOX User Guide, Rev. 0, 03/20214NXP Semiconductors1. Get to know the S32G-VNP-GLDBOX1.1 S32G-VNP-GLDBOX Reference Design OverviewThe S32G-VNP-GLDBOX (GoldBox) is a compact, highly-optimized and integrated reference design board with enclosure featuring the S32G Vehicle Network Processor. This board can provide reference for a variety of typical automotive applications such as:• Service-oriented gateway, vehicle compute nodes • Domain controller, safety controller • Vehicle black-box • FOTAFigure 1.1 shows the S32G-VNP-GLDBOX.PCIe X1 SocketSD Card SlotS32G274A ProcessorLPDDR4(4GB)TransceiverSJA1110ANOR Flash (64MB)Figure 1.1 S32G-VNP-GLDBOXS32G-VNP-GLDBOX User Guide, Rev. 0, 03/2021NXP Semiconductors51.2 S32G-VNP-GLDBOX Block DiagramFigure 1.2 shows the block diagram of the S32G-VNP-GLDBOX.Figure 1.2 S32G-VNP-GLDBOX block diagram1.3 S32G-VNP-GLDBOX Hardware ResourcesThe resources of the GoldBox are listed as below:• Processor➢ Four Arm Cortex-A53 cores (with optional cluster lockstep) ➢ Three, dual-core lockstep Arm Cortex-M7 cores➢ Hardware Security Engine (HSE) supports SHE/EVITA➢ CAN, LIN and FlexRay offload with Low Latency Communications Engine (LLCE) ➢ Gigabit Ethernet Packet Forwarding Engine (PFE) ➢ 8 MB Embedded System RAM with ECC ➢ 32KB Standby RAM with ECC• External Storage➢ 1 x NOR Flash (64MB) ➢ 1 x SD card slot ➢ 1 x eMMC (32GB) ➢ 1 x LPDDR4 (4GB)• Ethernet —12ports➢ 1 x 100BASE-TX➢ 6 x 100BASE-T1➢ 5 x 1000BASE-T•PCIe➢ 1 x M.2 M-key slot*➢ 1 x M.2 E-key slot*➢ 1 x PCIe X1 socket•LIN➢ 4 x LLCE LIN➢ 1 x LINFlexD•CAN/CAN FD➢16 x LLCE CAN/CAN FD➢ 2 x FlexCAN /CAN FD•FlexRay➢ 1 x LLCE FlexRay•USB➢ 1 x USB 2.0 port as host/device mode•Scalable interface➢ 1 x DSPI➢ 5 x ADC➢ 1 x I2C•RTC➢Support for external RTC•Debug and Trace➢ 1 x 20-pin JTAG for S32G➢ 1 x 10-pin JTAG for SJA1110A➢ 1 x Aurora Trace➢ 2 x UARTS32G-VNP-GLDBOX User Guide, Rev. 0, 03/20216NXP SemiconductorsS32G-VNP-GLDBOX User Guide, Rev. 0, 03/2021NXP Semiconductors72. S32G-VNP-GLDBOX Hardware Packages2.1 Hardware Package OverviewThe following section describes the hardware package overview of S32G-VNP-GLDBOX. Hardware andaccessories are needed as shown in the figure 2.1.Universal AdaptorDuPont LineEthernet Loop-BackCableAC/DC 12V PowerSupply SD Card UART0 UART1Cable Ethernet CableHeatsinkJ5 Cable (LIN, ADC)J53 Cable (100BASE-T1)Thermal Pad andScrewJ6 Cable (CAN, FlexRay)Figure 2.1 S32G-VNP-GLDBOX hardware and accessories2.2 Hardware Connection InstructionTo connect any cable to the GoldBox, follow the instructions shown in figure 2.2.UART cable connectionJ6 cable connection (LLCE CAN, FlexCAN, FlexRay)J5 cable connection(LLCE LIN, LINFlexD, ADC)J53 cable connection(100BASE-T1)P5, P4, P3, P2 cable connection(1000GBASE-T, 100BASE-TX, 1000BASE-T)Figure 2.2 S32G-VNP-GLDBOX hardware connection instructionS32G-VNP-GLDBOX User Guide, Rev. 0, 03/20218 NXP Semiconductors3. S32G-VNP-GLDBOX Switch Setting3.1 Default Switch SettingFigure 3.1 shows the default switch setting of the S32G-VNP-GLDBOX.SW7SW6SW5SW4SW11SW9SW10SW12SW8SW17SW3SW12SW3SW4SW5SW6SW7SW8SW9SW10SW11SW176th-OFF 7th-ON ALL-OFFALL-OFFALL-OFFFigure 3.1 Default switch setting3.2 Switch Setting for Power SelectionFigure 3.2 shows the switch setting for power selection.SW15SW15SW15Figure 3.2 Power selection switch settingS32G-VNP-GLDBOX User Guide, Rev. 0, 03/2021NXP Semiconductors93.3 Switch Setting for SD card BootFigure 3.3 shows the switch setting for SD card boot.SW7SW6SW5SW4SW9SW10SW3SW3SW4SW5SW6SW7SW9SW106th-OFF 7th-ON ALL-OFFALL-OFFALL-OFFCompare with default setting, no changeneededFigure 3.3 SD card boot switch setting3.4 Switch Setting for eMMC BootSW7SW6SW5SW4SW9SW10SW3SW3SW4SW5SW6SW7SW9SW106th-ON 7th-ON ALL-OFFALL-OFFALL-OFFCompare with default setting, the SW3 and the6th of SW4 need to be changedFigure 3.4 eMMC boot switch settingS32G-VNP-GLDBOX User Guide, Rev. 0, 03/202110 NXP Semiconductors3.5 Switch Setting for NOR Flash BootFigure 3.5 shows the switch setting for NOR Flash boot.SW7SW6SW5SW4SW9SW10SW3SW4SW5SW6SW7SW9SW106th-OFF 7th-OFF ALL-OFFALL-OFFALL-OFFCompare with default setting, the 7th of SW4Figure 3.5 NOR Flash boot switch setting3.6 Switch Setting for Serial BootSW9SW10Compare with default setting, the 1st of SW10Figure 3.6 Serial boot switch settingS32G-VNP-GLDBOX User Guide, Rev. 0, 03/2021NXP Semiconductors114. S32G-VNP-GLDBOX Connectors4.1 Connectors OverviewFigure 4.1 shows the part of important connectors of the S32G-VNP-GLDBOX.J5J6J1J2J4J3J57J44J47J56P3P2P4P5J53J48P1J176J184J180Figure 4.1 S32G-VNP-GLDBOX connectorsTable 4.1 shows the connectors of the S32G-VNP-GLDBOX and their corresponding signals.S32G-VNP-GLDBOX User Guide, Rev. 0, 03/202112NXP SemiconductorsS32G-VNP-GLDBOX User Guide, Rev. 0, 03/2021NXP Semiconductors134.2 Specific Connector InstructionFigure 4.2 shows the LLCE CAN, FlexCAN, LLCE FlexRay, ADC, LINFlexD and LLCE LIN connectors.J6J5240226USB UART0UART1J6J5Figure 4.2 FlexRay&CAN&LIN&ADC ConnectionsFigure 4.3 shows the Ethernet connectors.P5P4P3A P3BP2AP2BJ53110Figure 4.3 Ethernet ConnectionsS32G-VNP-GLDBOX User Guide, Rev. 0, 03/202114 NXP Semiconductors5. S32G-VNP-GLDBOX Set UpFollowing steps show how to run Linux BSP on CortexA53 core:1. Download and install the terminal emulator, if not installed already. About the terminal tool, you can choose any one which is familiar to you, such as Tera Term, Putty and so on.2. Download and install the FT232R USB-to-UART driver, if not installed already. Go to FT232R USB-to-UART driver link .Scroll down and select correct version. Follow the installation guides to install the driver.3. Set S32G-VNP-GLDBOX in SD card boot mode(refer to the Figure 3.2).4. Plug the SD card in J3 slot. The SD card has pre-loaded Linux BSP image which runs on CortexA53 cores.5. Connect the UART0 port(J2) of board and PC by UART cable. Then open serial terminal and configure COM port in PC. Select the corresponding COM port which can be found in “Device Manager” of the PC and set 115200 as the baud rate. The configuration result is shown in the figure 5.1.Figure 5.1 COM port configuration6.Connect power supply though J176 port described in Table 4.1. Open the power switch(refer to figure 3.2), the running logs will appear in the console as shown in Figure 5.2.…………[ 5.414637] mdio_bus PFEng Ethernet MDIO.pfe2: MDIO device ataddress 2 is missing.[ 5.481480] loading NXP PHY driver: [autonomous mode][ 5.578156] sja1105pqrs spi1.0: Loading SJA1105P SPI driver[ 5.583510] sja1105pqrs spi1.0: Detected device id is invalid: ffffffff[ 5.590005] sja1105pqrs spi1.0: SJA1105P SPI Failed to read Device Id[ 5.612947] EXT4-fs (mmcblk0p2): re-mounted. Opts: (null)Fri Aug 28 01:21:01 UTC 2020[ 5.897075] urandom_read: 3 callbacks suppressed[ 5.897084] random: dd: uninitialized urandom read (512 bytes read)INIT: Entering runlevel: 5Configuring network interfaces... ifup: don't have all variables for eth0/inetStarting syslogd/klogd: doneStarting random number generator daemon[ 6.098288] random: rngd:uninitialized urandom read (4 bytes read)[ 6.104307] random: rngd: uninitialized urandom read (4 bytes read).[ 6.111860] random: crng init done[ 6.115160] random: 1 urandom warning(s) missed due to ratelimitingStarting OpenBSD Secure Shell server: sshddone.Auto Linux BSP 1.0 s32g274ardb /dev/ttyLF0s32g274ardb login:Figure 5.2 Running logs of Linux BSPWhen see the console as shown in the Figure 5.2, it means that the Linux BSP runs successfully. Please input “root” to log in system. And if need to run the M7 project, please refer to the S32G-VNP-GLDBOX Software Enablement Guide.S32G-VNP-GLDBOX User Guide, Rev. 0, 03/2021NXP Semiconductors 15, Rev. 0, 03/202116 NXP Semiconductors6. Appendix A•Documents— S32G Data Sheet— S32G Reference Manual — GoldBox Fact sheet— S32G-VNP-GLDBOX Reference Manual— S32G-VNP-GLDBOX Software Enablement Guide — Auto_Linux_BSP_XX.X_S32G274A_User_Manual — Auto_Linux_BSP_XX.X_S32G274A_Quick_Start • Useful links— S32 Design Studio — S32 Debug Probe• Support https:/// • Enablement Tools— IDE: S32 Design Studio, Yocto , EB tresos TM— Software: Linux BSP, FreeRTOS TM , Real-Time Drivers(RTD) — Compiler: Green Hills, gcc— Debugger: Lauterbach, S32G Debug ProbeHow To Reach Us Home Page: Web Support: /support Information in this document is provided solely to enable system and software implementersto use NXP products. There are no express or implied copyright licenses granted hereunderto design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the applicationor use of any product or circuit, and specifically disclaims any and all liability, includingwithout limitation consequential or incidental damages. “Typical” parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals,”must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: /SalesTermsandConditions.While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer’s applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C‑5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C‑Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service namesare the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and word marks and the Power and logos and related marks are trademarks and service marks licensed by .© NXP B.V. 2021.All rights reserved.For more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:**********************Date of release: March, 2021Document identifier: S32G-VNP-GLDBOXUG。

C6678 SPI Boot ExamplePurposeThe purpose of this lab is to demonstrate all the steps that are needed to boot an allocation from SPI flash memory.Dependencies:∙Code composer Studio v5 or v6∙MCSDK or Processor SDK RTOS software for C6678Note: Files under mcsdk_2_01_XX_YY\tools\boot_loader have been moved topdk_c66xx_2_0_0\packages\ti\bootTask 1: Observe the source file and build the application. Verify that it works correctlyThe example application included in the package can be built using gmake or CCS in the Windows environment.GMAKE based built Procedure:1.Browse to makefile in the led_play folder under src folder2.In the Makefile set the path to C6000_FOLDER and PDK_PACKAGES. Note that thePDK_PACKAGES must contain path until the packages folder inside the PDK component.3.In the windows command prompt, add the gmake path to the PATH variable usingSet PATH=%PATH%;<CCS_INSTALL_PATH>\utils\bin4.From command line you can now build the example usinggmake cleangmake allCCS based build Procedure1.Open CCS Editor and import the led_play project from the src folder.2.Right click on the project and Open Project properties. Under Build or C/C++ Build (may varybased on version of CCS), set the PDK_INSTALL_DIR variable in the Environment.3.Right click on the project in the Editor view and Rebuild the project in your CCS environment.4.Load and run the led_play.out file on core 0 of the EVMC6678 to ensure that the rebuilt exampleruns on your EVM. Observe the LED blinks.Task 2: Building the btbl file – boot table format1.Copy the led_play.out file to the build folder2.In spiboot.bat, modify the path to IBL_UTIL to point to the boot utilities provided in the SDK.3.From windows command prompt, execute the spiboot.bat file to generate the boot image in theboot table format4.The details of each step involved in createing the boot image is described in the sections below.NOTE: Since EVM is designed to have FPGA firmware redirect the DSP core to run IBL, for direct SPI boot don`t forget to change the boot address to 0x00 from 0x51 inserted by the romparse utility as described in Section 4Section 1: Create boot table from application binary using Hex6x Utility The RBL expects the image flashed on the SPI flash to be in Boot Table Format. The led_play example application Code has to be first converted into a Boot Table Format, using the hex6x utility present in CCS installation folder. (…\ccsv5\tools\compiler\c6000_7.4.2\bin) (Or a different version of the compiler). The hex6x utility expects an rmd file in which you provide path to the application binary and a format in which the boot table is expected. The documentation for hex6x utility is provided in theTMS320C6000 Assembly Language Tools documentation that is part of the compiler documentation. The hex6x utility reads the sections in the application binary and creates a flat binary in boot Table format that allows the ROM to interpret and load the sections of the application binary. The RMD file contains, few of the following information:-a.The Application.out file that has to be flashed.b.–a for the output hex format in ASCIIc.–e the entry point for the address, i.e. _c_init00d.Output file that contains the application.out in boottable format.e.Memory sections with the MEM and ROW WIDTH1.Create a new directory c:\temp2.Copy the out file from the project to the temp directory that you just created. Note, you cancopy the out file from the debug directory of the project3.Copy hex6x from the bin directory (…\ccsv6\tools\compiler\c6000_7.x.xx\bin) to the tempdirectory4.Open a cmd window and cd it to the temp directory5.Create the rmd file led_play.rmd using notepad or any other editor as follows:led_play.out-a-boot-e _c_int00ROMS{ROM1: org = 0x0C000000, length = 0x100000, memwidth = 32, romwidth = 32files = {led_play.btbl}}6.Run hex6x with led_play.rmd “hex6x led_play.rmd”7.The following is a screen shot of the hex6x run:8.Do dir and notice that the file led_play.btbl was generated9.Note that if you look at the led_play.map map file, and find the text section, you can seethe definition of the section and the length in the btbl file. From the map file:And from the file led_play.btbl:Section 2: Convert to i2c/SPI formatFrom the generated output in previous step which is in the boot table format convert it into the i2c/spi format by passing through the b2i2c.The byte-aligned boot table is then divided into 0x80 byte blocks and appended with length and checksum to adhere to the format required by the RBL, this is generated by passing through the b2i2c utility.The b2i2c utility is part of the MCSDK installation and present in the following folder.mcsdk_2_01_XX_YY\tools\boot_loader\ibl\src\util\btoccsNote: For Processor SDK RTOS users the utilities can be found underpdk_c66xx_2_0_0\packages\ti\boot\ibl\src\util\btoccs1.Copy the b2i2c.exe utility from the release (directory…\MCSDK_2_01_XX\mcsdk_2_01_XX_YY\tools\boot_loader\ibl\src\util\btoccs into the temp directory2.Run b2i2c, specify the input and output file name “b2i2c led_play.btbl led_play.btbl.i2c”3.The screen shot of the run is given below4.Do dir and see that the i2c format file led_play.btbl.i2c was generatedSection 3: Convert to CCS downloaded formatNext the i2c formatted file need to be converted into CCS acceptable .dat format using b2ccs utility present in the mscdk\tools\boot_loader\ibl\src\util\btoccs.1.Copy the b2ccs.exe utility from the release (directory…\MCSDK_2_01_XX\mcsdk_2_01_XX_YY\tools\boot_loader\ibl\src\util\btoccs into the temp directory2.Run b2ccs, specify the input and output file name “b2ccs led_play.btbl.i2c led_s”3.The screen shot of the run is given below4.Do dir and see that the i2c format file led_s was generatedSection 4: Adding Boot parameter TableAn updated boot parameter table is read from the SPI before the actual boot starts. To combine together the boot parameter table and the boot table in the ccs format romparse.exe is used. A *.map file contains the name of the boot table and the values for the boot parameter table. The following shows a standard boot parameter map file:section {boot_mode = 50param_index = 0options = 1core_freq_mhz = 1000exe_file = "led_s"next_dev_addr_ext = 0x0sw_pll_prediv = 5sw_pll_mult = 32sw_pll_postdiv = 2sw_pll_flags = 1addr_width = 24n_pins = 4csel = 0mode = 0c2t_delay = 0bus_freq_mhz = 0bus_freq_khz = 500}1.Copy romparse.exe utility from\MCSDK_2_XX_YY\mcsdk_2_01_XX_YY\tools\boot_loader\ibl\src\util\romparse to the tempdirectory2.Create a map file. You can copy and paste the above file into nysh.spi.map (nysh stands forKeystone I first two families, Nyquist and Shannon). A screen shot is given below3.Run romparse with the map file as a parameter “romparse nysh.spi.map”4.Note that the program romparse hardcoded the name of the output file (s) and the i2caddress into the parameter table that is appended to the boot table.5.The screen shot of the run is given below6.Do dir and see that the i2c format file s was generated7.The program romparse was developed to work with EEPROM connected via i2c. SPI bootprotocol is the same as i2c, except that EEPROM is connected to page 0x51 of the i2c while SPI boot starts from 0. The 0x51 is hard-written into the output file s. The user must change this value into 00. This is done by the following:a.Open the file s with an editor (I use notepad in the screen shots below)b.Change the 51 to 0. The same file will be looked like the following:c.Save the modified fileSection 5: Big Endian formatThe program led_play was built as little endian. The EVM is running as little endian as well, but the RBL always works as big endian. The program byteswapccs swaps the bytes for big endian RBL. The source for byteswapccs.c is given in the Appendix. An executable was built and will be given to the students.1.Create an EXE from byteswapccs.c (This is already done)2.Run byteswapccs.exe with the input file as the s generated at previous step andoutput as the app.dat that will be flashed to the NOR3.The screen shot of the run is given below4.Do dir and see that the big endian file app.dat was generatedTask3: Flash the EVM SPI flash1.Configuring the EVM for CCS NOR flashingFlashing the EVM SPI flash is done using CCS connected to the EVM. The EVM is in no-boot (or sleep) mode. The EVM mode is determined by the setting of four switches on the board, Sw3, SW4, SW5 and SW6. The switches control the following:∙SW3 DSP Boot mode, DSP Configuration∙SW4 DSP boot Configuration∙SW5 DSP boot Configuration∙SW6 DSP boot Configuration, PLL setting, PCIe mode SelectionThe following table is taken from/index.php/TMDXEVM6678L_EVM_Hardware_Setup describes the various mode setting of the EVM:The location of the switched on the EVM for the non-boot case is given by the following pictures.And a close-up of the switches2.The CCS NOR writer is part of the release at locationMCSDK_2_XX_YY\mcsdk_2_01_XX_YY\tools\writer\nor\evmc6678l . The README.txt file (in the \nor\docs directory) gives instructions how to flash the NOR memory. The way the flashdata was developed, some minor modifications to the README.txt file are needed. Thefollowing is the updated instructions:Steps to program the NOR:1. Be sure to set the boot mode dip switch to no boot/EMIF16 boot mode on the EVM.2. Copy app.dat file to writer\nor\evmc66xxl\bin directory3. Change the file_name to app.dat and start_addr to 0 inwriter\nor\evmc66xxl\bin\norwriter_input.txt if necessary. See the screen shot below for the norwrite_input.txt file4. Open CCSv5 and launch the evmc66xx emulator target configuration and connect to core 0.5. Load the program writer\nor\evmc66xxl\bin\norwriter_evm66xxl.out to CCS, be sureevmc66xxl.gel is used in CCS and DDR is initialized. Ignore the red comment that says that it does not find the main() C source.6. Open the Memory view (in CCSv5, view->Memory Browser), and view the memory address0x80000000.7. Load app.dat to 0x80000000:* In CCSv5, right click mouse in memory window, select "load memory".* Browse and select writer\nor\evmc66xxl\bin\app.dat (TI data format), click "next" . See the following screen shot* Set the Start Address to "0x80000000", enter the size of the file. If you check the line “use the file header information to set the start address and size of memory block to be loaded, it will load the file size automatically, see the picture below. Click "finish"8. After the app.dat file is loaded into the memory, run the program (in CCSv5, press F8), it will start to program the NOR.9. When programming is completed, the console will print "NOR programming completed successfully", if there is any error, the console will show the error message.2.The following screen shots shows the nor_writer_input.txt file3.The following screen shoots shows the CCS after loading the memory and the norwriter program4.The next screen shoot shows the console after running the norwriter programTask 6: Boot from NOR SPI1.Power off the EVM, change the EVM switched according to the Boot Mode Dip Switch Settingfrom above - ROM SPI BOOT off, on, off, off on,on,on,on on,on,off,on on,on,on,on . A screen shot of the dip switch is given below2.Power up the EVM. The LED will blink. The last screen shot shows the blinking LED。

ISSPI Support Note 0002Subject: ISSPI 11.11 silently fails to install on OML 9.10 running on RHEL 6.xSeverity: ImportantClassification: Customer viewableAudience: Software Support, ConsultantsRelease history2013/11/04 Original releaseABSTRACTWhen installing the ISSPI 11.11 on the OML management server on RHEL 6.x, the installation script appears to succeed but the ISSPI packages are not installed due to a dependency on /usr/bin/ksh. This support note explains how to identify the problem and fix it. The same problem is expected to exist with earlier versions of ISSPI.PROBLEM STATEMENTWhen installing the ISSPI 11.11 on the OML management server on RHEL 6.x, the installation script appears to succeed:# ./oainstall.sh -i -mINFO: Registering the HP Operations agent packages on the management serverINFO: Backing up the older version of the HP Operations agent packages for theAIX_powerpc32 platformINFO: Backup of the older version of the HP Operations agent packages for theAIX_powerpc32 platform is successful...INFO: Registering the HP Operations agent packages for the OS WININFO: Registration of the HP Operations agent packages for WIN patch is successful INFO: Installing product HPInfraSPIINFO: Installing package HPSpiSysI ....INFO: Installing package HPSpiClI ....INFO: Installing package HPSpiVmI ....INFO: Installing package HPSpiInfG ....INFO: Registering the HP Operations agent packages on the management server is successfulHowever, upon verification, only one package has been installed:# rpm -qa | grep HPSpiHPSpiInfG-11.11.025-1ISSPI policies will be missing in the AdminUI console.The installation logs /var/opt/OV/shared/server/log/oainstall.log will show generic errors: [01/25/13 16:17:43] [OAInstall] [INFO] Invoking command :./scripts/oaproductinstall.pl -i -spiconfig ./scripts/../default_configINFO: Adding bundle path =.//integration/infraspi/LIN/Linux2.6_X64/infraspibundle.xml to the product listINFO: Installing product HPInfraSPIINFO: Found the OM server version to be compatible for integrated productinstallationINFO: Disk space check not yet implementedINFO: Copied /media/HPOvOpsAgt-11.00/integration/infraspi/LIN/Linux2.6_X64/HPSpiSysI.xml/HPSpiSysI.rpm.gz to/var/tmp/HPSpiSysI.rpm.gzINFO: The component package HPSpiSysI extracted successfully.INFO: Installing package HPSpiSysI ....INFO: Installing package through command rpm -i --force /var/tmp/HPSpiSysI.rpm >/dev/null 2>&1ERROR: The component package HPSpiSysI installation failed.INFO: Removing copied file /var/tmp/HPSpiSysI.rpmINFO: Copied /media/HPOvOpsAgt-11.00/integration/infraspi/LIN/Linux2.6_X64/HPSpiClI.xml/HPSpiClI.rpm.gz to/var/tmp/HPSpiClI.rpm.gzINFO: The component package HPSpiClI extracted successfully.INFO: Installing package HPSpiClI ....INFO: Installing package through command rpm -i --force /var/tmp/HPSpiClI.rpm >/dev/null 2>&1ERROR: The component package HPSpiClI installation failed.INFO: Removing copied file /var/tmp/HPSpiClI.rpmINFO: Copied /media/HPOvOpsAgt-11.00/integration/infraspi/LIN/Linux2.6_X64/HPSpiVmI.xml/HPSpiVmI.rpm.gz to/var/tmp/HPSpiVmI.rpm.gzINFO: The component package HPSpiVmI extracted successfully.INFO: Installing package HPSpiVmI ....INFO: Installing package through command rpm -i --force /var/tmp/HPSpiVmI.rpm >/dev/null 2>&1ERROR: The component package HPSpiVmI installation failed.INFO: Removing copied file /var/tmp/HPSpiVmI.rpmINFO: Copied /media/HPOvOpsAgt-11.00/integration/infraspi/LIN/Linux2.6_X64/HPSpiInfG.xml/HPSpiInfG.rpm.gz to/var/tmp/HPSpiInfG.rpm.gzINFO: The component package HPSpiInfG extracted successfully.INFO: Installing package HPSpiInfG ....INFO: Installing package through command rpm -i --force /var/tmp/HPSpiInfG.rpm >/dev/null 2>&1INFO: The component package HPSpiInfG installed successfully.INFO: Removing copied file /var/tmp/HPSpiInfG.rpmINFO: Copying .//integration/infraspi/LIN/Linux2.6_X64/infraspibundle.xml to/opt/OV//bin/OpC/agtinstall/infraspibundle.xmlINFO: Copying /media/HPOvOpsAgt-11.00/scripts/oaproductinstall.pl to/opt/OV//bin/OpC/agtinstall/oaproductinstall.pl[01/25/13 16:17:56] [OAInstall] [INFO] Registering the HP Operations agent packages on the management server is successfulISSPI 2.00 and 11.10 exhibit a similar problem but it has not been checked whether the installation fails silently or produces an error message.SOLUTIONThis problem occurs because the package HPSpiSysI.rpm has a dependency on /usr/bin/ksh, although the file is actually not required for this package. On a RHEL 6.x, the file /usr/bin/ksh is no longer available. Even if you create the file as a symbolic link to /bin/ksh, it will not resolve the dependency, because RPM expects to find that the file was installed by an RPM package:# rpm -q -f /usr/bin/kshfile /usr/bin/ksh is not owned by any packageTo resolve the problem, proceed as follows:NOTE: These steps can be used before or after a failed installation attempt. They are also valid for an upgrade from an older version.1.Copy the ISSPI packages from the depot to a temporary directory# mkdir /tmp/isspi1111# cd/media/HPOvOpsAgt-11.00/integration/infraspi/LIN/Linux2.6_X64# cp HPSpi*.rpm.gz /tmp/isspi1111# cd /tmp/isspi1111# gunzip HPSpi*.rpm.gz# ls -ltotal 2964-r--r--r-- 1 root root 584115 Jan 25 16:22 HPSpiClI.rpm-r--r--r-- 1 root root 35677 Jan 25 16:22 HPSpiInfG.rpm-r--r--r-- 1 root root 1241555 Jan 25 16:22 HPSpiSysI.rpm-r--r--r-- 1 root root 1153267 Jan 25 16:22 HPSpiVmI.rpm2.Confirm the dependency problem# rpm -i --test --force HPSpiSysI.rpmwarning: HPSpiSysI.rpm: Header V3 DSA signature: NOKEY, key ID 2689b887error: Failed dependencies:/usr/bin/ksh is needed by HPSpiSysI-11.11.025-1.x86_64There should be a dependency error about /usr/bin/ksh and only /usr/bin/ksh.If there is no dependency error, you are facing a different problem.If there are more dependency errors, you need to resolve all other dependencies first.3.Install the packages manually# rpm -i --force --nodeps HPSpiSysI.rpmwarning: HPSpiSysI.rpm: Header V3 DSA signature: NOKEY, key ID 2689b887# rpm -i --force HPSpiClI.rpmwarning: HPSpiClI.rpm: Header V3 DSA signature: NOKEY, key ID 2689b887# rpm -i --force HPSpiVmI.rpmwarning: HPSpiVmI.rpm: Header V3 DSA signature: NOKEY, key ID 2689b887# rpm -qa | grep HPSpiHPSpiSysI-11.11.025-1HPSpiVmI-11.11.025-1HPSpiClI-11.11.025-1HPSpiInfG-11.11.025-1Note that you need the --nodeps option only for the package HPSpiSysI.rpm.If you have dependency errors for the other packages, you need to resolve these.If the package HPSpiInfG-11.11.025-1 does not show up in the list, you need to install it manually too:# rpm -i --force HPSpiInfG.rpmwarning: HPSpiInfG.rpm: Header V3 DSA signature: NOKEY, key ID 2689b887 Although you are installing the package manually with rpm, you will still find the installation logs updated in /var/opt/OV/shared/server/log/oainstall.log.BACKGROUND INFORMATIONThe dependency on /usr/bin/ksh is actually not required. It surfaced because RHEL 6 moved ksh out of /usr/bin. See the RHEL 6 Migration Guide:5.4. ShellsThe location of the shell binary files has changed. For example, the bash and ksh binaries are no longerin /usr/bin. Both binaries are now found in /bin. Scripts will require updating to point to the newlocation of the binary.*********************。

![8.1.6 高级配置模式──SPI_Xilinx可编程逻辑器件设计与开发(基础篇)_[共4页]](https://img.taocdn.com/s1/m/1291ed3c172ded630a1cb62b.png)

Xilinx FPGA 的配置模式277 在这个流程中,我们可以看到比较详细的配置细节。

事实上,对于普通用户而言,并不要求掌握如此详细的配置过程,我们也只是在遇到具体的配置问题时才会去分析配置的细节。

8.1.6 高级配置模式──SPI在新一代Xilinx FPGA 中,在原有配置模式的基础上,增加了SPI 与BPI 的配置模式。

串行外设接口(SPI )是一种四线同步串行数据总线。

这种数据链路最初是用作微控制器与外设之间的串行通信接口。

许多现代微控制器都包括内置的 SPI 控制器,以支持众多存储器、传感器、显示驱动器以及模数和数模转换器通信。

这种接口常见于嵌入式和消费市场,现在也可用来配置FPGA 。

SPI 系统通常由一个主器件和至少一个从器件组成。

对于 Spartan-3E 配置,FPGA 是 SPI 主器件,SPI FLASH PROM 是从器件。

SPI 接口使用表8-2所示为4个信号在主从器件之间进行通信。

表8-2 SPI 接口信号 通用 SPI 信号信号描述SCLK“串行时钟”提供串行接口的时钟 MOSI“主出从入”由主器件用来指定要执行的指令或者向从器件传送数据 MISO“主入从出”由主器件用来收集从器件传输的数据 SS_n “从器件选择”,低有效信号;当置为高时,此信号用来反选从器件并将MISO 设置为高阻抗 通用 SPI 接口是标准的全双工接口。

SPI 主器件通过 SCLK 时钟控制所有时序。

在选择信号 SS_n 转为低之后,主器件经 MOSI 引脚将数据由主器件同步输出到从器件。

在同一时钟周期内,主器件接收由从器件同步输出的数据。

数据在一个时钟沿上从源器件同步输出,在该周期内的下一个对沿(opposite edge) 上同步输入目标器件。

图8-17所示为主从器件的典型连接方式。

图8-17 Spartan-3E/A 器件SPI 模式示意图在多个FPGA 需要配置的情况下,SPI 主器件使用片选信号 SS_n 选择从器件。

AN1351: Using the Co-Processor Communication Daemon (CPCd)This application note guides the user through the steps needed to properly configure and run the CPC daemon (CPCd) on Linux or Android. It does not discuss how to use the CPC Library to write applications that interact with CPCd.Introduction 1 IntroductionCo-Processor Communication (CPC) enables one host system to communicate with a Network co-processor device (NCP), also named the secondary device or secondary, by physical transport (UART, SPI, and so on).In CPC, data transfers between processors are segmented in sequential packets. Transfers are guaranteed to be error-free and sent in order. Multiple applications can send or receive on the same endpoint without worrying about collisions.A CPC daemon (CPCd) is provided to allow applications on Linux to interact with a secondary running CPC.The CPC daemon (CPCd) is distributed as three components:•The daemon binary (cpcd)• A library and associated header files that enable C applications to interact with the daemon (libcpc.so)• A configuration file (cpcd.conf)Theory of Operation 2 Theory of OperationCPCd uses Unix sockets configured as sequential packets to transfer data with the Linux host applications. Data is then forwarded to the co-processor over a serial link. The Unix sockets, used to transfer data with applications that use the CPC Library (libcpc.so), are instan-tiated in the /tmp/cpcd folder.. A description of the CPC library usage is out of scope for this application note.Figure 2.1. Co-Processor Communication Overview3 Compiling, Installing, and Configuring CPCd3.1 DownloadingDownload the daemon source files from Silicon Labs GitHub project:https:///SiliconLabs/cpc_daemonThe main branch contains the latest official versions. Early access versions are available in the specific version branches.3.2 Compiling CPCd and the CPC LibraryThe build essential and CMake packages in Linux are required for this step. Compile the CPC daemon in the source folder using the following commands:mkdir buildcd buildcmake ../make3.3 Installing CPCdSuper-user permissions are required to install the daemon, cpclib, and the configuration file. These can be installed with the following commands:make installThe following components will be installed:•/usr/local/lib/libcpc.so.0.1•/usr/local/lib/libcpc.so.1•/usr/local/lib/libcpc.so•/usr/local/include/sl_enum.h•/usr/local/include/sl_cpc.h•/usr/local/bin/cpcd•/etc/cpcd.confOnce installed, CPCd can be executed by invoking the cpcd command.3.4 Configuring CPCdWhen running the daemon without arguments, it starts with the default configuration file installed in the previous step. To specify a different configuration file, use the --conf argument. For example:cpcd --conf <configuration file path>3.5 Obtaining the Version of CPCdIf CPCd is started with the -v or --version argument, the daemon first prints the version of CPCd and exit. For example:cpcd –version3.6 Available ConfigurationsCPCd is configured in a key/value manner in the cpcd.conf file.Table 1.1. CPCd configurationInstance Name INSTANCE_NAME string cpcd_0 NoBus type selection BUS_TYPE UARTSPIUART YesSPI device file SPI_DEVICE_FILE Any path to SPI devicefile/dev/spidev0.0Yes if BUS_TYPE is SPISPI Chip Select GPIO #SPI_CS_GPIO Any GPIO # (1)24Yes if BUS_TYPEis SPISPI RX IRQ GPIO SPI_RX_IRQ_GPIO Any GPIO # (1)23Yes if BUS_TYPEis SPISPI Bitrate SPI_DEVICE_BITRATE Any (2)1000000Yes if BUS_TYPEis SPISPI Mode SPI_DEVICE_MODE SPI_MODE_0 (3)SPI_MODE_1SPI_MODE_2SPI_MODE_3SPI_MODE_0Yes if BUS_TYPEis SPIUART Device File UART_DEVICE_FILE Any (4)/dev/serial0Yes if BUS_TYPEis UARTUART Baud Rate UART_DEVICE_BAUD 1200 (5)24004800192003840057600115200115200Yes if BUS_TYPEis UARTUART Hardware Flow Control UART_HARDFLOW True or false False Yes if BUS_TYPE is UARTTrace to stdout STDOUT_TRACE True or false False No Trace to a file located underTRACES_FOLDER TRACE_TO_FILE True or False False NoDestination folder whenTRACE_TO_FILE is enabled TRACES_FOLDER Any path that the CPCdcan access./cpcd-traces NoThe maximum number of open filedescriptors.RLIMIT_NOFILE Depends on the OS limit 2000No Disable the encryption over CPCendpoints DISABLE_ENCRYPTION True or false False No(1) Make sure the CPC daemon has enough permissions to access this GPIO.(2) This setting depends on various factors. The bitrate needs to satisfy both side requirements.(3) Refer to section 2.6 for additional details.(4) This setting depends on the Linux SOC.(5) These baud rates are typical, but any value that meets both requirements can be used.3.7 Available SPI ModesThe SPI_DEVICE_MODE configuration allows SPI clock polarity and phase to be configured, as shown in the following table.Table 1.2. SPI Mode configurationSPI_MODE_000SPI_MODE_101SPI_MODE_210SPI_MODE_311Troubleshooting 4 TroubleshootingIf an error or a warning occurs during CPCd runtime, it prints to the console STDERR. If additional debugging is required, tracing can be enabled.Note:Enabling traces may impact performance.4.1 Tracing to the Standard Output (stdout)When the configuration STDOUT_TRACE is enabled, the CPC daemon prints traces to the console.4.2 Tracing to a FileWhen the configuration TRACE_TO_FILE is enabled. the CPC daemon prints traces to a file. The tracing file name contains the date and timestamp. This file is placed in the folder specified in the configuration TRACES_FOLDER.The trace file has the following format:trace-<year>-<month>-<day>-<hour>-<minute>-<second>.txtThe timestamp uses the operating system’s local time zone.Note:Only enable tracing to a file when debugging, as log file size increases over time.Considerations 5 Considerations•The SPI driver uses a sysfs class GPIO as a chip select. Make sure the daemon has the proper permissions to access this GPIO. •If the provided GPIO for the SPI chip select is already used by another driver, it needs to be deactivated and enabled as standard GPIO. In Linux this is usually done via the device tree.•CPCd uses Unix sockets to exchange information with the Linux applications that use the CPC library. These sockets are stored under /etc/cpcd. Only users with the appropriate permissions should be able to access these sockets. CPCd inherits the permission of the user who starts the CPC daemon.•Make sure no other application is using the serial bus at the same time as CPCd.•Sensitive information can be exposed when tracing to a file is enable. Only enable tracing during development, for debugging purposes only. Refer to the TRACE_TO_FILE and STDOUT_TRACE configurations.Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USAIoT Portfolio/IoTSW/HW/simplicityQuality /qualitySupport & Community/communityDisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software imple-menters using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and “Typical” parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the infor -mation supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A “Life Support System” is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs product in such unauthorized applications. Note: This content may contain offensive terminology that is now obsolete. Silicon Labs is replacing these terms with inclusive language wherever possible. For more information, visit /about-us/inclusive-lexicon-projectTrademark InformationSilicon Laboratories Inc.®, Silicon Laboratories ®, Silicon Labs ®, SiLabs ® and the Silicon Labs logo ®, Bluegiga ®, Bluegiga Logo ®, EFM ®, EFM32®, EFR, Ember ®, Energy Micro, Energy Micro logo and combinations thereof, “the world’s most energy friendly microcontrollers”, Redpine Signals ®, WiSeConnect , n-Link, ThreadArch ®, EZLink ®, EZRadio ®, EZRadioPRO ®, Gecko ®, Gecko OS, Gecko OS Studio, Precision32®, Simplicity Studio ®, Telegesis, the Telegesis Logo ®, USBXpress ® , Zentri, the Zentri logo and Zentri DMS, Z-Wave ®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.。

TRISPI参数设置解释TRI SPI是一种串行外设接口协议,用于连接主机和外设设备,实现数据传输和通信。

它是由Texas Instruments公司开发的,用于其DSP处理器和模拟设备之间的通信。

下面将详细介绍TRI SPI参数设置的含义和作用。

1. 时钟速率(Clock Rate):时钟速率是指传输数据的速度,用时钟周期(Clock cycle)来衡量。

它决定了数据传输的速度和带宽。

时钟速率越高,数据传输速度越快,但也会增加功耗和噪声。

时钟速率需要根据外设的能力和主机的处理能力来设置,并且通常需要在外设和主机之间协商一个合适的速率。

2. 时钟相位和极性(Clock Phase and Polarity):时钟相位和极性确定了时钟信号的起始位置和传输数据的时机。

时钟相位(Clock phase)可以设置为0或1,用于指定数据采样的时机。

时钟极性(Clock polarity)可以设置为低电平(CPOL=0)或高电平(CPOL=1),用于指定时钟信号的起始电平。

时钟相位和极性需要主机和外设之间预先约定并设置一致,以保证数据的正确传输。

3. 数据位数(Data Bits):数据位数指定每个数据帧(Data frame)中数据信号的位数。

常见的设置为8位,即每个数据帧由8位二进制数组成。

数据位数需要与外设和主机之间预先约定并设置一致,以保证数据的正确传输。

4. 电平转换(Voltage Translation):电平转换用于将SPI总线上的电平转换为外设所需要的电平。

SPI总线的电平通常为0V和5V,而外设可能需要不同的电平。

因此,在连接外设之前,需要根据外设的电平需求进行电平转换。

电平转换可以通过逻辑电平转换器或电平转换电路实现。

5. 传输模式(Transfer Mode):传输模式指定SPI总线的工作方式,有两种常见的模式:主模式(Master mode)和从模式(Slave mode)。

在主模式下,主机控制总线上的时钟信号和数据传输;而在从模式下,外设被动接收主机发送的时钟和数据。

华邦W25Q16存储器颗粒SPI编程W25X16、W25X32 和W25X64 系列FLASH 存储器可以为用户提供存储解决方案,具有“PCB 板占用空间少”、“引脚数量少”、“功耗低”等特点。

与普通串行FLASH 相比,使用更灵活,性能更出色。

它非常适合做代码下载应用,例如存储声音,文本和数据。

工作电压在 2.7V-3.6V 之间,正常工作状态下电流消耗0.5 毫安,掉电状态下电流消耗 1 微安。

所有的封装都是"节省空间"型的。

W25X16、W25X32 和W25X64 分别有8192、16384 和32768 可编程页,每页256 字节。

用"页编程指令"每次就可以编程256个字节。

用"扇区(sector)擦除指令"每次可以擦除16 页,用“块(block)擦除指令”每次可以擦除256 页,用“整片擦除指令”即可以擦除整个芯片。

W25X16、W25X32 和W25X64 分别有512、1024 和2048 个可擦除"扇区"或32、64 和128 个可擦除“块”。

W25X16、W25X32 和W25X64 支持标准的SPI 接口,传输速率最大75MHz。

四线制:①:串行时钟引脚CLK;①:芯片选择引脚CS;①:串行数据输出引脚DO;①:串行数据输入输出引脚DIO。

(注意:第①引脚“串行数据输入输出引脚DIO”的解释:在普通情况下,这根引脚是“串行输入引脚(DI),当使用了快读双输出指令(Fast Read Dual Output instruction)时,这根引脚就变成了DO 引脚,这种情况下,芯片就有了两个DO 引脚了,所以叫做双输出,这时,如果与芯片通信的速率相当于翻了一倍,所以传输速度更快。

)另外,芯片还具有保持引脚(HOLD)、写保护引脚(WP)、可编程写保护位(位于状态寄存器bit1)、顶部和底部块的控制等特征,使得控制芯片更具灵活性。

6 回复 最新回复: 2014-11-9 下午11:23 Arulpandiyan Vadivel分支到新 讨论.How to enable spidev forall SPI (1-5) for MX6此问题已回答。

Hi,We are currently trying to enable the spidev driver for the5 SPI interfaces on the MX6 nitrogen board under Linux.For now, I was having some problem adding SPI 2-5 intomy configuration.We are using Yocto with the kernel 3.0.35.I enable the user mode interface in “menuconfig” andmodify the following filehttps:///boundarydevices/linux-imx6/blob/boundary-L3.0.35_MX6DQ_ER_1208-Beta/arch/arm/mach-mx6/board-mx6q_sabrelite.cstatic struct spi_board_infoimx6_sabrelite_spi_nor_device[] __initdata = {#if defined(CONFIG_MTD_M25P80){.modalias = "spidev ",.max_speed_hz = 20000000, /* max spi clock (SCK)speed in HZ */.bus_num = 0,.chip_select = 0,.platform_data = &imx6_sabrelite__spi_flash_data,},#endif};Just by changing the driver name to spidev, I can boot andsee the spidev interface under /dev/.I tried to add the pads for the ecspi2 interface and modifythe bus_num to 1 to try to access the second SPI. After acouple of days with multiple attempts, I was still not able toget the spidev1.0 interface .I was hoping someone can point us to some gooddocumentation regarding the modifications required toenable the other SPI interfaces (2 to 5) under linux for themx6.patrice sarrasin 2012-12-11 上午6:42Let me know if you need anything else in order to assist.Best regardsPatrice正确答案作者:patrice sarrasin开启 2013-1-17 上午11:25Hi,I was finally able to figure out how to make this thingwork. For others that could have the same problem, hereis the code of the patch I made.Index: git/arch/arm/mach-mx6/board-mx6q_sabrelite.c=================================================================== --- git.orig/arch/arm/mach-mx6/board-mx6q_sabrelite.c2012-12-19 11:40:56.461028612 -0500+++ git/arch/arm/mach-mx6/board-mx6q_sabrelite.c2012-12-19 15:06:35.913464999 -0500@@ -79,6 +79,8 @@#define MX6Q_SABRELITE_SD4_CDIMX_GPIO_NR(2, 6)#define MX6Q_SABRELITE_SD4_WPIMX_GPIO_NR(2, 7)#define MX6Q_SABRELITE_ECSPI1_CS1IMX_GPIO_NR(3, 19)+#define MX6Q_SABRELITE_ECSPI2_CS0IMX_GPIO_NR(5, 12)+#define MX6Q_SABRELITE_ECSPI3_CS0IMX_GPIO_NR(4, 24)#define MX6Q_SABRELITE_USB_OTG_PWRIMX_GPIO_NR(3, 22)#define MX6Q_SABRELITE_CAP_TCH_INT1IMX_GPIO_NR(1, 9)#define MX6Q_SABRELITE_USB_HUB_RESETIMX_GPIO_NR(7, 12)@@ -132,6 +134,18 @@MX6Q_PAD_EIM_D16__ECSPI1_SCLK,MX6Q_PAD_EIM_D19__GPIO_3_19, /*SS1*/+ /* ECSPI2 */+ MX6Q_PAD_DISP0_DAT17__ECSPI2_MISO,+ MX6Q_PAD_DISP0_DAT16__ECSPI2_MOSI,+ MX6Q_PAD_DISP0_DAT19__ECSPI2_SCLK,+ MX6Q_PAD_DISP0_DAT18__GPIO_5_12, /*SS0*/++ /* ECSPI3 */+ MX6Q_PAD_DISP0_DAT2__ECSPI3_MISO,+ MX6Q_PAD_DISP0_DAT1__ECSPI3_MOSI,+ MX6Q_PAD_DISP0_DAT0__ECSPI3_SCLK,+ MX6Q_PAD_DISP0_DAT3__GPIO_4_24, /*SS0*/ +/* ENET */MX6Q_PAD_ENET_MDIO__ENET_MDIO,MX6Q_PAD_ENET_MDC__ENET_MDC,@@ -221,12 +235,12 @@#endif/* DISPLAY */- MX6Q_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK, +/*MX6Q_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK, MX6Q_PAD_DI0_PIN15__IPU1_DI0_PIN15, /* DE */ - MX6Q_PAD_DI0_PIN2__IPU1_DI0_PIN2, /* HSync */ - MX6Q_PAD_DI0_PIN3__IPU1_DI0_PIN3, /* VSync */ - MX6Q_PAD_DI0_PIN4__IPU1_DI0_PIN4, /* Contrast */- MX6Q_PAD_DISP0_DAT0__IPU1_DISP0_DAT_0,+/* MX6Q_PAD_DI0_PIN2__IPU1_DI0_PIN2, /* HSync */+/* MX6Q_PAD_DI0_PIN3__IPU1_DI0_PIN3, /* VSync */+/* MX6Q_PAD_DI0_PIN4__IPU1_DI0_PIN4, /* Contrast */+/* MX6Q_PAD_DISP0_DAT0__IPU1_DISP0_DAT_0, MX6Q_PAD_DISP0_DAT1__IPU1_DISP0_DAT_1,MX6Q_PAD_DISP0_DAT2__IPU1_DISP0_DAT_2,MX6Q_PAD_DISP0_DAT3__IPU1_DISP0_DAT_3,@@ -251,8 +265,8 @@MX6Q_PAD_DISP0_DAT22__IPU1_DISP0_DAT_22, MX6Q_PAD_DISP0_DAT23__IPU1_DISP0_DAT_23, MX6Q_PAD_GPIO_7__GPIO_1_7, /* J7 - Display Connector GP */- MX6Q_PAD_GPIO_9__GPIO_1_9, /* J7 - Display Connector GP */- MX6Q_PAD_NANDF_D0__GPIO_2_0, /* J6 - LVDS Display contrast */+/* MX6Q_PAD_GPIO_9__GPIO_1_9, /* J7 - Display Connector GP */+/* MX6Q_PAD_NANDF_D0__GPIO_2_0, /* J6 - LVDS Display contrast *//* PWM1 */@@ -469,13 +483,22 @@.phy = PHY_INTERFACE_MODE_RGMII,};-static int mx6q_sabrelite_spi_cs[] = {- MX6Q_SABRELITE_ECSPI1_CS1,+static int mx6q_sabrelite_spi_cs2[] = {+ MX6Q_SABRELITE_ECSPI2_CS0,+};+static const struct spi_imx_mastermx6q_sabrelite_spi_data2 __initconst = {+ .chipselect = mx6q_sabrelite_spi_cs2,+ .num_chipselect =ARRAY_SIZE(mx6q_sabrelite_spi_cs2),};-static const struct spi_imx_mastermx6q_sabrelite_spi_data __initconst = {- .chipselect = mx6q_sabrelite_spi_cs,- .num_chipselect =ARRAY_SIZE(mx6q_sabrelite_spi_cs),+static int mx6q_sabrelite_spi_cs3[] = {+ MX6Q_SABRELITE_ECSPI3_CS0,+};++static const struct spi_imx_mastermx6q_sabrelite_spi_data3 __initconst = {+ .chipselect = mx6q_sabrelite_spi_cs3,+ .num_chipselect =ARRAY_SIZE(mx6q_sabrelite_spi_cs3),};#if defined(CONFIG_MTD_M25P80) ||defined(CONFIG_MTD_M25P80_MODULE)@@ -489,7 +512,7 @@.name = "kernel",.offset = MTDPART_OFS_APPEND,.size = MTDPART_SIZ_FULL,- },+ },};static struct flash_platform_dataimx6_sabrelite__spi_flash_data = {@@ -503,11 +526,20 @@static struct spi_board_infoimx6_sabrelite_spi_nor_device[] __initdata = {#if defined(CONFIG_MTD_M25P80){- .modalias = "m25p80",+ .modalias = "spidev",.max_speed_hz = 20000000, /* max spi clock (SCK) speed in HZ */- .bus_num = 0,+ .bus_num = 1,.chip_select = 0,- .platform_data = &imx6_sabrelite__spi_flash_data,+ .mode = SPI_MODE_0,+ /*.platform_data = &imx6_sabrelite__spi_flash_data,*/ + },5133 查看标签: linux-kernel , linux-os , spi , mx6 , mx6q分类: i.MX6D , i.MX6Q , i.MX6_All , Linux , i.MX6SL ,i.MX6DL , i.MX6S平均用户评级(0 评级)+ .modalias = "spidev",+ .max_speed_hz = 20000000, /* max spi clock (SCK)speed in HZ */+ .bus_num = 2,+ .chip_select = 0,+ .mode = SPI_MODE_0,+ /*.platform_data = &imx6_sabrelite__spi_flash_data,*/},#endif};@@ -1144,12 +1176,12 @@mx6q_sabrelite_init_uart();imx6q_add_mxc_hdmi_core(&hdmi_core_data);- imx6q_add_ipuv3(0, &ipu_data[0]);+ /*imx6q_add_ipuv3(0, &ipu_data[0]);imx6q_add_ipuv3(1, &ipu_data[1]);for (i = 0; i < ARRAY_SIZE(sabrelite_fb_data); i++)imx6q_add_ipuv3fb(i, &sabrelite_fb_data[i]);-+*/imx6q_add_vdoa();imx6q_add_lcdif(&lcdif_data);imx6q_add_ldb(&ldb_data);@@ -1172,7 +1204,8 @@ARRAY_SIZE(mxc_i2c2_board_info));/* SPI */- imx6q_add_ecspi(0, &mx6q_sabrelite_spi_data);+ imx6q_add_ecspi(1, &mx6q_sabrelite_spi_data2);+ imx6q_add_ecspi(2, &mx6q_sabrelite_spi_data3);spi_device_init();imx6q_add_mxc_hdmi(&hdmi_data);Re: How to enable spidev for all SPI (1-5) for正确答案patrice sarrasin 2013-1-17 上午11:25 (回复 patrice sarrasin )Hi,I was finally able to figure out how to make this thingwork. For others that could have the same problem, here isthe code of the patch I made.Index: git/arch/arm/mach-mx6/board-mx6q_sabrelite.c=================================================================== --- git.orig/arch/arm/mach-mx6/board-mx6q_sabrelite.c2012-12-19 11:40:56.461028612 -0500+++ git/arch/arm/mach-mx6/board-mx6q_sabrelite.c 2012-12-19 15:06:35.913464999 -0500@@ -79,6 +79,8 @@#define MX6Q_SABRELITE_SD4_CD IMX_GPIO_NR(2,6)#define MX6Q_SABRELITE_SD4_WP IMX_GPIO_NR(2,7)#define MX6Q_SABRELITE_ECSPI1_CS1IMX_GPIO_NR(3, 19)+#define MX6Q_SABRELITE_ECSPI2_CS0IMX_GPIO_NR(5, 12)+#define MX6Q_SABRELITE_ECSPI3_CS0IMX_GPIO_NR(4, 24)#define MX6Q_SABRELITE_USB_OTG_PWRIMX_GPIO_NR(3, 22)#define MX6Q_SABRELITE_CAP_TCH_INT1IMX_GPIO_NR(1, 9)#define MX6Q_SABRELITE_USB_HUB_RESETIMX_GPIO_NR(7, 12)@@ -132,6 +134,18 @@MX6Q_PAD_EIM_D16__ECSPI1_SCLK,MX6Q_PAD_EIM_D19__GPIO_3_19, /*SS1*/+ /* ECSPI2 */+ MX6Q_PAD_DISP0_DAT17__ECSPI2_MISO,+ MX6Q_PAD_DISP0_DAT16__ECSPI2_MOSI,+ MX6Q_PAD_DISP0_DAT19__ECSPI2_SCLK,+ MX6Q_PAD_DISP0_DAT18__GPIO_5_12, /*SS0*/++ /* ECSPI3 */+ MX6Q_PAD_DISP0_DAT2__ECSPI3_MISO,+ MX6Q_PAD_DISP0_DAT1__ECSPI3_MOSI,+ MX6Q_PAD_DISP0_DAT0__ECSPI3_SCLK,+ MX6Q_PAD_DISP0_DAT3__GPIO_4_24, /*SS0*/+/* ENET */MX6Q_PAD_ENET_MDIO__ENET_MDIO,MX6Q_PAD_ENET_MDC__ENET_MDC,@@ -221,12 +235,12 @@#endif/* DISPLAY */- MX6Q_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK, +/* MX6Q_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK, MX6Q_PAD_DI0_PIN15__IPU1_DI0_PIN15, /* DE */- MX6Q_PAD_DI0_PIN2__IPU1_DI0_PIN2, /* HSync */ - MX6Q_PAD_DI0_PIN3__IPU1_DI0_PIN3, /* VSync */ - MX6Q_PAD_DI0_PIN4__IPU1_DI0_PIN4, /* Contrast */ - MX6Q_PAD_DISP0_DAT0__IPU1_DISP0_DAT_0,+/* MX6Q_PAD_DI0_PIN2__IPU1_DI0_PIN2, /* HSync */ +/* MX6Q_PAD_DI0_PIN3__IPU1_DI0_PIN3, /* VSync */ +/* MX6Q_PAD_DI0_PIN4__IPU1_DI0_PIN4, /* Contrast */+/* MX6Q_PAD_DISP0_DAT0__IPU1_DISP0_DAT_0,MX6Q_PAD_DISP0_DAT1__IPU1_DISP0_DAT_1,MX6Q_PAD_DISP0_DAT2__IPU1_DISP0_DAT_2,MX6Q_PAD_DISP0_DAT3__IPU1_DISP0_DAT_3,@@ -251,8 +265,8 @@MX6Q_PAD_DISP0_DAT22__IPU1_DISP0_DAT_22, MX6Q_PAD_DISP0_DAT23__IPU1_DISP0_DAT_23, MX6Q_PAD_GPIO_7__GPIO_1_7, /* J7 - Display Connector GP */- MX6Q_PAD_GPIO_9__GPIO_1_9, /* J7 - Display Connector GP */- MX6Q_PAD_NANDF_D0__GPIO_2_0, /* J6 - LVDS Display contrast */+/* MX6Q_PAD_GPIO_9__GPIO_1_9, /* J7 - Display Connector GP */+/* MX6Q_PAD_NANDF_D0__GPIO_2_0, /* J6 - LVDS Display contrast *//* PWM1 */@@ -469,13 +483,22 @@.phy = PHY_INTERFACE_MODE_RGMII,};-static int mx6q_sabrelite_spi_cs[] = {- MX6Q_SABRELITE_ECSPI1_CS1,+static int mx6q_sabrelite_spi_cs2[] = {+ MX6Q_SABRELITE_ECSPI2_CS0,+};++static const struct spi_imx_mastermx6q_sabrelite_spi_data2 __initconst = {+ .chipselect = mx6q_sabrelite_spi_cs2,+ .num_chipselect =ARRAY_SIZE(mx6q_sabrelite_spi_cs2),};-static const struct spi_imx_mastermx6q_sabrelite_spi_data __initconst = {- .chipselect = mx6q_sabrelite_spi_cs,- .num_chipselect =ARRAY_SIZE(mx6q_sabrelite_spi_cs),+static int mx6q_sabrelite_spi_cs3[] = {+ MX6Q_SABRELITE_ECSPI3_CS0,+};++static const struct spi_imx_mastermx6q_sabrelite_spi_data3 __initconst = {+ .chipselect = mx6q_sabrelite_spi_cs3,+ .num_chipselect =ARRAY_SIZE(mx6q_sabrelite_spi_cs3),};#if defined(CONFIG_MTD_M25P80) ||defined(CONFIG_MTD_M25P80_MODULE)@@ -489,7 +512,7 @@.name = "kernel",.offset = MTDPART_OFS_APPEND,.size = MTDPART_SIZ_FULL,- },+ },};static struct flash_platform_dataimx6_sabrelite__spi_flash_data = {@@ -503,11 +526,20 @@static struct spi_board_infoimx6_sabrelite_spi_nor_device[] __initdata = {#if defined(CONFIG_MTD_M25P80){- .modalias = "m25p80",+ .modalias = "spidev",.max_speed_hz = 20000000, /* max spi clock (SCK) speed in HZ */- .bus_num = 0,+ .bus_num = 1,.chip_select = 0,- .platform_data = &imx6_sabrelite__spi_flash_data,+ .mode = SPI_MODE_0,+ /*.platform_data = &imx6_sabrelite__spi_flash_data,*/ + },+ {+ .modalias = "spidev",+ .max_speed_hz = 20000000, /* max spi clock (SCK) speed in HZ */+ .bus_num = 2,+ .chip_select = 0,+ .mode = SPI_MODE_0,+ /*.platform_data = &imx6_sabrelite__spi_flash_data,*/ },#endif};@@ -1144,12 +1176,12 @@mx6q_sabrelite_init_uart();imx6q_add_mxc_hdmi_core(&hdmi_core_data);- imx6q_add_ipuv3(0, &ipu_data[0]);+ /*imx6q_add_ipuv3(0, &ipu_data[0]);imx6q_add_ipuv3(1, &ipu_data[1]);for (i = 0; i < ARRAY_SIZE(sabrelite_fb_data); i++)imx6q_add_ipuv3fb(i, &sabrelite_fb_data[i]);-+*/imx6q_add_vdoa();imx6q_add_lcdif(&lcdif_data);imx6q_add_ldb(&ldb_data);@@ -1172,7 +1204,8 @@ARRAY_SIZE(mxc_i2c2_board_info));/* SPI */- imx6q_add_ecspi(0, &mx6q_sabrelite_spi_data);+ imx6q_add_ecspi(1, &mx6q_sabrelite_spi_data2);+ imx6q_add_ecspi(2, &mx6q_sabrelite_spi_data3);spi_device_init();imx6q_add_mxc_hdmi(&hdmi_data);喜爱 (0)Niklas Molin2013-9-19 下午3:26 (回复 patrice sarrasin)Re: How to enable spidev for all SPI (1-5) for MX6Hi Patrice.How did you manage to get the device driver to showup in the /dev directory?I'm using the LTIB image and I can see that thespi_imx driver has started (in /proc/iomem and/proc/interrupts), but I can't figure out how to call it?I also tried to change the alias to spidev, but it didn'tdo anything.How do I access this driver from my application code?Thanks,Niklas喜爱 (0) patrice sarrasin2013-10-3 上午10:41 (回复 Niklas MolinRe: How to enable spidev for all SPI (1-5) forMX6Hi,if you did all the configuration correctly, youshould see the device appear in /dev/. It should besomething like /dev/spidev0.0 or another numberdepending on which SPI you are trying to enable.Also be sure you enable the option"CONFIG_SPI_SPIDEV=y" in your kernelregardsPatrice喜爱 (0)Re: How to enable spidev for all SPI (1-5)for MX6Hi Patrice.Thanks for the update.I have just switched from LTIB to YOCTO(seems like LTIB is not going to be supportedany longer).I just wanted to check which file this defineshould be included (to enable the option in thekernel)?Regards,Niklas喜爱 (0)Niklas Molin2013-10-30 下午6:05 (回复 patrice sarrasinRe: How to enable spidev for all SPI (1-5) for MX6Hi Patrice.How do you make the board-mx6q_sabrelite.c file tonot me change during the compile?I try to do some updates in this file. But after a compileI can see that the compiler has updated this file withthe original file.Regards,Niklas Molin2013-11-1 上午11:16 (回复 patrice sarrasin)2015年3月10日How to enable spidev for all SPI (1-5) for MX6 | Freescale Communityhttps:///message/312306#31230611/11© 2007-2012 Jive Software |Terms of Use |Trademarks |Privacy |Agreement |Newsletter|Browser Compatibility © Freescale, Inc. 2004 - 2014. All Rights Reserved.Niklas喜爱 (0)Re: How to enable spidev for all SPI (1-5) for MX6Hi patrice,As my source and your base source are mismatching,can you please share the updated source code ofarch/arm/mach-mx6/board-mx6q_sabrelite.c. Thanksin advance.RegardsArulpandiyan Vadivel喜爱 (0)Arulpandiyan Vadivel 2014-11-9 下午11:23 (回复 patrice sarrasin。