基于CPLD的中文字符显示的设计与实现

- 格式:doc

- 大小:23.50 KB

- 文档页数:5

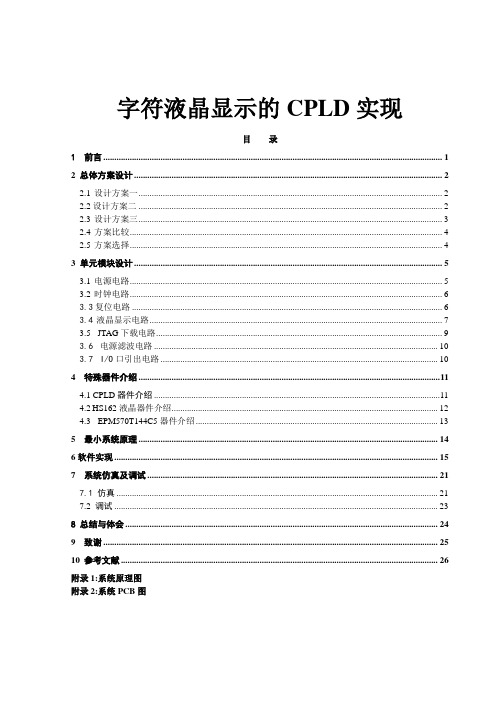

字符液晶显示的CPLD实现目录1 前言 (1)2 总体方案设计 (2)2.1设计方案一 (2)2.2设计方案二 (2)2.3设计方案三 (3)2.4方案比较 (4)2.5方案选择 (4)3 单元模块设计 (5)3.1电源电路 (5)3.2时钟电路 (6)3.3复位电路 (6)3.4液晶显示电路 (7)3.5JTAG下载电路 (9)3.6电源滤波电路 (10)3.7I/O口引出电路 (10)4 特殊器件介绍 (11)4.1 CPLD器件介绍 (11)4.2HS162液晶器件介绍 (12)4.3EPM570T144C5器件介绍 (13)5 最小系统原理 (14)6软件实现 (15)7 系统仿真及调试 (21)7.1 仿真 (21)7.2 调试 (23)8 总结与体会 (24)9 致谢 (25)10 参考文献 (26)附录1:系统原理图附录2:系统PCB图1 前言EDA是电子设计自动化(Electronic Design Automation)缩写,是90年代初从CAD(计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅助测试)和CAE(计算机辅助工程)的概念发展而来的。EDA技术是以计算机为工具,根据硬件描述语言HDL( Hardware Description language)完成的设计文件,自动地完成逻辑编译、化简、分割、综合及优化、布局布线、仿真以及对于特定目标芯片的适配编译和编程下载等工作。硬件描述语言HDL是相对于一般的计算机软件语言,如:C、PASCAL而言的。HDL语言使用与设计硬件电子系统的计算机语言,它能描述电子系统的逻辑功能、电路结构和连接方式。设计者可利用HDL程序来描述所希望的电路系统,规定器件结构特征和电路的行为方式;然后利用综合器和适配器将此程序编程能控制FPGA和CPLD内部结构,并实现相应逻辑功能的的门级或更底层的结构网表文件或下载文件。目前,就FPGA/CPLD开发来说,比较常用和流行的HDL主要有ABEL-HDL、AHDL和VHDL。目前的EDA产业正处在一场大变革的前夕,对更低成本、更低功耗的无止境追求和越来越短的产品上市压力正迫使IC供应商提供采用0.13μm或以下的千万门级的系统芯片,而这些系统芯片的高复杂性设计更加依赖于EDA供应商提供全新的设计工具和方法以实现模拟前后端、混合信号和数字电路的完全整合。然而,这些新的需求为当代EDA工具和设计方法带来了不少新的挑战与机会。例如,如何在工艺上防止模拟电路与数字电路之间的干扰;现有的大部份EDA工具最多只能处理百万门级设计规模,随着IC设计向千万门级以上规模发展,现有EDA工具和方法必须进行升级。如何融合各EDA供应商的工具,以便向IC设计界提供更高效能和更方便的RTL-to-GDSII或Conc-ept-to-GDSII整合设计环境;为保证深亚微米(0.13μm或以下)和更低内核工作电压(1.8V或以下)时代的信号完整性和设计时序收敛,必须采用新的设计方法。本设计利用CPLD控制字符液晶实现字符的显示。字符液晶由液晶显示器和专用的行,列驱动器,控制器及必要的连接件装配而成,可显示数字和英文字符。由CPLD作为控制芯片,通过VreilogHDL硬件描述语言设计,运用自顶而下的设计思想,按功能逐层分割实现层次化的设计。然后通过quartusⅡ软件进行仿真验证。2 总体方案设计2.1 设计方案一由单片机AT89S52来实现字符液晶显示。图2-1 利用单片机实现液晶显示硬件原理图方案一的原理简述:该方案是用单片机AT89S52来实现字符液晶显示。通过编程实现对单片机的控制,显示出想要显示出来的字符。 2.2设计方案二采用FPGA 器件实现液晶显示。图2-2 FPGA 液晶显示的框架结构图晶振RS485电源FPGA电平转换列驱动器电平转换行驱动器LCDPC方案二的原理简述:FPGA主要是指采用四输入查找表(LUT4)的基于SRAM的器件,因为SRAM是挥发的,掉电丢失数据,所以FPGA需要外部配置ROM,上电的时候,从外部的ROM把FPGA的配置数据导入到FPGA芯片内部后工作。具有SRAM的FPGA采用标准的CMOS制造工艺,可以随着最新的工艺而更新还代,给用户带来了实惠;衡量FPGA 容量的一个基本指标是逻辑单元(Logic cell或者Logic element),由一个可编程得LUT4和一个可编程的DFF组成,LUT4完成组合逻辑功能,而DFF用来实现时序功能。FPGA的容量从几千的逻辑单元到几十万的逻辑单元不等。如Altera的Cyclone/II/III和Stratix/II/II 系列芯片,Xilinx Spartan3/3E/3A/3AN和Virtex4/5系列芯片都是FPGA器件。在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FPGA可在逻辑门下编程,而CPLD是在逻辑块下编程。2.3 设计方案三基于复杂可编程逻辑器件CPLD,通过EDA技术,采用VerilogHDL硬件描述语言实现液晶显示。图2-3 CPLD与字符液晶HS162的接口典型电方案三的原理简述:液晶显示器件(LCD)是一种平板薄型显示器件,它的驱动电压很低、工作电流极小。它是一种专门用来显示字母、数字、符号等的点阵型液晶模块,它由32个5*8点阵字符位组成,每一个点阵字符位都可以显示一个字符,但是它不能显示图形。模块内部自带有160个5*8点阵字型的字符发生器CHROM和8个可由用户自定义的5*8的字符发生器CGRAM。本次设计原理图如图2-3所示:D0-D7为传给液晶的数据(可能为显示数字或控制液晶指令),RS用于控制将D0-D7的数据写入指令寄存器还是数据寄存器,RW为读写控制信号,E为使能信号。电位器调节液晶的对比度,以到最佳显示效果。2.4 方案比较通过方案一二三的比较,可以看出方案一的设计使用分立元件电路较为多,因此会增加电路调试难度,且电路的不稳定性也会随之增加,而采用CPLD芯片实现的电路,由于在整体性上较好,在信号的处理和整个系统的控制中,CPLD的方案能大大缩减电路的体积,提高电路的稳定性。此外其先进的开发工具使整个系统的设计调试周期大大缩短,一般来讲,同样的逻辑,基于FPGA要比基于单片机要快很多,因为它们工作的原理是完全不同的。单片机是基于指令工作的,同样的激励到达单片机后,单片机首先要判断,然后读取相应的指令,最后作出相应,这每一步都是需要在单片机的时钟驱动下一步步的进行。而基于FPGA则是把相应的逻辑“暂时”固化为硬件电路了,它对激励作出的响应速度就是电信号从FPGA的一个管脚传播另一个管脚的传播速度,当然这指的是异步逻辑,同时电信号也要在芯片内进行一些栅电容的充放电动作,但这些动作都是非常非常快的。本次设计不是很复杂,也不需要大量LE,但CPLD比FPGA更加适合编程调试,FPGA的价格也是CPLD倍数。2.5 方案选择在现代SOC技术的引领下,人们对低故障、高实时、高可靠、高稳定的性能更加青睐,结合本设计的要求及综合以上比较的情况,我们选择了基于CPLD的液晶显示方案三。3 单元模块设计本设计由CPLD 作为控制芯片,通过VreilogHDL 硬件描述语言设计,运用自顶而下的设计思想,按功能逐层分割实现层次化的设计。下面介绍主要模块的功能及作用。 3.1 电源电路电源采用集成稳压电路 ,器件用LM 7805 ,三端式集成稳压器的输出电压是固定的,在使用中不能进行调整,固定正电压输出。滤波器电容一般采用几百~几千微法。当稳压器距离整流滤波电路比较远时,再输入端必须接入电容器,以抵消电路的电感效应,防止产生自激震荡,输出电容用以滤除输出端的高频信号,改善电路的瞬态响应。P1输入8到12V 的直流电压,输入的直流电压通过一个保护二极管后,通过一个三端集成稳压器LM7805得到一个5V 的直流电源,将此时的输出电压再经过一次电容滤波,得到一个稳定的+5V 直流电源输出。图3-1为电源电路图。图3-1 5V 电源电路采用LM1117-3.3稳压芯片进行3.3V电压设计,设计电路简单,纹波比较小。其典型应用如下所示:VC V图3-2 3.3V 电源电路由图3-1中输出的5V直流电压作为输入电压,经过稳压器件LM1117-3.3变换后,经过滤波电容滤波后得到3.3V稳定的直流电源。D401做为电源指示灯的作用,灯亮表示输出电压正常。3.2 时钟电路一般常用的CPLD中常用的振荡器有石英晶体振荡器和有源晶振。本次设计才用MAXII的EPM570T144C5进行设计,由于设计芯片中没有PLL,所以要想实现高速设计,必须采用高频时钟源,因此只有采用有源晶振才能得到可靠的时钟源。本次设计中采用了,两个时钟源,一个作为平常使用,另外一个作为备用时钟源。时钟电路如下图所示:(a) (b)图3-3 晶振电路图3-3中的电容均为滤波作用,使晶振的电源更加稳定。电阻的作用都是为了使电路阻抗匹配。3.3复位电路为确保微机系统中电路稳定可靠工作,复位电路是必不可少的一部分,复位电路的第一功能是上电复位。一般微机电路正常工作需要供电电源为5V±5%,即4.75~5.25V。由于微机电路是时序数字电路,它需要稳定的时钟信号,因此在电源上电时,只有当VCC超过4.75V低于5.25V以及晶体振荡器稳定工作时,复位信号才被撤除,微机电路开始正常工作。微机电路在工作中受到干扰后,容易出现CPU程序“跑飞”而盲目运行甚至出现死机现象。此时复位信号有效,使微机系统重新恢复正常运行。这种监视CPU运行的电路称为WATCHDOG电路。VC C 3.3VC2110u图3-4 复位电路3.4 液晶显示电路液晶显示器件(LCD)是一种平板薄型显示器件,它的驱动电压很低、工作电流极小。它是一种专门用来显示字母、数字、符号等的点阵型液晶模块,它由32个5*8点阵字符位组成,每一个点阵字符位都可以显示一个字符,但是它不能显示图形。模块内部自带有160个5*8点阵字型的字符发生器CHROM和8个可由用户自定义的5*8的字符发生器CGRAM。D0-D7为传给液晶的数据(可能为显示数字或控制液晶指令),RS用于控制将D0-D7的数据写入指令寄存器还是数据寄存器,RW为读写控制信号,E为使能信号。电位器调节液晶的对比度,以到最佳显示效果。图3-5 液晶显示电路CPLD芯片与液晶显示器件(LCD)的管脚锁定如表3-1所示:表3-1 CPLD与HS162-4的管脚对应关系3.5 JTAG 下载电路JTAG 是英文“Joint Test Action Group (联合测试行为组织)”的词头字母的简写,该组织成立于1985年,是由几家主要的电子制造商发起制订的PCB 和IC 测试标准。JTAG 建议于1990年被IEEE 批准为IEEE1149.1-1990 测试访问端口和边界扫描结构标准。该标准规定了进行边界扫描所需要的硬件和软件。自从1990 年批准后,IEEE 分别于1993 年和1995 年对该标准作了补充,形成了现在使用的IEEE1149.1a-1993 和IEEE1149.1b-1994。JTAG 主要应用于:电路的边界扫描测试和可编程芯片的在线系统编程。标准的 JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。JTAG 测试允许多个器件通过 JTAG 接口串联在一起,形成一个 JTAG 链,能实现对各个器件分别测试。 JTAG 接口还常用于实现 ISP ( In-System Programmable 在系统编程)功能,如对 FLASH 器件进行编程等。通过 JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口。其典型连接如图所示:(其中JTAG_TCK,JTAGTDO, JTAG_TMS JTAG_TDI 分别对应接CPLD 相应的管脚)。JTAG 91K R81K R101KVC C 3.3VJTAG_TCK JTAG_TDO JTAG_TMS JTAG_TDIU201A图 3-6 JTAG 下载电路3.6 电源滤波电路由于CPLD可以工作在几百兆的时钟频率下,对电源的要求比较高,为了改善电源的品质,在CPLD的每个电源管脚处都加上一个滤波电容。C 3.3V图 3-7 JTAG电源滤波电路3.7 I/O口引出电路图3-8 I/O口引出电路为了方便电路板的后续扩展运用,特意将部分I/O口通过插针引出,可以很方便的运用排线与扩展器件连接。4 特殊器件介绍4.1 CPLD器件介绍CPLD是Complex Programmable Logic Device的缩写,它是有最早的PLD器件发展形成的高密度可编程逻辑器件,它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点。CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。许多公司都开发出了CPLD可编程逻辑器件。比较典型的就是Altera、Lattice、Xilinx 世界三大权威公司的产品。如Altera公司的MAXII器件,就是其极具代表性的一类CPLD器件,是有史以来功耗最低、成本最低的CPLD。MAX II CPLD基于突破性的体系结构,在所有CPLD系列中,其单位I/O引脚的功耗和成本都是最低的。Altera公司的MAX7000A系列器件是高密度、高性能的EPLD,它是基于第二代MAX 结构,采用CMOS EPROM工艺制造的。该系列的器件具有一定得典型性,其他结构都与此结构非常的类似。它包括逻辑阵列块、宏单元、扩展乘积项、可编程连线阵列和IO控制部分。由于大多数CPLD是基于乘积项的“与或”结构,故适合设计组合逻辑电路。下图4-1(a)、(b)就是CPLD的器件结构和结构原理图。图4-1(a)CPLD器件的结构图4-1(b)CPLD结构原理4.2 HS162液晶器件介绍表4-1 CGROM 中的字符代码与图形对应关系4.3 EPM570T144C5器件介绍EPM570T144C5器件是Altera 公司在2000推出的2.5V 低价格SRAM 工艺FPGA 结构与10KE 类似,带嵌入式存储块(EAB),部分型号带PLL,主要有1K10、1K30、1K50、1K100等型号。EP1K30TC144器件中,EP1K 表示器件类型,30表示器件内有30K 个逻辑门,T 代表封装类型,C 表示用途为商用,144表示管脚数为144。其引脚图如图4-2所示。U201AU201C图4-2 EPM570T144C5的引脚图5 最小系统原理本设计的电路实现是基于CPLD最小系统原理图,再配以所需的外设。最小系统设计包含了时钟产生电路模块、程序下载配置电路模块、电源电路模块,通过连线将各个模块进行连接成最小系统。由于本设计电路比较简单,外设比较少,使用到的五个独立键盘,模拟实现信号输入。我们对外设也作了扩展准备,将CPLD芯片的IO引脚进行了插针引出,以方便后续电路的扩展。将外设与最小系统进行合理正确连接,即可实现本设计的电路原理要求。(系统原理图和系统PCB图见附录)。6软件实现显示模块采用有限状态机来进行设计。设置了8个状态,其中Idle为空闲状态,主要包括有写命令和写数据来进行显示。应该注意的是,液晶是慢速的设备,每次操作之前都应该通过其状态寄存器来判断其是否处于忙的状态,在本次设计我们才操作一次等待较长的时间所以没有进行忙的检测。HS162-4液晶模块的读写操作、屏幕和光标的操作都是通过指令变成来实现的,为了方便控制,可以采用状态机进行设计,在设计中采用8个状态:图6-1 字符液晶控制器状态图其中,“IDLE”表示空闲状态,“SETCGRAM”是CGRAM状态,“SETFUNCTION”是工作方式设置状态,“SWITCHMODE”表示输入方式设置状态,“RETURNCURSOR”表示光标归位状态,“SHIFT”表示字符移位状态,“WRITERAM”是写RAM状态。HS162液晶控制指令由图6-2给出:图6-2 HS162液晶控制指令程序设计部分:module lcd_HS162(clk,rst,lcd_e,lcd_rw,lcd_rs,data);input clk,rst;output lcd_e,lcd_rw,lcd_rs; reg lcd_rw,lcd_rs;output[7:0] data;reg[7:0] data; reg[10:0] state; reg[6:0] count;reg[255:0] data_in_buf;reg flag,clk2KHz;reg[23:0] cnt; reg[5:0] disp_count;parameter IDLE =8'b00000000;parameter CLEAR =8'b00000001; //清屏parameter SETCGRAM =8'b00000010; //设置CGRAMparameter SETFUNCTION=8'b00000100;//工作方式设置1:8/1:4位数据接口;两行/一行显示;5×10/5×7点阵parameter SWITCHMODE =8'b00001000;//显示状态设置,显示开/关;光标开/关;闪烁开/关parameter SETMODE =8'b00010000;//输入方式设置,读写数据后ram地址增/减1;画面动/不动parameter RETURNCURSOR =8'b00100000; //归home位parameter SHIFT =8'b01000000;parameter WRITERAM =8'b10000000; //写RAMparameter cur_inc =1;parameter cur_dec =0;parameter cur_shift =1;parameter cur_noshift =0;parameter open_display =1;parameter open_cur =0;parameter blank_cur =0;parameter shift_display =1;parameter shift_cur =0;parameter right_shift =1;parameter left_shift =0;parameter datawidth8 =1;parameter datawidth4 =0;parameter twoline =1;parameter oneline =0;parameter font5x10 =1;parameter font5x7 =0;parameter data_in=" One World One Dream ";/* 定义液晶上显示的字符内容,注意空格也算为字符,总共两行32个字符;只需更改双引号内的字符即可实现显示字符的改变*/always@(posedge clk) //由50MHz时钟分频得到2KHZ时钟begin if(cnt==23'h6A18)begin cnt<=0;clk2KHz<=~clk2KHz; endelse cnt<=cnt+1;endassign lcd_e=clk2KHz;always @ (posedge clk2KHz or negedge rst)if(!rst) beginstate<=CLEAR;flag<=0;data_in_buf<=data_in;disp_count<=6'b0;endelse begincase(state)IDLE: begin state<=IDLE; endCLEAR: begin lcd_rs<=0;lcd_rw<=0;data<=8'b0000_0001;state<=SETCGRAM; end SETCGRAM: beginlcd_rs<=0;lcd_rw<=0;data<=8'b10000000;state<=SETFUNCTION;endSETFUNCTION : begin //工作方式设置lcd_rs<=0;lcd_rw<=0;data[7:5]<=3'b001;data[4]<=datawidth8;data[3]<=twoline;data[2]<=font5x10;data[1:0]<=2'b00;state<=SWITCHMODE;endSWITCHMODE: begin //显示状态设置lcd_rs<=0;lcd_rw<=0;data[7:3]<=5'b00001;data[2]<=open_display;data[1]<=open_cur;data[0]<=blank_cur;state<=SETMODE;endSETMODE: begin //输入方式设置lcd_rs<=0;lcd_rw<=0;data[7:2]<=6'b000001;data[1]<=cur_inc;data[0]<=cur_noshift;state<=WRITERAM;endRETURNCURSOR: beginlcd_rs<=0;lcd_rw<=0;data<=8'b00000010;state<=WRITERAM;endSHIFT: beginlcd_rs<=1;lcd_rw<=0;data<=data_in_buf[255:248];data_in_buf <= (data_in_buf << 8);disp_count <= disp_count + 1'b1;state<=WRITERAM;endWRITERAM: beginlcd_rs<=1;lcd_rw<=0;if(disp_count == 32) begindisp_count <= 4'b0;data_in_buf<=data_in;state <=CLEAR;endelse if(disp_count==16)beginlcd_rs<=0;lcd_rw<=0;data<=8'b11000000;state<=SHIFT; endelse begindata<=data_in_buf[255:248];data_in_buf <= (data_in_buf << 8);disp_count <= disp_count + 1'b1;state <= WRITERAM;endendendcaseendendmodule7 系统仿真及调试7.1 仿真通过QuartusII软件,我们进行了仿真,其仿真波形如下图:图7-1 波形仿真图根据上面所编写的程序就可以进行仿真,可以看到仿真的结果如图7-1所示,界面上正确的显示出了“ONE WORLD ONE DRENM” 字样。本设计输入信号只有clk时钟信号和rst复位信号,字符的显示主要是通过信号cld_e来控制,而cld_e是由clk分频而来。改变上面程序中的parameter data_in=" ONE WORLD ONE DREAM ";为:parameter data_in=" yang hua qiong Design "; 则仿真结果如图7-2 所示:图7-2波形仿真图由仿真结果可以看到,界面上正确显示出了“yang hua qiong Design”字样。由上面的仿真结果可知,本设计的程序设计是正确的,可以达到预期的效果,能够用CPLD实现字符液晶显示。在QuartusII软件中利用硬件描述语言描述电路后,用RTL Viewers生成的对应的电路图如图7-3所示:图7-3 用RTL Viewers生成的对应的电路图7.2 调试在QuartusII软件中,通过对所设计的硬件描述语言代码进行波形仿真后,达到了预期效果,于是,我们在该软件上进行下载配置设置。在Assignments菜单下选中Devices,在Family栏选择ACEX1K,选中EP1K30TC144-2器件。再在Assignments菜单下选中Pins 按照相应要求对管脚进行锁定。最后在Tools菜单下,选中Programmer,对配置方式进行设置,这里选择Passive Seril(PS)被动串行模式。选择好要下载的硬件设备后点击Start即可开始编程下载了。调试过程为在线调试。在通过调试中,我们发现了很多问题,现归纳如下:(1)在软件上能实现仿真的程序不一定在硬件电路上就能运行,原因有很多,这里是由于电路中的时钟频率太快,若不增加一个分频电路,灯闪烁时间太快,肉眼无法观察,故设计了一个50MHZ到2KHZ的分频电路。(2)调试中的实际问题需要考虑,人同时按多个键的同步性,不能达到时钟的精度,比如模拟键盘的输入状态是高电平有效,我们设计的结构是按键按下为低,这是若要实现该电路的控制就需要同时按下2个键,为了使输入状态实现只需按下一个键的按键控制,需要对按键逻辑取反。(3)由于分频的运算很大,故增加分频电路后,在QuartusII软件中则不能进行正确的仿真,可以直接将程序下载到电路板上去调试。8 总结与体会两周的课程设计使我们将课堂上的理论知识有了进步的了解,并增强了对EDA技术这门课程的兴趣。在本次设计中,我们完成本系统设计的要求及功能。在设计开始前我们对各个模块进行了详细的分析和设计准备工作,设计过程中,我们相互协调,积极参与完成各个技术实现的难点。通过本次设计,我们在对EDA这门技术上有了更深刻的认识,也从实践的例子中去感受到了EDA设计给我们设计带来的改变与进步。我们不仅掌握QuartusII软件和protel软件的使用,与此同时,我们还对电子设计的思路有了更多的认识。通过对EDA设计中的TOP-DOWN设计方式的运用,体会到了对于一个大型系统的设计方案选取应从顶向下的设计思路,这与传统的至底向上的设计方式有很大改进,且设计效率得到大大提高。由于时间仓促和我们自身水平有限,本设计在功能上也只是完成了一些基本功能,对于电路的可靠性,稳定性等参数还未做过详细的测试。总体来说,这次实习我受益匪浅。在摸索该如何设计电路使之实现所需功能的过程中,特别有趣,培养了我的设计思维,增加了实际操作能力。在让我体会到了设计电路的艰辛的同时,更让我体会到成功的喜悦和快乐。9 致谢在黄老师的辛勤指导下,我们小组同学积极讨论和思考,完成本此课程设计,此次设计,使我们受益匪浅。在此我要感谢电气信息学院提供这次课程设计的机会,让我们可以锻炼自己的动手能力,从实际操作中更深刻的理解熟悉在课堂上所学习的理论知识,为我们熟悉我们的专业相关技术知识提供了平台。在这里我要特别感谢黄老师,在我们的设计过程中,至始至终都得到了黄老师的悉心指导和耐心的讲解,我们的设计才得以顺利完成。这次课程设计能取得成功,还有我们组的几个同学通力合作,大家在设计中献言献策,积极发挥着个人的聪明与才智。10 参考文献[1] 谢自美. 电子线路设计(第二版)[M]. 华中科技大学出版社. 2000[2] 卢毅编著.VHDL与数字电路设计[M].北京.科技大学出版.2001[3] 侯佰亨,顾新编著.VHDL硬件描述语言与实际应用[M].西安.西安电子科社.2000[4] 康华光陈大钦. 电子技术基础模拟部分(第四版)[M]. 高等教育出版社.1987[5](美)J.Bhasker . Verilog HDL 硬件描述语言[M] . 机械工业出版社.2000[6] 周明德. 微型计算机系统原理及应用(第四版) [M]. 清华大学出版社. 2002[7] 张洪润等. 电子线路及应用. 北京.科学出版社. 2002[8] 杨宝清. 实用电路手册. 北京. 机械工业出版社. 2002[9] 潘松,黄继业.EDA技术实用教程[ M ].北京:科学出版社, 2002.[10] 杨君,王景存.基于VerilogHDL的流水线的设计方法及应用[J].武汉科技大学学报(自然科学版) ,2002, 25 (4) : 394—396.[11] 郝国法,黄睿,郝琳等.FPGA在自动售邮票机设计中的应用[J].武汉科技大学学报(自然科学版),2001,24(2):178—180.[12] 王景存,李炳生,郝国法等.用FPGA实现数字逻辑分析仪设计[J].武汉科技大学学报(自然科学版),2001,24(1):298—300.[13] 胡华春,石玉.数字锁相环原理与应用[M].上海科学技术出版社,1990.。

字符发生器的设计一、实验目的:1、掌握字符发生器原理;2、通过自己完成程序设计,掌握字符发生器的设计方法;3、通过自己完成程序设计,掌握VHDL的编程方法;二、设计要求:1、自己完成各模块的程序编写;2、设计的字数必须超过9个字以上(包含9个字);3、字符中包含自己的名字;三、使用硬件:16×16LED点阵,FPGA芯片(Cyclone EP1C12Q240C8)及连线;四、设计原理1、LED显示原理16X16的点阵显示是传统的点阵显示的基本应用,它是很多复杂的显示的基础。

这种点阵的显示可以使用多种方法来实现,其中所用到的期间也不尽相同,但是很多基本的算法和思想都是相同的,只是根据不同的硬件,具体的方法有所区别。

目前这种简单的显示方法已经很成熟了,很多地方会用到它。

例如在火车站、机场、银行、证券公司等公共场所的信息显示都是用的点阵显示。

有些场所使用了一些更为复杂的点阵。

随着硬件水平的提高,显示的效果会更加美观。

现设计一个16X16点阵。

要求汉字可不断地循环显示,并且使每个汉字之间有停顿。

一个汉字,常见的是 16×16 的点阵, 256 个发光点。

这些点,并不是同时发光的。

如果每一瞬间,只有一行发光,那就需要把整个的汉字“横向取模”,送到显示屏;如果每一瞬间,只有一列发光,那就需要把整个的汉字“纵向取模”,送到显示屏。

16×16扫描LED点阵的工作原理同8位扫描数码管类似。

它有16个共阴极输出端口,每个共阴极对应有16个LED 显示灯。

所以其扫描译码地址是4位信号线。

其汉字扫描码由 16 位段地址(l0-l15)输入。

通过时钟的每列扫描显示完整汉字。

2864E2PROM 存储器是电擦除/编程的只读存储器,容量为8K ×8Bit ,有13位并行地址线和8位并行数据线,而一个完整的字符所需的存储空间为32字节即32×8Bit ,也就是说2684最多可连续存256个16×16点阵字形。

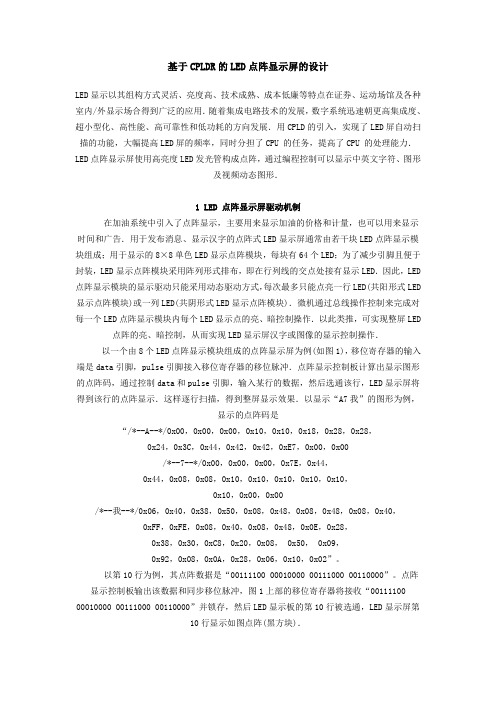

基于CPLDR的LED点阵显示屏的设计LED显示以其组构方式灵活、亮度高、技术成熟、成本低廉等特点在证券、运动场馆及各种室内/外显示场合得到广泛的应用.随着集成电路技术的发展,数字系统迅速朝更高集成度、超小型化、高性能、高可靠性和低功耗的方向发展.用CPLD的引入,实现了LED屏自动扫描的功能,大幅提高LED屏的频率,同时分担了CPU 的任务,提高了CPU 的处理能力.LED点阵显示屏使用高亮度LED发光管构成点阵,通过编程控制可以显示中英文字符、图形及视频动态图形.1 LED 点阵显示屏驱动机制在加油系统中引入了点阵显示,主要用来显示加油的价格和计量,也可以用来显示时间和广告.用于发布消息、显示汉字的点阵式LED显示屏通常由若干块LED点阵显示模块组成;用于显示的8×8单色LED显示点阵模块,每块有64个LED;为了减少引脚且便于封装,LED显示点阵模块采用阵列形式排布,即在行列线的交点处接有显示LED.因此,LED 点阵显示模块的显示驱动只能采用动态驱动方式,每次最多只能点亮一行LED(共阳形式LED 显示点阵模块)或一列LED(共阴形式LED显示点阵模块).微机通过总线操作控制来完成对每一个LED点阵显示模块内每个LED显示点的亮、暗控制操作.以此类推,可实现整屏LED 点阵的亮、暗控制,从而实现LED显示屏汉字或图像的显示控制操作.以一个由8个LED点阵显示模块组成的点阵显示屏为例(如图1),移位寄存器的输入端是data引脚,pulse引脚接入移位寄存器的移位脉冲.点阵显示控制板计算出显示图形的点阵码,通过控制data和pulse引脚,输入某行的数据,然后选通该行,LED显示屏将得到该行的点阵显示.这样逐行扫描,得到整屏显示效果.以显示“A7我”的图形为例,显示的点阵码是“/*--A--*/0x00,0x00,0x00,0x10,0x10,0x18,0x28,0x28,0x24,0x3C,0x44,0x42,0x42,0xE7,0x00,0x00/*--7--*/0x00,0x00,0x00,0x7E,0x44,0x44,0x08,0x08,0x10,0x10,0x10,0x10,0x10,0x10,0x00,0x00/*--我--*/0x06,0x40,0x38,0x50,0x08,0x48,0x08,0x48,0x08,0x40,0xFF,0xFE,0x08,0x40,0x08,0x48,0x0E,0x28,0x38,0x30,0xC8,0x20,0x08, 0x50, 0x09,0x92,0x08,0x0A,0x28,0x06,0x10,0x02”。

基于cpld实验报告基于CPLD的实验报告引言:CPLD(Complex Programmable Logic Device)是一种集成电路器件,具有可编程的逻辑功能。

它在数字电路设计和开发中扮演着重要的角色。

本实验报告将介绍基于CPLD的实验设计和实施过程,以及实验结果和分析。

一、实验目的本次实验的目的是通过使用CPLD器件,设计一个基本的数字电路,并验证其功能和性能。

通过这个实验,我们可以深入了解CPLD的工作原理和应用,提高我们的电路设计和实施能力。

二、实验设计和实施1. 实验所需材料和设备本次实验所需的材料和设备包括CPLD开发板、电源适配器、电路元件(如电阻、电容等)和连接线。

2. 实验步骤(1)准备工作:将CPLD开发板连接到电源适配器,并确保电源正常工作。

同时,准备好所需的电路元件和连接线。

(2)电路设计:根据实验要求和设计要求,设计一个适当的数字电路。

可以选择逻辑门电路、计数器电路或其他常见的数字电路。

(3)电路实施:根据电路设计,将电路元件连接到CPLD开发板上。

确保连接正确,并遵循电路设计的布局。

(4)编程CPLD:使用相应的软件工具,将设计好的电路逻辑编程到CPLD器件中。

确保编程过程正确,并检查编程结果。

(5)测试和验证:将电源适配器连接到CPLD开发板上,开启电源。

通过输入相应的信号,观察和验证电路的功能和性能。

可以使用示波器等测试设备进行测量和分析。

三、实验结果和分析经过实验,我们成功设计并实施了一个基本的数字电路。

通过测试和验证,我们发现电路能够按照设计要求正常工作,并且具有良好的性能。

在实验过程中,我们注意到CPLD器件具有以下优点:1. 可编程性:CPLD器件可以根据需要进行编程,实现不同的逻辑功能和电路设计。

2. 灵活性:CPLD器件可以根据实际需求进行配置和布局,适应不同的应用场景。

3. 高集成度:CPLD器件集成了大量的逻辑门和触发器,可以实现复杂的数字电路设计。

应用技术研究陈 霞 女 工学硕士 电气工程系讲师基于CPLD 点阵电子显示屏的设计陈霞 肖颖[文章摘要] 本文介绍了以AT-89S52单片机为控制核心,基于CPLD 独立扫描的实用、高效的智能型LED 大屏幕显示屏系统设计方法。

[关 键 词] MCU 、点阵LED 、CPLD社会的信息化,促进了显示技术的发展,LED 大屏幕点阵显示系统作为一项高科技产品已经渐渐融入了人们的生活。

与传统的显示媒体相比,由于其亮度高、动态影像显示效果好、耗能少、使用寿命长、显示内容多样、显示方式灵活、性价比高等优势,已经开始广泛应用于各行各业。

采用单片机控制的LED 点阵显示屏显示形式美观大方,显示内容灵活可变,具有低功耗,结构简单,操作方便等优点,已广泛应用于银行,证券,影视,体育和公路交通等各个方面,显示了其良好的市场前景。

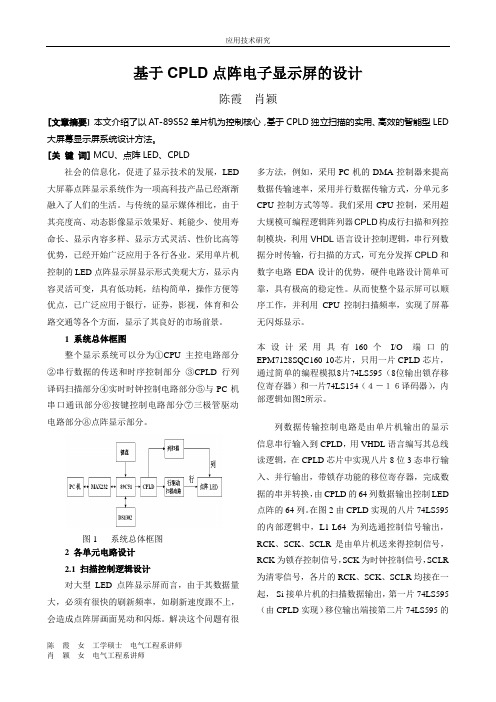

1 系统总体框图整个显示系统可以分为①CPU 主控电路部分②串行数据的传送和时序控制部分 ③CPLD 行列译码扫描部分④实时时钟控制电路部分⑤与PC 机串口通讯部分⑥按键控制电路部分⑦三极管驱动电路部分⑧点阵显示部分。

图1 系统总体框图 2 各单元电路设计 2.1 扫描控制逻辑设计对大型LED 点阵显示屏而言,由于其数据量大,必须有很快的刷新频率,如刷新速度跟不上,会造成点阵屏画面晃动和闪烁。

解决这个问题有很多方法,例如,采用PC 机的DMA 控制器来提高数据传输速率,采用并行数据传输方式,分单元多CPU 控制方式等等。

我们采用CPU 控制,采用超大规模可编程逻辑阵列器CPLD 构成行扫描和列控制模块,利用VHDL 语言设计控制逻辑,串行列数据分时传输,行扫描的方式,可充分发挥CPLD 和数字电路EDA 设计的优势,硬件电路设计简单可靠,具有极高的稳定性。

从而使整个显示屏可以顺序工作,并利用CPU 控制扫描频率,实现了屏幕无闪烁显示。

本设计采用具有160个I/O 端口的EPM7128SQC160-10芯片,只用一片CPLD 芯片,通过简单的编程模拟8片74LS595(8位输出锁存移位寄存器)和一片74LS154(4-16译码器),内部逻辑如图2所示。

基于CPLD的中文字符显示的设计与实现摘要本设计用CPLD设计制作一个中文字符显示电路。

设计以使用简单,调整方便,功能完备为目的,采用lattice公司的IspLS1032E-70lJ可编程器件,以ABLE语言为开发语言,设计并实现能够连续静态显示多个字,并且应具有一种动态显示效果的电路。

关键词中文字符显示;CPLD ABLE语言;设计本设计是旨在提高对ABLE语言的掌握水平,熟悉利用CPLD来设计实现简单实用的电路制作,同时加深对IspLS1032E-70lJ可编程器件的了解。

1 设计任务与要求用CPLD设计并制作一个16×16点阵的中文字符显示器,能够连续静态显示多个字,并且应具有一种动态显示效果(如字的左移或右移等),每个字显示时间可以自由的设定。

2 电路的框架结构和基本工作原理2.1 电路框架结构2.2 工作原理由555产生一种频率的时钟脉冲,在时钟脉冲作用下,地址计数器,EEPROM 相对应的地址单元中的字模代码输出,同时地址计数器为行选线产生电路提供地址线,随着地址计数器的变化,点阵显示屏逐行扫描,显示屏上显示出相应的字符和图案。

3 设计方案与实现3.1 功能设计随着计数器状态的转变,所显示的字符将会出现静态,左移,上移,字符之后是一幅动画,这是电路自动运行的。

用使能输入端控制显示颜色,由两个使能端构成4种状态,可产生4种颜色变换效果。

分别是全红色,全绿色,红绿换屏显示,红绿间隔同屏滚动显示。

3.2 功能模块电路实现1)主控器ispLSI1032E可编程器件1032E中实现地址计数器、E2ROM输入和输出和字体色彩的控制。

地址计数由低4位与高8构成,。

高7位实现字符的更替以达到静态、动态显示的课题要求。

扫描通过0000到1111状态转换来实现循环。

通过按钮将输入信息传到1032上来控制色彩的变化,达到所颜色的动态显示。

分频更换字符时钟功能都是由1032E来实现,通过ABLE编程语言,用一个程序实现上面几个的功能,最后直接把1032E接入电路中,从而代替了一个555、译码器和地址计数器。

EDA课程设计题目: 16*16点阵显示器的设计班级:08电子信息工程(应电方向)院系:应用技术学院姓名:学号:实验地点:应用技术学院综合实验室指导老师:王悦善职称:讲师成绩:( 2011年6月2日 )目录1. 前言 (2)1.1本设计的研究背景和研究目的 (2)1.2LED点阵显示特点 (2)1.3FPGA设计的特点 (2)2 系统设计 (3)2.1.1设计任务与要求 (3)2.1.2 设计要求 (3)2.2设计原理 (3)2.3扫描控制模块 (3)2.4方案选择 (3)2.4.1 方案一: (3)2.4.2方案二汉字的存储 (4)2.5实现 (4)2.5.1列循环扫描 (4)2.5.2字符样式设计 (5)3. 系统调试与仿真 (8)3.1开发环境介绍 (8)3.2调试与仿真 (8)3.2.1 创建工程 (8)3.2.2 编译前设置 (8)3.2.3 全程编译 (10)3.2.4功能仿真 (10)4 结束语 (12)5 参考文献 (12)6 附录:程序 (13)1. 前言1.1 本设计的研究背景和研究目的随着我国经济的高速发展,对公共场合发布信息的需求日益增长,利用LED点阵滚动显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

采用传统方法设计的汉字滚动显示器,通常需要使用单片机、存储器和制约逻辑电路来进行PCB板级的系统集成。

尽管这种方案有单片机软件的支持较为灵活,但是由于受硬件资源的限制,未来对设计的变更和升级,总是难以避免要付出较多研发经费和较长投放市场周期的代价。

随着电子设计自动化(EDA)技术的进展,基于可编程FPGA器件进行系统芯片集成的新设计方法,也正在快速地到代基于PCB板的传统设计方式。

因此,本设计的研究是很有必要的,之所以基于FPGA设计是因为现场可编程门阵列(FPGA)设计周期小,灵活度高,适合用于小批量系统,提高系统的可靠性和集成度。

并且采用编写灵活的VHDL语言编写主程序。

基于CPLD的中文字符显示的设计与实现

摘要本设计用cpld设计制作一个中文字符显示电路。

设计以使用简单,调整方便,功能完备为目的,采用lattice公司的

ispls1032e-70lj可编程器件,以able语言为开发语言,设计并实现能够连续静态显示多个字,并且应具有一种动态显示效果的电路。

关键词中文字符显示;cpld able语言;设计

中图分类号tn702 文献标识码a 文章编号

1674-6708(2010)26-0201-02

本设计是旨在提高对able语言的掌握水平,熟悉利用cpld来设计实现简单实用的电路制作,同时加深对ispls1032e-70lj可编程器件的了解。

1 设计任务与要求

用cpld设计并制作一个16×16点阵的中文字符显示器,能够连续静态显示多个字,并且应具有一种动态显示效果(如字的左移或右移等),每个字显示时间可以自由的设定。

2 电路的框架结构和基本工作原理

2.1 电路框架结构

2.2 工作原理

由555产生一种频率的时钟脉冲,在时钟脉冲作用下,地址计数器,eeprom相对应的地址单元中的字模代码输出,同时地址计数器为行选线产生电路提供地址线,随着地址计数器的变化,点阵显示屏逐行扫描,显示屏上显示出相应的字符和图案。

3 设计方案与实现

3.1 功能设计

随着计数器状态的转变,所显示的字符将会出现静态,左移,上移,字符之后是一幅动画,这是电路自动运行的。

用使能输入端控制显示颜色,由两个使能端构成4种状态,可产生4种颜色变换效果。

分别是全红色,全绿色,红绿换屏显示,红绿间隔同屏滚动显示。

3.2 功能模块电路实现

1)主控器isplsi1032e

可编程器件1032e中实现地址计数器、e2rom输入和输出和字体色彩的控制。

地址计数由低4位与高8构成,。

高7位实现字符的更替以达到静态、动态显示的课题要求。

扫描通过0000到1111状态转换来实现循环。

通过按钮将输入信息传到1032上来控制色彩的变化,达到所颜色的动态显示。

分频更换字符时钟功能都是由1032e来实现,通过able编程语言,用一个程序实现上面几个的功能,最后直接把1032e接入电路中,从而代替了一个555、译码器和地址计数器。

主控器程序部分代码如下:

module control

equations

low.clk=clk_1;//时钟方程

fpq.clk=clk_1;

high.clk=clk_2;

fff.clk=clk_2;

when low<=15 then low:=low.fb+1

else low:=0; //低四位状态转换

when high<=206 then high:=high.fb+1//高八位206种状态转换

else high:=0;

when fpq<=127 then fpq:=fpq.fb+1 //分频器状态转换

else fpq:=0;

when fff<=7 then fff:=fff.fb+1

else fff:=0;

……

end

2) 555构成行扫描时钟。

555定时器3引脚为输出。

时钟周期为:t=tl+th=0.7*r2*c2+0.7*(r1+r2)*c2≈800hz

c1=0.01u;c2=0.1u;r1=r2=7k;

计数器进入译码器进行行扫描,当时钟频率越高,低位地址计数

器计数速度就越快,行扫描一个字符的速度亦越快,屏上显示的字

符就越稳定。

根据人眼的视觉暂留特性,如果1秒内有50幅断续画面出现,则看到的将是一幅连续的画面或者是一幅稳定的图案。

3)eeprom实现字模存储

为了使电路能读出所储存的字模,把eeprom的储存信息输入电路,

通过1032输出端串联限流电阻直接与显示屏相连,实现字模的读入和输出。

字模分左右两块eeprom将左边字符代码输入到左eeprom,将右边代码输入到右eeprom。

例如电路中所显示的字符和动画自模如下:

左:00 ff 04 04 7f 44 44 44 44 48 50 60 40 7f 40 00

右:00 fe 40 40 fc 44 44 44 44 3c 04 04 04 fc 04 00

4)用74ls154译码器进行行扫描

利用4-16译码器74ls154实现,输入端a、b、c、d分别与低四位的地址计数器的输出端相连,当计数器从状态0000进位转换到1111,则输出引脚依次为1-11、13-17为低电平输出,通过驱动器,那么就实现了1~16行的扫描,只要扫描的频率适当,就可以实现字符的稳定呈现或连续的画面。

4 操作说明

1)外接电源为5v的稳压直流电源;

2)按钮说明

(1)效果开关ab为00时,效果为红色;(2)效果开关ab为01时,效果为绿色;(3)效果开关ab为10时,效果为红绿轮换;(4)效果开关ab为11时,效果为红绿滚动。

参考文献

[1]康华光,等编著.电子技术基础(数字部分)[m].高等教育出版社,2006,1.

[2]周立功,等编著.eda实验与实践[m].北京航空航天大学出版

社.。