信号完整性基础培训课程

- 格式:ppt

- 大小:4.93 MB

- 文档页数:54

信号完整性上岗培训教材编辑:审核:校对:中兴通讯上海第一研究所目录第一章高速数字设计和信号完整性分析导论1.基本概念2.理想的数字信号波形2.1理想的TTL数字信号波形2.2理想的CMOS数字信号波形2.3理想的ECL数字信号波形3.数字信号的畸变3.1地线电阻的电压降的影响3.2信号线电阻的电压降的影响3.3 电源线电阻的电压降的影响3.4 转换噪声(SSN)3.5 串扰噪声(Crosstalk)3.6 反射噪声(Reflection)3.7 边沿畸变4.研究目的5.研究领域6.研究手段第二章数字电路工作原理1.数字电路分类2.基本结构和特点2.1 TTL2.2 CMOS2.3 LVDS2.4 ECL3.电路特性3.1转换特性3.2V/I特性3.3热特性及寿命3.4直流噪声容限3.5交流噪声容限4.电路互连4.1工作电压4.2逻辑电平范围4.3噪声5.电路选型基本原则第三章传输线理论1.基本概念2.基本特性2.1特性阻抗2.2延迟3.传输线分类3.1非平衡式传输线3.2平衡式传输线4.常用传输线4.1圆导线4.2微带线4.2.1一般微带线4.2.2埋入式微带线4.3带状线4.3.1非对称式带状线4.3.2对称式带状线5.反射和匹配5.1反射系数5.2反射的计算5.3传输线的临界长度5.4传输线的匹配和端接5.4.1终端电阻并联匹配5.4.2终端阻容式并联匹配5.4.3始端串联匹配5.4.4二极管嵌位6.串绕6.1正向串绕6.2反向串绕6.3平行线和重叠线7.负载效应7.1直流负载和交流负载7.2 最小间隔7.3 集中负载7.4 分布负载7.5径向负载8.负载驱动方式8.1点对点8.2串推8.3星型8.4扇型9.传输线损耗9.1 集肤效应9.2邻近效应9.3辐射效应9.4介质损耗第四章直流供电系统设计1.基本概念2.设计目标3.一般设计规则4.多层板叠层结构5.电流回路5.1基本概念5.2回路面积5.3参考平面的开槽5.4连接器的隔离盘6.去耦电容极其应用6.1去耦电容6.2低频大容量去耦电容6.3高频去耦电容6.4多层片式陶瓷电容的材料选择6.5表面贴装电容的布局和布线6.6多层印制板中的平面电容6.7埋入式电容7.噪声抑制7.1系统电源变化7.2系统电源的电位差7.3系统逻辑地的电位差7.4地电平抖动第五章《TTL/CMOS通用设计规范——信号完整性要求》1.电气特性和器件选型2.一般设计规则3.传输线设计4.负载驱动规则5.时钟的产生和分配6.电源和地系统设计7.受控阻抗连接器设计8.逻辑级延的估算9.印制板设计规则10.热设计要求第六章《印制电路板设计规范——信号完整性要求》1.分类1.1印制板的类型1.2可生产性等级2.一般要求2.1电气连接的准确性2.2印制板的可制造性2.3印制板的可测试性2.4印制板的可靠性2.5印制板组件的维修性2.6元器件的安装形式3.详细要求3.1材料选择3.2电气性能3.3设计规则3.4电路设计3.5印制板的结构3.6机械3.7散热3.8环境3.9CAD/CAM/CAT第七章ES6000工程设计规范1.适用范围2.引用标准和文献3.符号、缩略语4.信号完整性设计目标4.1 系统噪声分配4.2 LVDS差分信号传输噪声分配4.3 LVPECL差分信号传输噪声分配5.高速信号传输规则5.1 传输设计5.2 传输线匹配规则5.3 信号传输的一般规则5.4 G.LING的信号传输5.5 SDRAM接口5.6 EHI接口5.7 LVPECL信号传输5.8 LVDS信号传输5.9 印制电路板布线的一般要求5.10 背板连接器中信号针与地针的分布6.背板设计规则6.1 印制板材料6.2 印制板结构和尺寸6.3 印制板电源、地层结构6.4 印制板孔、盘尺寸6.5 印制板布线规则7.主控与交换板设计规则7.1 印制板材料7.2 印制板结构和尺寸7.3 印制板电源、地层结构7.4 印制板空、盘尺寸7.5 印制板布线规则8.ATM接口板设计规则8.1 印制板材料8.2 印制板结构和尺寸8.3 印制板电源、地层结构8.4 印制板孔、盘尺寸8.5 印制板布线规则9.其他线路接口板设计规则9.1 印制板材料9.2 印制板结构和尺寸9.3 印制板电源、地层结构9.4 印制板孔、盘尺寸9.5 印制板布线规则第一章 高速数字系统设计的信号完整性分析导论1. 基本概念高速数字设计(High-Speed Digital Design)强调被动元件的特性及其对电路性能的影响, 包括导线、印制电路板以及集成电路封装等等;高速数字设计研究被动元件如何影响信号传输 (振铃和反射), 信号之间的相互作用(串扰); 信号完整性 (Signal Integrity ,以下简称SI) 是指信号在信号线上的质量。

摘要如果您刚刚接触信号完整性分析,或者需要温习这方面的基础知识,那么本白皮书将是您的最佳选择。

在介绍基础知识之前,本白皮书首先回答一个最基本的问题“我需要了解哪些信息”?在基础知识部分,我们首先学习关键网络的识别和分析。

接着讨论传输线,以及因快速边缘率信号所产生的高频噪声引起的各种问题。

最后,我们将了解阻抗的概念,并在阻抗和信号完整性的背景下展开讨论。

现在,让我们从零开始学习信号完整性基础知识。

在开始任何类型的仿真或分析之前,您必须做好哪些准备工作,了解哪些信息呢?您的设计中可能包含成千上万个网络,需要全部进行仿真吗?恐怕不是—您没有足够的时间完成这项工作,事实上也完全没有必要。

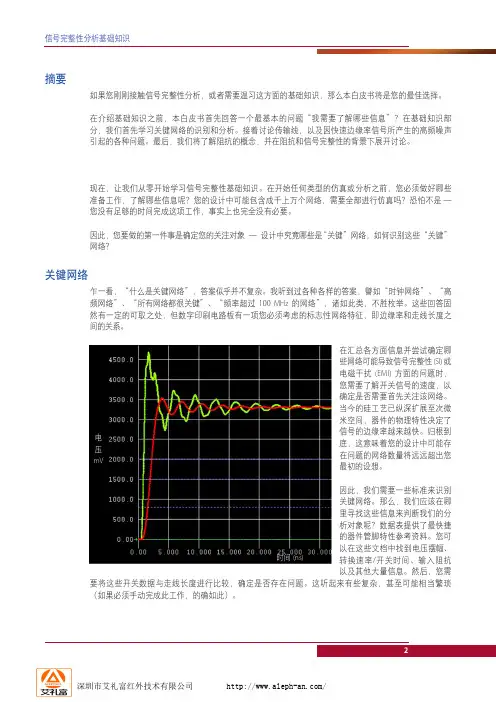

因此,您要做的第一件事是确定您的关注对象—设计中究竟哪些是“关键”网络,如何识别这些“关键”网络?关键网络乍一看,“什么是关键网络”,答案似乎并不复杂。

我听到过各种各样的答案,譬如“时钟网络”、“高频网络”、“所有网络都很关键”、“频率超过100 MHz 的网络”,诸如此类,不胜枚举。

这些回答固然有一定的可取之处,但数字印刷电路板有一项您必须考虑的标志性网络特征,即边缘率和走线长度之间的关系。

些网络可能导致信号完整性 (SI) 或电磁干扰(EMI) 方面的问题时,您需要了解开关信号的速度,以确定是否需要首先关注该网络。

当今的硅工艺已纵深扩展至次微米空间,器件的物理特性决定了信号的边缘率越来越快。

归根到底,这意味着您的设计中可能存在问题的网络数量将远远超出您最初的设想。

因此,我们需要一些标准来识别关键网络。

那么,我们应该在哪里寻找这些信息来判断我们的分析对象呢?数据表提供了最快捷的器件管脚特性参考资料。

您可以在这些文档中找到电压摆幅、转换速率/开关时间、输入阻抗以及其他大量信息。

然后,您需要将这些开关数据与走线长度进行比较,确定是否存在问题。

这听起来有些复杂,甚至可能相当繁琐(如果必须手动完成此工作,的确如此)。

这时,您需要使用工具来提供帮助。

信号完整性基础信号完整性问题过冲(overshoot/undershoot)振铃(ringing/ring back)非单调性(non-monotonic)码间串扰(ISI)同步开关噪声(SSN)噪声余量(noise margin)串扰(crosstalk)信号完整性(Signal Integrity)主要包括以下几方面问题:1.过冲(Overshoot/Undershoot)一般IC对于过冲的高度和宽度的容忍度都有指标。

因为过冲会使IC内部的ESD防护二极管导通,通常电流有100mA左右。

信号长期的过冲会使IC器件降质,并是电源噪声和EMI的来源之一。

2. 振铃(Ringing/Ring Back)振铃会使信号的threshold域值模糊,而且容易引起EMI。

3.非单调性(Non-monotonic)电平上升过程中的平台会产生非单调性,这有可能对电路有危害,特别是针对异步信号如:Reset、Clock等会有影响。

4. 码间串扰(ISI)主要是针对高速串行信号。

其产生的本质是前一个波形还没有进入稳态,另外也有可能是传输线对不同频率衰减不同所造成的。

一般通过眼图来观察,方法是输入一伪随机码,观察输出眼图。

5. 同步开关噪声(SSN)同步开关噪声会使单根静止的信号线上出现毛刺?V,另外还会影响输入电平的判断。

SSN的另一种现象是SSO(同步开关输出),这会使得传输线的特性如阻抗、延时等特性发生改变。

6. 噪声裕量(Noise Margin)控制噪声余量的目的是防止外界干扰,用于克服仿真没有分析到的一些次要因素。

一般对于TTL信号应留有200~300mV的余量。

7. 串扰(Crosstalk)串扰主要有线间串扰、回路串扰、通过平面串扰(常见于数模混合电路)三种形式。

通常示波器所观察到的数字信号。

图中为各相关的信号完整性参数:•Overshoot、Undershoot指信号的过冲。

•Ringback 指信号的振铃。

信号完整性课程设计一、课程目标知识目标:1. 让学生掌握信号完整性的基本概念,包括信号的传播、反射、串扰等现象;2. 引导学生了解信号完整性问题的产生原因及其对电子系统性能的影响;3. 使学生了解并掌握改善信号完整性的常用方法和技术。

技能目标:1. 培养学生运用所学知识分析实际电子系统中信号完整性问题的能力;2. 培养学生设计简单电路并进行信号完整性仿真实验的能力;3. 提高学生解决实际工程问题中信号完整性问题的能力。

情感态度价值观目标:1. 培养学生对信号完整性知识的兴趣和求知欲,激发学生主动学习的积极性;2. 培养学生具备良好的团队合作精神和沟通能力,能够在团队中共同解决问题;3. 引导学生认识到信号完整性在电子系统设计中的重要性,提高学生的专业素养。

课程性质:本课程为电子工程专业高年级的专业课程,旨在帮助学生深入理解信号完整性知识,提高解决实际工程问题的能力。

学生特点:学生已具备一定的电子电路基础知识,具有较强的学习能力和实践操作能力。

教学要求:结合课程性质和学生特点,注重理论与实践相结合,充分调动学生的主观能动性,提高学生的综合能力。

在教学过程中,将课程目标分解为具体的学习成果,以便进行教学设计和评估。

二、教学内容1. 信号完整性的基本概念:信号传播、反射、串扰等现象的定义及其在电子系统中的应用;2. 信号完整性问题产生原因:信号传输线理论、阻抗匹配、信号频率与传输线长度关系等;3. 信号完整性分析方法:传输线模型、反射与传输系数的计算、眼图分析等;4. 信号完整性改善技术:阻抗匹配设计、地平面设计、差分信号设计、端接技术等;5. 信号完整性仿真实验:利用相关软件(如HyperLynx、ADS等)进行简单电路的信号完整性仿真;6. 实际案例分析:分析典型电子系统中信号完整性问题的解决方法。

教学大纲安排:1. 第一周:信号完整性的基本概念及产生原因;2. 第二周:信号完整性分析方法;3. 第三周:信号完整性改善技术;4. 第四周:信号完整性仿真实验及实际案例分析。