PCBSI信号完整性汇总PPT演示课件

- 格式:ppt

- 大小:4.12 MB

- 文档页数:16

信号完整性基础信号完整性问题过冲(overshoot/undershoot)振铃(ringing/ring back)非单调性(non-monotonic)码间串扰(ISI)同步开关噪声(SSN)噪声余量(noise margin)串扰(crosstalk)信号完整性(Signal Integrity)主要包括以下几方面问题:1.过冲(Overshoot/Undershoot)一般IC对于过冲的高度和宽度的容忍度都有指标。

因为过冲会使IC内部的ESD防护二极管导通,通常电流有100mA左右。

信号长期的过冲会使IC器件降质,并是电源噪声和EMI的来源之一。

2. 振铃(Ringing/Ring Back)振铃会使信号的threshold域值模糊,而且容易引起EMI。

3.非单调性(Non-monotonic)电平上升过程中的平台会产生非单调性,这有可能对电路有危害,特别是针对异步信号如:Reset、Clock等会有影响。

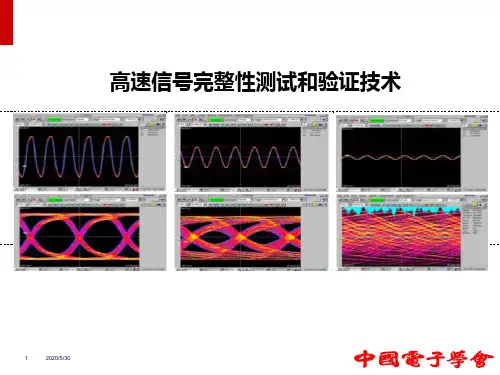

4. 码间串扰(ISI)主要是针对高速串行信号。

其产生的本质是前一个波形还没有进入稳态,另外也有可能是传输线对不同频率衰减不同所造成的。

一般通过眼图来观察,方法是输入一伪随机码,观察输出眼图。

5. 同步开关噪声(SSN)同步开关噪声会使单根静止的信号线上出现毛刺?V,另外还会影响输入电平的判断。

SSN的另一种现象是SSO(同步开关输出),这会使得传输线的特性如阻抗、延时等特性发生改变。

6. 噪声裕量(Noise Margin)控制噪声余量的目的是防止外界干扰,用于克服仿真没有分析到的一些次要因素。

一般对于TTL信号应留有200~300mV的余量。

7. 串扰(Crosstalk)串扰主要有线间串扰、回路串扰、通过平面串扰(常见于数模混合电路)三种形式。

通常示波器所观察到的数字信号。

图中为各相关的信号完整性参数:•Overshoot、Undershoot指信号的过冲。

•Ringback 指信号的振铃。

Allegro PCB SI -XL为高速数字PCB板和系统的电气设计工程师提供的一个集成的设计和分析环境,它可以探索和解决在设计各个环节中存在的与电气性能相关的问题。

通过对时序、信噪、串扰、电源地构造和电磁兼容等多方面因素进行探索和折中,设计工程师可以在将设计递交到生产之前充分优化设计的电气性能和可靠性。

它既可以对单个板进行,又可以对多块PCB板构成的系统进行。

它可以直接读、写Cadence的Allegro PCB格式的Brd文件,与Allegro PCB 设计流程完全集成。

设计工程师可以在设计的各个阶段进行高速性能的分析,如在PCB板部分布局或完全布局的情况下,在PCB 板部分布线或完全布线的情况下,甚至在没有网表或PCB数据的情况下均可进行分析。

Allegro PCB SI -XL 不需数据转换,直接对PCB数据操作的特点,以及它能够产生约束条件来驱动布局,布线功能,可以确保高速PCB设计中电气性能的约束能快速、精确地实现。

Allegro PCB SI 共包括五个主要的组成部分:. Floorplanner/editor——布局规划编辑器. SigXplorer ——SigXplorer拓扑结构研发环境. SigNoise——SigNoise信噪分析子系统. SPECCTRA Autorouter——SPECCTRA 专家级自动布线器. EMControl ——电磁兼容设计规则检查工具以下详述这五个组成部分的功能:a) Floorplanner/editor 布局规划编辑器Allegro PCB SI Floorplanner/editor 布局规划编辑器以图形化方式显示PCB板数据,方便用户阅读、分析和修改PCB数据。

设计者可以快速、方便地评判不同的布局策略对设计性能的影响。

设计工程师可以按计划好的电气约束去试布线,以便在将这些约束规则传递给PCB布局布线工程师之前,能保证这些高速PCB 设计规则的执行状态。