数字集成电路 电路系统与设计 chapter1

- 格式:ppt

- 大小:4.12 MB

- 文档页数:51

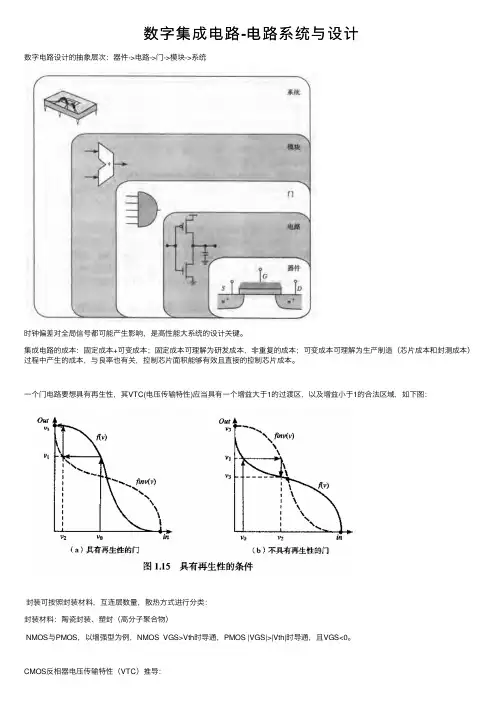

数字集成电路-电路系统与设计数字电路设计的抽象层次:器件->电路->门->模块->系统时钟偏差对全局信号都可能产⽣影响,是⾼性能⼤系统的设计关键。

集成电路的成本:固定成本+可变成本;固定成本可理解为研发成本,⾮重复的成本;可变成本可理解为⽣产制造(芯⽚成本和封测成本)过程中产⽣的成本,与良率也有关,控制芯⽚⾯积能够有效且直接的控制芯⽚成本。

⼀个门电路要想具有再⽣性,其VTC(电压传输特性)应当具有⼀个增益⼤于1的过渡区,以及增益⼩于1的合法区域,如下图:封装可按照封装材料,互连层数量,散热⽅式进⾏分类:封装材料:陶瓷封装、塑封(⾼分⼦聚合物)NMOS与PMOS,以增强型为例,NMOS VGS>Vth时导通,PMOS |VGS|>|Vth|时导通,且VGS<0。

CMOS反相器电压传输特性(VTC)推导:上式为CMOS上下管需要遵守的规则。

结合上式得到,下图为CMOS中上官PMOS部分不同栅极输⼊电压下,下管NMOS电流与输出电压的关系为了使NMOS和PMOS的传输特性能够符合上式DC成⽴,需要根据⼆者的V-I曲线找到交叉点,使其满⾜DC平衡找到上图中的DC平衡交叉点,并提取绘制得到CMOS的电压传输特性如下图,可以看出CMOS的电压传输特性具有再⽣性其中res表⽰呈电阻特性PMOS和NMOS的电流⽅向问题:源極的源是指載流⼦的起點;漏極的漏是指載流⼦的終點。

載流⼦從源極出發,穿過溝道,到達漏極,從外部看,載流⼦最終從漏極漏出去了。

顯然,NMOS和PMOS的載流⼦是不同的,因此導致了令⼈困惑的電流⽅向問題。

盯住載流⼦即可,別被電流⽅向迷惑。

可以簡單地認為,柵極和襯底間的電壓超過閾值後,漏極和源極就接通了,⽽電流⼤⼩則是由柵漏源三極間的電壓決定。

因為MOS是對稱結構,所以源極和漏極無區別且可互換。

關於D和S,也就是漏和源,其實是從⼯藝⾓度觀察的結果。

在MOS中,有兩種載流⼦,⼀種是電⼦,另⼀種是空⽳,標記為N和P。

106682367.doc1.1将下列各式写成按权展开式:(352.6)10=3×102+5×101+2×100+6×10-1(101.101)2=1×22+1×20+1×2-1+1×2-3(54.6)8=5×81+54×80+6×8-1(13A.4F)16=1×162+3×161+10×160+4×16-1+15×16-21.3二进制数00000000~11111111和0000000000~1111111111分别可以代表多少个数?解:分别代表28=256和210=1024个数。

1.4将下列个数分别转换成十进制数:(1111101000)2,(1750)8,(3E8)16解:(1111101000)2=(1000)10(1750)8=(1000)10(3E8)16=(1000)101.5将下列各数分别转换为二进制数:(210)8,(136)10,(88)16解:结果都为:(10001000)21.6将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)81.7将下列个数分别转换成十六进制数:(11111111)2,(377)8,(255)10解:结果都为(FF)161.8转换下列各数,要求转换后保持原精度:解:(1.125)10=(1.0010000000)10——小数点后至少取10位(0010 1011 0010)2421BCD=(11111100)2 (0110.1010)余3循环BCD码=(1.1110)21.9用下列代码表示(123)10,(1011.01)2:解:(1)8421BCD码:(123)10=(0001 0010 0011)8421BCD(1011.01)2=(11.25)10=(0001 0001.0010 0101)8421BCD(2)余3 BCD码(123)10=(0100 0101 0110)余3BCD(1011.01)2=(11.25)10=(0100 0100.0101 1000)余3BCD1.10已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2(1)按二进制运算规律求A+B,A-B,C×D,C÷D,(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×D,C÷D,并将结果与(1)进行比较。

数字集成电路-电路系统与设计第二版课程设计

一、课程设计介绍

数字集成电路是现代电路设计中的重要组成部分,也是计算机科学与工程的重要分支。

本课程设计旨在通过对数字集成电路的系统与设计进行探究,并结合具体的案例来设计和实现数字集成电路,使学生能够熟悉数字集成电路的基本原理、设计方法和实现技术。

本课程设计主要包含以下内容:

1.数值系统和编码

2.逻辑功能设计:组合逻辑电路和时序逻辑电路

3.集成电路设计方法和流程

4.VHDL和FPGA实现数字逻辑电路

5.数字信号处理器

通过本次课程设计,学生将掌握数字集成电路的系统性设计思路和实现方法,具备数字电路设计的基本能力和实际操作技术,能够针对具体应用场景提出解决方案,实现数字电路的设计、验证和调试。

二、课程设计要求

1. 课程设计题目

本次课程设计的题目为“4位计数器设计”。

2. 软件工具

VHDL编程软件和EDA工具

1。

数字集成电路电路系统与设计

数字集成电路是指将若干个数字电路组合在一起,形成一个完整

的电路系统的过程。

数字集成电路充分利用了数字电子技术的优势,

将不同的数字电路模块集成至一个芯片上,从而大大提高了电路系统

的性能和可靠性。

数字集成电路的设计需要遵循特定的规范和标准,包括电路功能

的设计、电路参数的计算和选取,以及电路布局和制造等方面。

同时,数字集成电路的设计需要充分考虑电路系统的稳定性、抗干扰能力、

低功耗、高可靠性等特点,以满足不同应用场景的需求。

数字集成电路常常应用于各种高精度、高复杂度数字系统中,包

括计算机、通信系统、音视频处理、自动化控制等领域。

在数字集成

电路的设计和制造中,还需要根据具体应用场景选择不同的设计方案

和制造工艺,以获得最优性能和可靠性。

数字集成电路是现代电子产品中不可或缺的一部分,它们广泛应用于计算机、手机、汽车、医疗设备等领域。

数字集成电路通过在芯片上集成大量的数字电子元件,实现了电子系统的高度集成和高速运算。

本文将从电路、系统与设计三个方面探讨数字集成电路的相关内容。

一、数字集成电路的电路结构数字集成电路的电路结构主要包括逻辑门、寄存器、计数器等基本元件。

其中,逻辑门是数字集成电路中最基本的构建元件,包括与门、或门、非门等,通过逻辑门的组合可以实现各种复杂的逻辑功能。

寄存器是用于存储数据的元件,通常由触发器构成;而计数器则可以实现计数和计时功能。

这些基本的电路结构构成了数字集成电路的基础,为实现各种数字系统提供了必要的支持。

二、数字集成电路与数字系统数字集成电路是数字系统的核心组成部分,数字系统是以数字信号为处理对象的系统。

数字系统通常包括输入输出接口、控制单元、运算器、存储器等部分,数字集成电路在其中充当着处理和控制信号的角色。

数字系统的设计需要充分考虑数字集成电路的特性,包括时序和逻辑的正确性、面积和功耗的优化等方面。

数字集成电路的发展也推动了数字系统的不断完善和创新,使得数字系统在各个领域得到了广泛的应用。

三、数字集成电路的设计方法数字集成电路的设计过程通常包括需求分析、总体设计、逻辑设计、电路设计、物理设计等阶段。

需求分析阶段需要充分了解数字系统的功能需求,并将其转化为具体的电路规格。

总体设计阶段需要根据需求分析的结果确定电路的整体结构和功能分配。

逻辑设计阶段是将总体设计转化为逻辑电路图,其中需要考虑逻辑函数、时序关系、并行性等问题。

电路设计阶段是将逻辑电路图转化为电路级电路图,包括门电路的选择和优化等。

物理设计阶段则是将电路级电路图转化为实际的版图设计,考虑布线、功耗、散热等问题。

在每个设计阶段都需要充分考虑电路的性能、面积、功耗等指标,以实现设计的最优化。

结语数字集成电路作为现代电子系统的关键组成部分,对于数字系统的功能和性能起着至关重要的作用。

数字集成电路:电路系统与设计(第二版)简介《数字集成电路:电路系统与设计(第二版)》是一本介绍数字集成电路的基本原理和设计方法的教材。

本书的内容覆盖了数字电路的基础知识、逻辑门电路、组合逻辑电路、时序逻辑电路、存储器和程序控制电路等方面。

通过学习本书,读者可以了解数字集成电路的概念、设计方法和实际应用。

目录1.数字电路基础知识 1.1 数字电路的基本概念 1.2 二进制系统与数制转换 1.3 逻辑运算与布尔代数2.逻辑门电路 2.1 与门、或门、非门 2.2 与非门、或非门、异或门 2.3 多输入门电路的设计方法3.组合逻辑电路 3.1 组合逻辑电路的基本原理 3.2 组合逻辑电路的设计方法 3.3 编码器和译码器4.时序逻辑电路 4.1 时序逻辑电路的基本原理 4.2 同步时序电路的设计方法 4.3 异步时序电路的设计方法5.存储器电路 5.1 存储器的基本概念 5.2 可读写存储器的设计方法 5.3 只读存储器的设计方法6.程序控制电路 6.1 程序控制电路的基本概念 6.2 程序控制电路的设计方法 6.3 微程序控制器的设计方法内容概述1. 数字电路基础知识本章主要介绍数字电路的基本概念,包括数字电路与模拟电路的区别、数字信号的表示方法以及数制转换等内容。

此外,还介绍了数字电路中常用的逻辑运算和布尔代数的基本原理。

2. 逻辑门电路逻辑门电路是数字电路中的基本组成单元,本章主要介绍了与门、或门、非门以及与非门、或非门、异或门等逻辑门的基本原理和组成。

此外,还介绍了多输入门电路的设计方法,以及逻辑门电路在数字电路设计中的应用。

3. 组合逻辑电路组合逻辑电路是由逻辑门电路组成的,本章主要介绍了组合逻辑电路的基本原理和设计方法。

此外,还介绍了编码器和译码器的原理和应用,以及在数字电路设计中的实际应用场景。

4. 时序逻辑电路时序逻辑电路是在组合逻辑电路的基础上引入了时序元件并进行时序控制的电路。

本章主要介绍了时序逻辑电路的基本原理和设计方法,包括同步时序电路和异步时序电路的设计。

数字集成电路(IC)在当今的电子装置和系统中发挥着至关重要的作用。

这些电路的设计将大量电子组件集成到一个单一芯片上,提供高性能和紧凑的尺寸。

在本篇文章中,我们将探索数字IC设计的关键方面,侧重于电路,系统和设计方面。

我们探索数字IC的电路方面。

数字 IC由晶体管,电阻器,电容器等基本电子元件构建而成,这些电子元件相互连接,可以实现逻辑功能。

现代数字IC集成水平惊人,数十亿晶体管被包装成一个芯片。

这种密集的集成使得在很小的物理空间内可以执行复杂的功能,如微处理器,内存单元,以及通信接口。

数字IC还设计为高速运行,消耗最小功率。

实现高速运行需要仔细考虑信号传播延迟,交叉对讲,以及动力消散。

为了应对这些挑战,IC设计师采用了先进的电路设计技术,如管道衬线,时钟标注,以及动力标注,以优化数字电路的性能和能效。

转到系统方面,数字IC常是更大的电子系统的一部分,它们与其他组件如传感器、起动器和通信接口相互作用。

数字IC的设计必须考虑到系统层面的要求,包括与外部组件的接口,处理输入、输出信号,以及支持各种通信协议。

数字IC在系统层面设计中的一个有趣例子是汽车电子领域。

现代车辆配备了广泛的数字IC,控制发动机,传输,安全系统,以及信息娱乐等功能。

这些IC必须满足可靠性、性能和安全性的严格要求,同时与各种传感器和起动器接口。

汽车数字IC的设计不仅涉及电路层面的考虑,还涉及系统层面的方面,如故障耐受性,通信协议,以及实时操作。

让我们谈谈数字IC的设计方面。

IC设计开始于具体说明电路的功能,之后是建筑和逻辑设计,电路执行,以及验证。

设计过程涉及各种工具和技术,包括逻辑综合、地点和路线、时间分析和功能核查。

设计可制造性和可检验性是关键考虑因素,可确保能够大规模生产高产量的IC并测试其可靠性。

IC设计中一个有趣的例子是开发适用于加密货币开采的集成电路。

为此目的设计的ASIC高度优化,用于履行采矿所需的密码散列功能,与一般用途处理器相比,往往能达到更高的性能和能源效率。

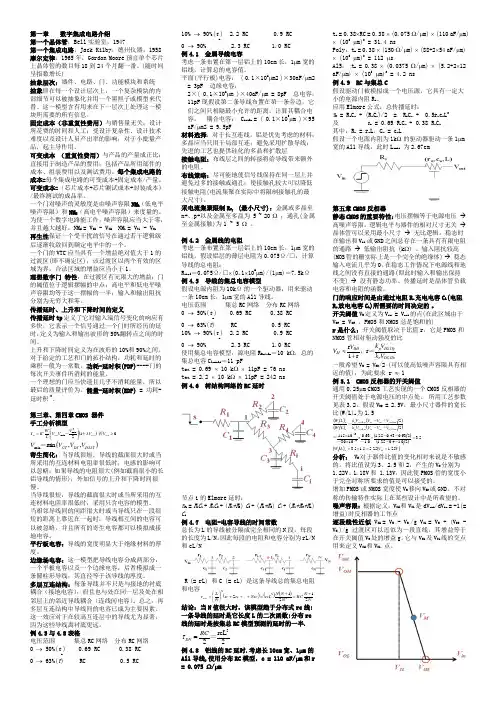

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

IC,这些微小但强大的芯片,是我们电子设备的无名英雄,从我们口袋里的光滑智能无线终端,到我们桌子上的强大的截肢者,甚至我们车上最先进的汽车系统。

当它到数字集成电路时,全部是创建顶尖的系统,来传递心跳的性能,而吸电就像一个花哨的鸡尾酒,永远,永远,投球在可靠性上。

这些电路是数据处理、信号处理和控制系统的摇滚巨星,使得我们技术精湛的世界开始运转。

但是,在所有的滑翔和魅力背后,工作上有大量的脑力。

设计数字集成电路就像开始一个令人惊叹的冒险,任务包括设定舞台有规格,通过模型化将人物带入生命,在模拟中通过脚步化,通过合成来伤害它们的存在,最后通过彻底的验证确保一切的平稳航行。

就像是数字交响乐的策划者,进行电路,系统和设计技术的和谐混合,在区块上创建最高效和可靠的集成电路。

这是一个疯狂的旅程,但有人必须做到这一点!设计数字集成电路需要使用不同的工具和方法来开发和改进数字系统。

首先要弄清楚数字系统需要做什么以及它需要多好的表现我们用维利洛格和VHDL等特殊语言创建模型并测试数字系统。

接下来,我们把模型变成逻辑门列表,我们努力确保设计符合所有要求。

我们用半导体制造来制造实际的电路。

这涉及到根据设计创建布局和建造电路。

数字集成电路领域是一个不断发展和动态的研究领域,其特点是设计方法、技术和应用方面不断取得进展。

随着数字系统继续在各种电子装置和系统中发挥重要作用,对数字集成电路设计专业人才的需求日益增加。

对这一领域感兴趣的个人必须在数字电路、系统和设计原则方面奠定坚实的基础,并随时了解数字集成电路技术的最新发展。

只要具备必要的知识和技能,就能够有助于创造创新的数字集成电路,推动技术进步,提高电子系统的性能。

数字集成电路——电路、系统与设计目录第一部分基本单元第1章引论1.1 历史回顾1.2 数字集成电路设计中的问题1.3 数字设计的质量评价1.4 小结1.5 进一步探讨第2章制造工艺2.1 引言2.2 CMOS集成电路的制造2.3 设计规则——设计者和工艺工程师之间的桥梁2.4 集成电路封装2.5 综述:工艺技术的发展趋势2.6 小结2.7 进一步探讨设计方法插入说明A——IC版图第3章器件3.1 引言3.2 二极管3.3 MOS(FET)晶体管3.4 关于工艺偏差3.5 综述:工艺尺寸缩小3.6 小结3.7 进一步探讨设计方法插入说明B——电路模拟第4章导线4.1 引言4.2 简介4.3 互连参数——电容、电阻和电感4.4 导线模型4.5 导线的SPICE模型4.6 小结4.7 进一步探讨第二部分电路设计第5章CMOS反相器5.1 引言5.2 静态CMOS反相器——直观综述5.3 CMOS反相器稳定性的评估——静态特性5.4 CMOS反相器的性能——动态特性5.5 功耗、能量和能量延时5.6 综述:工艺尺寸缩小及其对反相器衡量指标的影响5.7 小结本文由整理提供5.8 进一步探讨第6章CMOS组合逻辑门的设计6.1 引言6.2 静态CMOS设计6.3 动态CMOS设计6.4 设计综述6.5 小结6.6 进一步探讨设计方法插入说明C——如何模拟复杂的逻辑电路设计方法插入说明D——复合门的版图技术第7章时序逻辑电路设计7.1 引言7.2 静态锁存器和寄存器7.3 动态锁存器和寄存器7.4 其他寄存器类型7.5 流水线:优化时序电路的一种方法7.6 非双稳时序电路7.7 综述:时钟策略的选择7.8 小结7.9 进一步探讨第三部分系统设计第8章数字IC的实现策略8.1 引言8.2 从定制到半定制以及结构化阵列的设计方法8.3 定制电路设计8.4 以单元为基础的设计方法8.5 以阵列为基础的实现方法8.6 综述:未来的实现平台8.7 小结8.8 进一步探讨设计方法插入说明E——逻辑单元和时序单元的特性描述设计方法插入说明F——设计综合第9章互连问题9.1 引言9.2 电容寄生效应9.3 电阻寄生效应9.4 电感寄生效应9.5 高级互连技术9.6 综述:片上网络9.7 小结9.8 进一步探讨第10章数字电路中的时序问题10.1 引言10.2 数字系统的时序分类本文由整理提供10.3 同步设计——一个深入的考察10.4 自定时电路设计10.5 同步器和判断器10.6 采用锁相环进行时钟综合和同步10.7 综述:未来方向和展望10.8 小结10.9 进一步探讨设计方法插入说明G——设计验证第11章设计运算功能块11.1 引言11.2 数字处理器结构中的数据通路11.3 加法器11.4 乘法器11.5 移位器11.6 其他运算器11.7 数据通路结构中对功耗和速度的综合考虑11.8 综述:设计中的综合考虑11.9 小结11.10进一步探讨第12章存储器和阵列结构设计12.1 引言12.2 存储器内核12.3 存储器外围电路12.4 存储器的可靠性及成品率12.5 存储器中的功耗12.6 存储器设计的实例研究12.7 综述:半导体存储器的发展趋势与进展12.8 小结12.9 进一步探讨设计方法插入说明H——制造电路的验证和测试本文由整理提供。