数字电路与系统设计 (6)

- 格式:ppt

- 大小:2.38 MB

- 文档页数:60

数字逻辑电路与系统设计课程设计课程设计目的通过本课程设计的学习,学生应能够掌握数字逻辑电路基本概念、设计方法以及应用技巧。

学生应该能够使用Verilog HDL或者其他硬件描述语言(HDL)设计数字逻辑电路和系统,并能够基于FPGA平台设计和实现数字电路系统。

课程设计内容本次课程设计主要包含以下内容:1.数字电路基础知识:数字逻辑基本理论、逻辑门的特点、数字电路的抽象层次。

2.Verilog HDL编程:Verilog HDL的基本语法、数据类型、运算符以及常用结构体。

3.组合逻辑电路设计:组合逻辑电路的设计方法、Karnaugh图、逻辑门级联、多路复用器/解复用器、译码器、比较器等。

4.时序逻辑电路设计:时序逻辑电路的设计方法、触发器、寄存器、计数器等。

5.FPGA系统设计:FPGA的基本原理和结构、FPGA开发板的使用、FPGA系统设计的流程以及示例项目。

课程设计要求1.课程设计可以采用Verilog HDL或者其他HDL编程语言。

2.参与者需要结成小组,每个小组3-5人。

3.每个小组需要完成一项数字电路设计项目,包括设计报告和实验验证。

4.每个小组需要在课程结束时提交一份完整的设计报告以及实验数据和项目代码。

5.设计项目可以是基于组合逻辑或时序逻辑的电路系统设计,包括但不限于多路选择器、加法器、比较器、寄存器、时钟控制器、计数器、显示控制器等。

6.设计报告应该包含问题描述,设计总体方案,设计分级具体实现以及实验结果和分析等。

7.实验验证应该使用FPGA开发板完成,需要进行基准测试,并按照设计要求逐步进行验证。

8.设计报告和实验验证需要进行小组汇报,并进行讨论。

课程设计参考资料1.Verilog HDL编程指南(第二版), 王自发, 清华大学出版社,20182.数字逻辑与计算机设计,M. Morris Mano, Pearson Education,20153.FPGA原理与设计, Jonathan W. Valvano, Morgan & Claypool,20114.FPGA开发实战, Evan A. Curtice, Packt Publishing, 2018结论通过本次课程设计,学生将能够熟练掌握数字逻辑电路设计的基础知识和关键技能。

国内比较好的数字电路和模拟电路教材

以下是一些国内比较好的数字电路和模拟电路教材推荐:

数字电路教材:

1. 《数字电路与系统设计》(作者:王景川)-该教材主要介

绍数字电路的基础知识、设计方法和实践经验,内容涵盖数字逻辑基本原理、组合逻辑电路、时序逻辑电路等。

2. 《数字电子技术基础》(作者:马玉昆、韩震宇)-该教材

全面介绍了数字电路的基本理论和应用技术,包括数字逻辑、组合逻辑电路、时序逻辑电路等,结合大量实例、案例进行讲解,对数字电路的理解和实践能力提供了较好的支持。

模拟电路教材:

1. 《模拟电子技术基础》(作者:韩震宇、黄令峰)-该教材

以讲解模拟电子技术的基础知识和应用技术为主题,包括模拟电子基础知识、放大器、运算放大器、电源与稳压器、滤波器、振荡器等内容,通过实例、习题等方式帮助学生掌握模拟电路的设计与分析。

2. 《电子电路分析基础》(作者:郭静莉)-该教材主要介绍

电子电路的基础知识和分析方法,包括电子元器件、基本电路、放大电路、振荡电路、滤波器等,通过清晰的推导和实例分析,使学生能够更好地理解和掌握模拟电路的设计与分析。

以上教材都是在国内教育机构或高校中广泛使用,并且经过了多年的教学实践,具有较好的教学效果和用户口碑。

但是,选

择教材应根据个人的学习需求和喜好来进行,推荐参考多个教材,并结合教师指导进行学习。

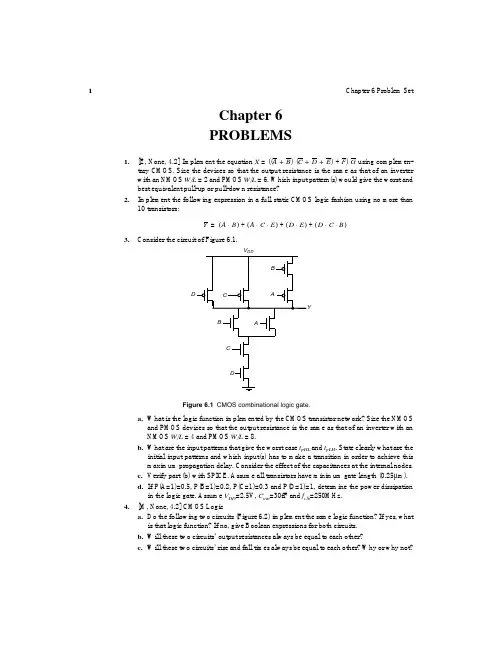

数字集成电路--电路、系统与设计(第⼆版)课后练习题第六.Digital Integrated Circuits - 2nd Ed 11 DESIGN PROJECT Design, lay out, and simulate a CMOS four-input XOR gate in the standard 0.25 micron CMOS process. You can choose any logic circuit style, and you are free to choose how many stages of logic to use: you could use one large logic gate or a combination of smaller logic gates. The supply voltage is set at 2.5 V! Your circuit must drive an external 20 fF load in addition to whatever internal parasitics are present in your circuit. The primary design objective is to minimize the propagation delay of the worst-case transition for your circuit. The secondary objective is to minimize the area of the layout. At the very worst, your design must have a propagation delay of no more than 0.5 ns and occupy an area of no more than 500 square microns, but the faster and smaller your circuit, the better. Be aware that, when using dynamic logic, the precharge time should be made part of the delay. The design will be graded on themagnitude of A × tp2, the product of the area of your design and the square of the delay for the worst-case transition.。

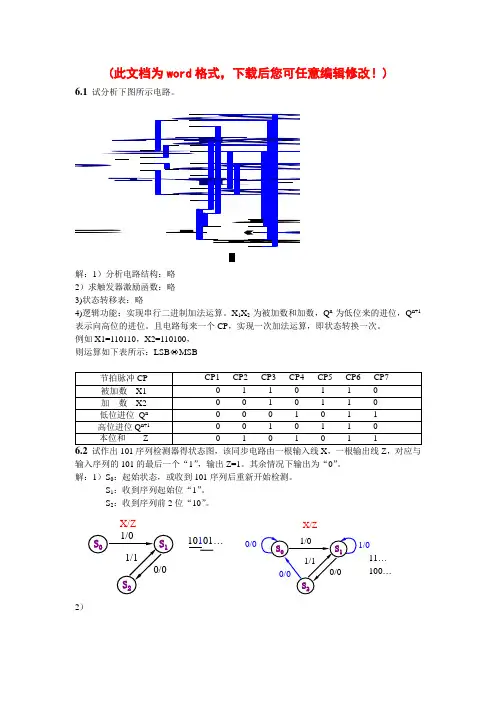

l ee t h e \1210101…X/Z0/01/0X/Z11…100…6.3对下列原始状态表进行化简: (a)解:1)列隐含表: 2)进行关联比较3)列最小化状态表为:a/1b/0b b/0a/0aX=1X=0N(t)/Z(t)S(t)解:1)画隐含表: 2)进行关联比较: 6.4 试画出用MSI 移存器74194构成8位串行 并行码的转换电路(用3片74194或2片74194和一个D 触发器)。

l ee t-h e \r 91行''' 试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:略 状态方程:略状态转移图 该电路具有自启动性。

6.7 图P6.7为同步加/减可逆二进制计数器,试分析该电路,作出X=0和X=1时的状态转移表。

解:题6.7的状态转移表X Q 4nQ 3nQ 2nQ 1nQ 4n +1Q 3n +1Q 2n +1Q 1n +1Z 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 1 1 0 0 0 0 1 1 0 0 1 0 1 1 0 0 1 0 1 1 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 0 0 1 0 0 0 0 1 1 1 0 0 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 11 1116.8分析图6.8电路,画出其全状态转移图并说明能否自启动。

数字集成电路:电路系统与设计(第二版)简介《数字集成电路:电路系统与设计(第二版)》是一本介绍数字集成电路的基本原理和设计方法的教材。

本书的内容覆盖了数字电路的基础知识、逻辑门电路、组合逻辑电路、时序逻辑电路、存储器和程序控制电路等方面。

通过学习本书,读者可以了解数字集成电路的概念、设计方法和实际应用。

目录1.数字电路基础知识 1.1 数字电路的基本概念 1.2 二进制系统与数制转换 1.3 逻辑运算与布尔代数2.逻辑门电路 2.1 与门、或门、非门 2.2 与非门、或非门、异或门 2.3 多输入门电路的设计方法3.组合逻辑电路 3.1 组合逻辑电路的基本原理 3.2 组合逻辑电路的设计方法 3.3 编码器和译码器4.时序逻辑电路 4.1 时序逻辑电路的基本原理 4.2 同步时序电路的设计方法 4.3 异步时序电路的设计方法5.存储器电路 5.1 存储器的基本概念 5.2 可读写存储器的设计方法 5.3 只读存储器的设计方法6.程序控制电路 6.1 程序控制电路的基本概念 6.2 程序控制电路的设计方法 6.3 微程序控制器的设计方法内容概述1. 数字电路基础知识本章主要介绍数字电路的基本概念,包括数字电路与模拟电路的区别、数字信号的表示方法以及数制转换等内容。

此外,还介绍了数字电路中常用的逻辑运算和布尔代数的基本原理。

2. 逻辑门电路逻辑门电路是数字电路中的基本组成单元,本章主要介绍了与门、或门、非门以及与非门、或非门、异或门等逻辑门的基本原理和组成。

此外,还介绍了多输入门电路的设计方法,以及逻辑门电路在数字电路设计中的应用。

3. 组合逻辑电路组合逻辑电路是由逻辑门电路组成的,本章主要介绍了组合逻辑电路的基本原理和设计方法。

此外,还介绍了编码器和译码器的原理和应用,以及在数字电路设计中的实际应用场景。

4. 时序逻辑电路时序逻辑电路是在组合逻辑电路的基础上引入了时序元件并进行时序控制的电路。

本章主要介绍了时序逻辑电路的基本原理和设计方法,包括同步时序电路和异步时序电路的设计。

第1章习题及解答将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)()2(3)(1101101)2 (4)()2(5)()2(6)()2(7)()2(8)()2题解:(1)(11011)2 =(27)10 (2)()2 =(151)10(3)(1101101)2 =(109)10 (4)()2 =(255)10(5)()2 =()10(6)()2 =()10(7)()2=()10(8)()2 =()10将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(1)2(3)()2 (4)()2题解:(1)(1010111)2 =(57)16 =(127)8(2)(0)2 =(19A)16 =(632)8(3)()2 =()16 =()8(4)()2 =(2C.61)16 =()8将下列十进制数表示为8421BCD码。

(1)(43)10 (2)()10(3)()10 (4)()10题解:(1)(43)10 =(01000011)8421BCD(2)()10 =(.00010010)8421BCD(3)()10 =()8421BCD(4)()10 =(.0001)8421BCD将下列有符号的十进制数表示成补码形式的有符号二进制数。

(1) +13 (2)−9 (3)+3 (4)−8题解:(1) +13 =(01101)2(2)−9 =(10111)2(3) +3 =(00011)2(4)−8 =(11000)2用真值表证明下列各式相等。

(1)BA+=+B+BBAA(2)()()()=⊕A⊕CACABB(3)()C BA+=+BCA(4)CAB++A=AABC题解:(1)证明BA+=++BABBA(2)证明()()()ACABCBA⊕=⊕(3)证明()C BACBA+=+(4)证明CAB++=AACBA用逻辑代数公式将下列逻辑函数化成最简与或表达式。

(1)D++A=F+BCBCACA(2)()()D++=F+AACCDA(3)()()B++F+=B+DCDBDDA(4)()D++F+=ADCBCBA(5)()C A B C B AC F ⊕++= (6)()()C B B A F ⊕⊕= 题解:(1)BC A D C A BC C A B A F +=+++= (2)()()CD A D CD A C A A F +=+++=(3)()()C B B A D B D A C B D D D B F ++=++++= (4)()D C B A D C B AD C B A F +=+++= (5)()C B AC C A B C B AC F +=⊕++=(6)()()C A BC B A C B B A F ++=⊕⊕=或C A C B AB ++= 用卡诺图将下列逻辑函数化成最简与或表达式。

数字电路与系统设计实验报告学院:班级:姓名:实验一基本逻辑门电路实验一、实验目的1、掌握TTL与非门、与或非门和异或门输入与输出之间的逻辑关系。

2、熟悉TTL中、小规模集成电路的外型、管脚和使用方法。

二、实验设备1、二输入四与非门74LS00 1片2、二输入四或非门74LS02 1片3、二输入四异或门74LS86 1片三、实验内容1、测试二输入四与非门74LS00一个与非门的输入和输出之间的逻辑关系。

2、测试二输入四或非门74LS02一个或非门的输入和输出之间的逻辑关系。

3、测试二输入四异或门74LS86一个异或门的输入和输出之间的逻辑关系。

四、实验方法1、将器件的引脚7与实验台的“地(GND)”连接,将器件的引脚14与实验台的十5V连接。

2、用实验台的电平开关输出作为被测器件的输入。

拨动开关,则改变器件的输入电平。

3、将被测器件的输出引脚与实验台上的电平指示灯(LED)连接。

指示灯亮表示输出低电平(逻辑为0),指示灯灭表示输出高电平(逻辑为1)。

五、实验过程1、测试74LS00逻辑关系(1)接线图(图中K1、K2接电平开关输出端,LED0是电平指示灯)(2)真值表2、测试74LS02逻辑关系(1)接线图(2)真值表3、测试74LS86逻辑关系接线图(1)接线图(2)真值表六、实验结论与体会实验是要求实践能力的。

在做实验的整个过程中,我们首先要学会独立思考,出现问题按照老师所给的步骤逐步检查,一般会检查处问题所在。

实在检查不出来,可以请老师和同学帮忙。

实验二逻辑门控制电路实验一、实验目的1、掌握基本逻辑门的功能及验证方法。

2、掌握逻辑门多余输入端的处理方法。

3、学习分析基本的逻辑门电路的工作原理。

二、实验设备1、基于CPLD的数字电路实验系统。

2、计算机。

三、实验内容1、用与非门和异或门安装给定的电路。

2、检验它的真值表,说明其功能。

四、实验方法按电路图在Quartus II上搭建电路,编译,下载到实验板上进行验证。

数字电路课程设计(5篇)第一篇:数字电路课程设计数字电路课程设计要求:1.结合所学知识设计一简单实用电路(建议选多功能数字钟),并在实验室里完成实物电路的连接调试。

2.每人独立完成一篇课程论文,论文至少2000字,可手写,也可打印(打印稿的格式另附)。

3.要求写出设计背景,理论基础,设计思路,设计过程,调试过程,仿真过程(可选),最终电路等。

4.总结所设计电路的优点,缺点,改进方向。

5.严禁抄袭,所有雷同论文均以0分计。

6.选多功能数字钟的同学在数字电路实验室完成实验。

选其它题目的同学所需软硬件资源请自行解决。

第二篇:数字电路课程设计一、设计报告书的要求: 1.封面2.课程设计任务书(题目,设计要求,技术指标等)3.前言(发展现状、课程设计的意义、设计课题的作用等方面)。

3.目录4.课题设计(⑴ 写出你考虑该问题的基本设计思路,画出一个实现电路功能的大致框图。

⑵ 画出框图中的各部分电路,对各部分电路的工作原理应作出说明。

⑶ 画出整个设计电路的原理电路图,并简要地说明电路的工作原理。

⑷ 用protel画原理电路图。

(5)用Multisim或者Proteus画仿真图。

5.总图。

6.课题小结(设计的心得和调试的结果)。

7.参考文献。

二、评分依据:①设计思路,②单元电路正确与否,③整体电路是否完整,④电路原理说明是否基本正确,⑤报告是否清晰,⑥答辩过程中回答问题是否基本正确。

三、题目选择:(三人一组,自由组合)(设计要求,技术指标自己选择)1、基于DC4011水箱水位自动控制器的设计与实现水箱水位自动控制器,电路采用CD4011四与非门作为处理芯片。

要求能够实现如下功能:水箱中的水位低于预定的水位时,自动启动水泵抽水;而当水箱中的水位达到预定的高水位时,使水泵停止抽水,始终保持水箱中有一定的水,既不会干,也不会溢,非常的实用而且方便。

2、基于CD4011声控、光控延时开关的设计与实现要求电路以CD4011作为中心元件,结合外围电路,实现以下功能:在白天或光线较亮时,节电开关呈关闭状态,灯不亮;夜间或光线较暗时,节电开关呈预备工作状态,当有人经过该开关附近时,脚步声、说话声、拍手声等都能开启节电开关。

第6章题解:6.1 试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余3BCD 码计数器。

题6.1 解:余3BCD 码计数器计数规则为:0011→0100→…→1100→0011→…,由于采用异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1所示。

CLK13图 题解6.1题6.2 试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2 解:6.3 试用D 触发器和门电路设计一个同步4位格雷码计数器。

题6.3 解:根据格雷码计数规则,Q 3 Q 2Q 1 Q 0计数器的状态方程和驱动方程为:1333031210122202131011110320320100321321321321n n n n n n n nn n n n n n n n n n n n n n n n n n n n n n n n n n n n n n Q D Q Q Q Q Q Q Q Q D Q Q Q Q Q Q Q QD Q Q Q Q Q Q Q QQ D Q Q Q Q Q Q Q Q Q Q Q Q ++++==++==++==++==+++按方程画出电路图即可,图略。

题 6.4 解:反馈值为1010。

十一进制计数器6.5 试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题 6.5 解:可采取同步清零法实现。

电路如图题解6.5所示。

题 6.6 解: 当M=1时:六进制计数器 当M=0时:八进制计数器图题解6.5图题解6.56.7 试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变量M=0时,电路为8421BCD 码十进制计数器,M=1时电路为5421BCD 码十进制计数器,5421BCD 码计数器状态图如下图P6.7所示。

74163功能表如表6.4所示。

图 P 6.7Q 3Q 2Q 1Q 01010题6.7 解:实现8421BCD 码计数器,可采取同步清零法;5421BCD 码计数器可采取置数法实现,分析5421BCD 码计数规则可知,当21Q =时需置数,应置入的数为:32103000D D D D Q =。