数字电路与系统设计(张顺兴)第四章习题答案

- 格式:pdf

- 大小:3.73 MB

- 文档页数:19

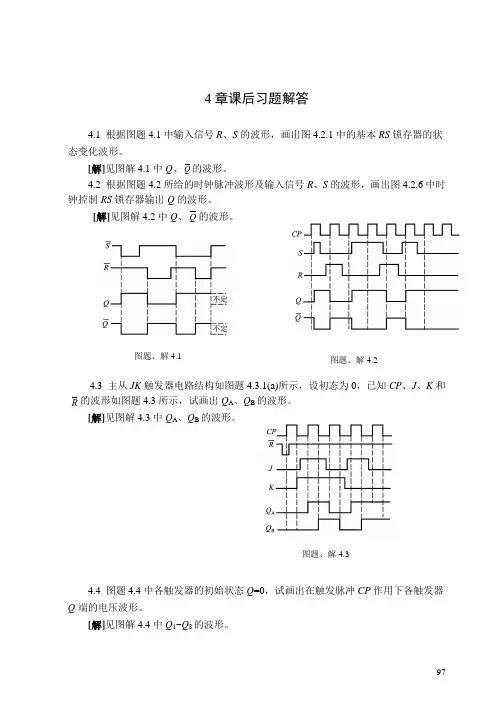

974章课后习题解答4.1 根据图题4.1中输入信号R 、S 的波形,画出图4.2.1中的基本RS 锁存器的状态变化波形。

[解]见图解4.1中Q 、Q 的波形。

4.2 根据图题4.2所给的时钟脉冲波形及输入信号R 、S 的波形,画出图4.2.6中时钟控制RS 锁存器输出Q 的波形。

[解]见图解4.2中Q 、Q 的波形。

4.3 主从JK 触发器电路结构如图题4.3.1(a)所示,设初态为0,已知CP 、J 、K 和R 的波形如图题4.3所示,试画出Q A 、Q B 的波形。

[解]见图解4.3中Q A 、Q B 的波形。

4.4 图题4.4中各触发器的初始状态Q =0,试画出在触发脉冲CP 作用下各触发器Q 端的电压波形。

[解]见图解4.4中Q 1~Q 8的波形。

图题、解4.1图题、解4.2图题、解4.3984.5画出图题4.5中Q 的波形(忽略触发器的传输延迟时间)。

[解]见图解4.5中Q 的波形。

4.6分别画出图题4.6 (a)、(b)中Q 的波形(忽略触发器的传输延迟时间,假定触发器的初始状态为0)。

【解】见图解4.6中Q 的波形。

图题、解4.4图题、解4.5图题4.699(a)(a)(b)图解4.64.7 图题4.7所示为各种边沿触发器,已知CP 、A 和B 的波形,试画出对应的Q 的波形。

(假定触发器的初始状态为0)。

【解】Q 1、Q 2、Q 3、Q 4的波形见图解4.7所示。

图题4.7100图解4.74.8 试画出图题4.8中P 的波形(忽略触发器的传输延迟时间)。

【解】P 的波形见图解4.8所示。

图解4.84.9 试分析图题4.9所示引入转换电路(在虚线框内)后,整个触发器电路的逻辑功能。

图题4.8101[解] 由于n n n Q K Q J Q +=+1,故具有JK 触发器的功能。

4.10 试用一个T 触发器及逻辑门实现一个D 触发器的功能。

【解】实现电路如图解4.10所示。

图解4.104.11试用一个D 触发器及逻辑门实现一个T 触发器的功能。

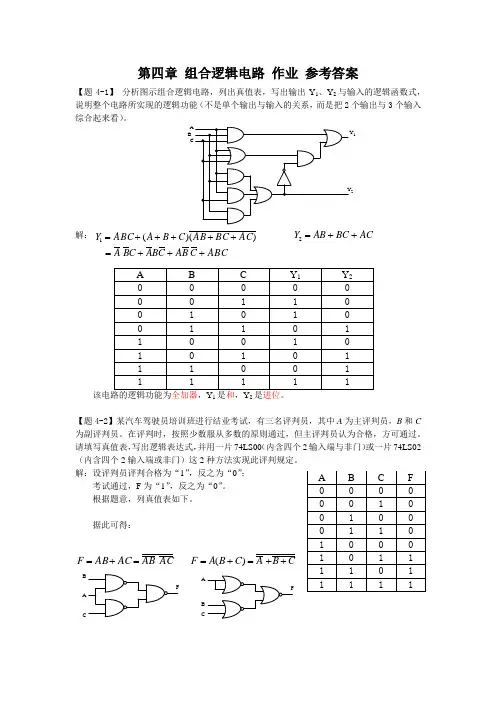

第四章 组合逻辑电路 作业 参考答案【题4-1】 分析图示组合逻辑电路,列出真值表,写出输出Y 1、Y 2与输入的逻辑函数式,说明整个电路所实现的逻辑功能(不是单个输出与输入的关系,而是把2个输出与3个输入综合起来看)。

解:该电路的逻辑功能为全加器,Y 1是和,Y 2是进位。

【题4-2】某汽车驾驶员培训班进行结业考试,有三名评判员,其中A 为主评判员,B 和C 为副评判员。

在评判时,按照少数服从多数的原则通过,但主评判员认为合格,方可通过。

请填写真值表,写出逻辑表达式,并用一片74LS00(内含四个2输入端与非门)或一片74LS02(内含四个2输入端或非门)这2种方法实现此评判规定。

解:设评判员评判合格为“1”,反之为“0”; 考试通过,F 为“1”,反之为“0”。

根据题意,列真值表如下。

据此可得:ABC12ABCC B A C B A C B A AC BC AB C B A ABC Y +++=+++++=)()(1AC BC AB Y ++=2ACAB AC AB F =+=CB AC B A F ++=+=)(FB CA FB CA【题4-3】设计一个“4输入1输出”的组合逻辑电路,实现“五舍六入”的功能:即当输入的四位8421BCD 码不大于5时,输出0;否则输出1。

要求: (1) 画出卡诺图、化简逻辑函数;(2) 用1片CD4001(内含四个2输入端或非门)实现该逻辑功能(标出管脚号)。

【题4-4】设计一个代码转换电路,输入为3位二进制代码、输出为3位格雷码(见下表),要求从CD4011、CD4001、CD4030中选用1个最合适的芯片实现逻辑功能。

解:CDAB Y 00X X 0X 011001X XXCA B A C A B A BC A Y +++=++=+=))((FB CA21313546121101000111XABC00011011YABC0010111ZABCAX =BA B A B A Y ⊕=+=CB C B C B Z ⊕=+=B CAYZX【题4-5】用一片74HC138(3-8译码器)辅以“4输入与非门”实现“1位全减”。

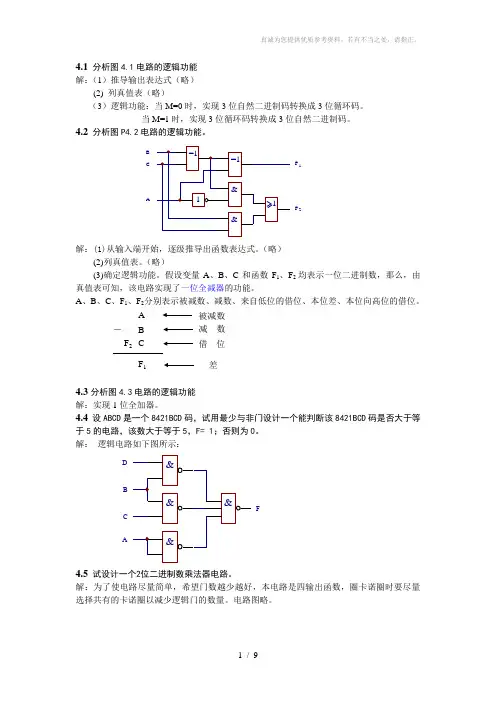

4.1分析图4.1电路的逻辑功能解:(1)推导输出表达式(略)(2) 列真值表(略)4.6 试设计一个将8421BCD 码转换成余3码的电路。

解: 电路图略。

4.7 在双轨输入条件下用最少与非门设计下列组合电路: 解:略4.8 在双轨输入信号下,用最少或非门设计题4.7的组合电路。

解:将表达式化简为最简或与式:(1)F=(A+C)(⎺A+B+⎺C)= A+C+⎺A+B+⎺C(2)F=(C+⎺D)(B+D)(A+⎺B+C)= C+⎺D+B+D+A+⎺B+C(3)F=(⎺A+⎺C)(⎺A+⎺B+⎺D)(A+B+⎺D)= ⎺A+⎺C+⎺A+⎺B+⎺D+A+B+⎺D(4)F=(A+B+C)(⎺A+⎺B+⎺C)= A+B+C+⎺A+⎺B+⎺C 4.9 已知输入波形A 、B 、C 、D ,如图P4.4所示。

采用与非门设计产生输出波形如F 的组合电路。

解: F=A ⎺C+⎺BC+C ⎺D 电路图略4.10 电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。

试设计该编码电路。

解:略4.11 试将2/4译码器扩展成4/16译码器 解:A 3A 2A 1 A 0⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺Y 4 ⎺Y 5⎺Y 6⎺Y 7 ⎺Y 8⎺Y 9⎺Y 10⎺Y 11 ⎺ Y 12⎺Y 13⎺Y 14⎺Y 15A 1 ⎺EN ⎺Y 3A 0 2/4 ⎺Y 2译码器 ⎺Y 1⎺Y 0⎺EN A 1 2/4(1)A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3⎺EN A 1 2/4(2) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺EN A 1 2/4(3) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺EN A 1 2/4(4) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 34.12试用74138设计一个多输出组合网络,它的输入是4位二进制码ABCD,输出为:F1:ABCD是4的倍数。

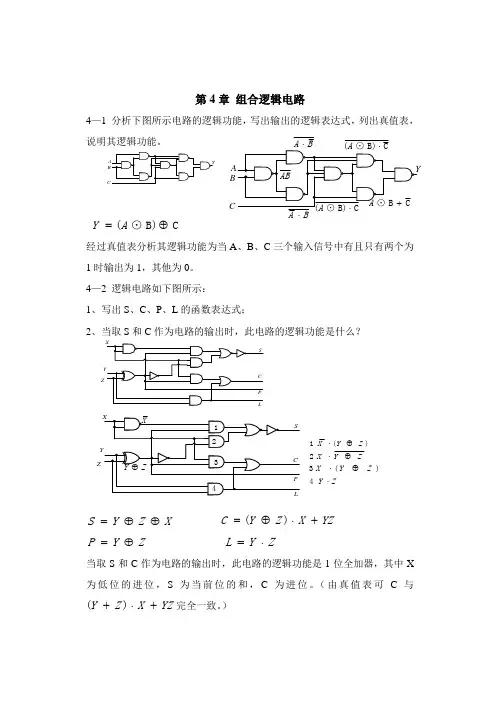

第4章 组合逻辑电路4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

C B)⊙(⊕=A Y经过真值表分析其逻辑功能为当A 、B 、C 三个输入信号中有且只有两个为1时输出为1,其他为0。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?X Z Y S ⊕⊕= YZ X Z Y C +⋅⊕=)(Z Y P ⊕= Z Y L ⋅=当取S 和C 作为电路的输出时,此电路的逻辑功能是1位全加器,其中X 为低位的进位,S 为当前位的和,C 为进位。

(由真值表可C 与YZ X Z Y +⋅+)(完全一致。

)ZB CBA ⋅CB)⊙(⋅A Z)(Z Y X ⊕⋅ZY X ⊕⋅)(Z Y X ⊕⋅ZY ⋅12344—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

Z Y X F ⊕⊕=1 Z Y X F ⋅⊕=)(2Z XY Z XY F +⋅=3 XYZ F =44—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P 和2P 的表达式,列出真值表,说明其逻辑功能。

ABC C B A m m m m Y Y P +⋅⋅=+=⋅=⋅=70707016543216543212m m m m m m Y Y Y Y Y Y P +++++=⋅⋅+⋅⋅=C B C A B A ++=P1的逻辑功能为当三个输入信号完全一致时输出为1。

P2的逻辑功能为当上输入信号不完全一致时输出为1。

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

1234解:设输入变量A 、B 、C 分别对应三台设备的状态,0表示故障,1表示正常;输出变量X 、Y 、Z 表示绿、黄、红三个灯的亮灭,0表示灭,1表示亮,根据题意可得真值表如下:设ABC 分别连入74LS138的A 2A 1A 0 由真值表得 42104210Y Y Y Y m m m m Y ⋅⋅⋅=+++=6530Y Y Y Y Z ⋅⋅⋅=4—6 下图3.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

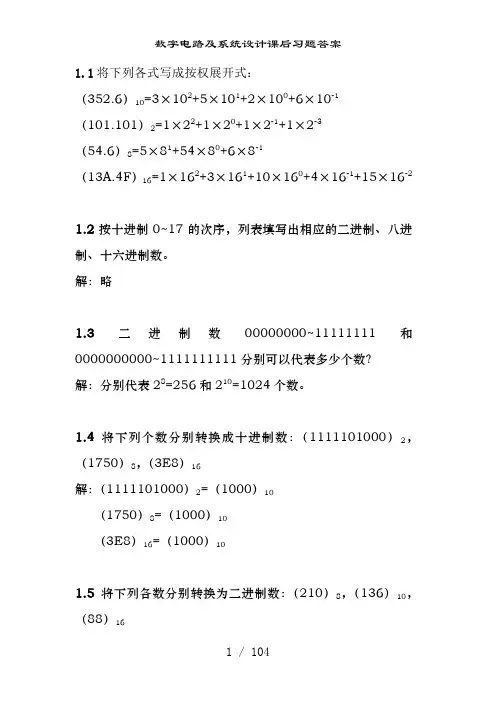

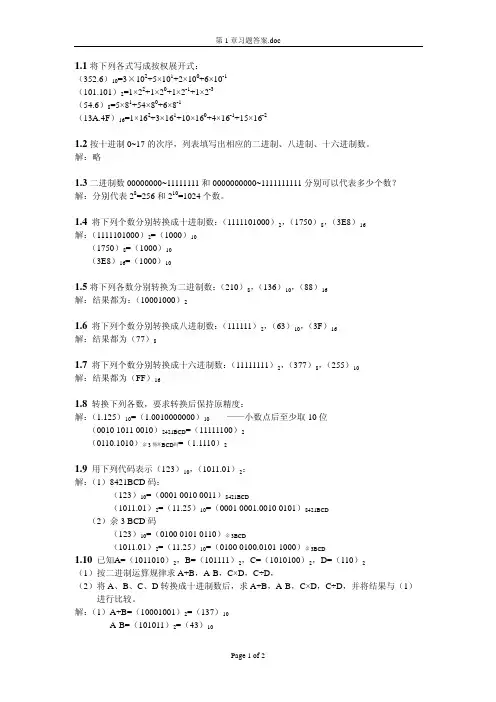

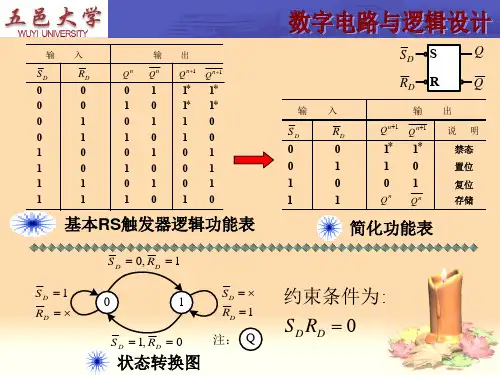

第4章触发器[题4.1]画出图P4.1所示由与非门组成的根本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的根本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3]试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3 [解]:图P4.3所示电路的真值表S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解] 见图A4.4图A4.4[题4.5] 在图P4.5电路中,假设CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图P4.5[解]见图A4.5图A4.5[题4.6]假设将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]假设主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]假设主从结构RS触发器的CP、S、R、DR各输入端的电压波形如图P4.8所示,1DS。

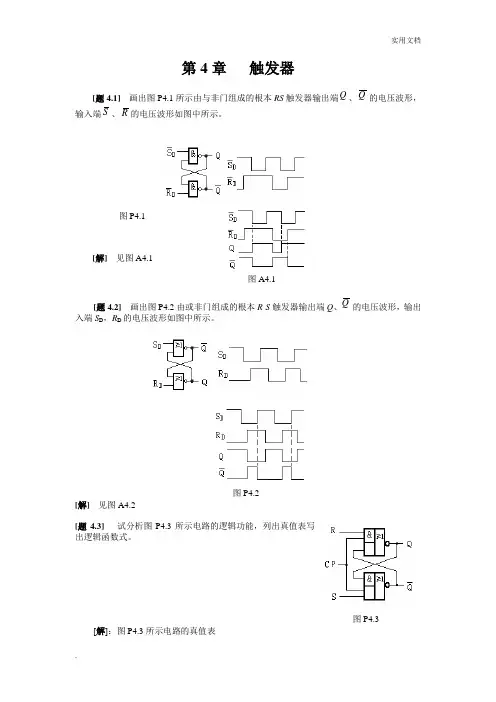

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

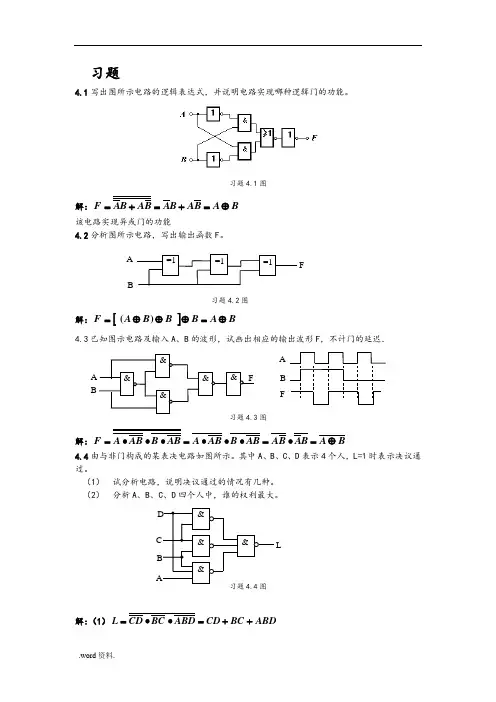

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:BABABABABAF⊕=+=+=该电路实现异或门的功能4.2分析图所示电路,写出输出函数F。

习题4.2图解:[]BABBBAF⊕=⊕⊕⊕=)(4.3已知图示电路及输入A、B的波形,试画出相应的输出波形F,不计门的延迟.图解:BABABAABBABAABBABAF⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A、B、C、D表示4个人,L=1时表示决议通过。

(1)试分析电路,说明决议通过的情况有几种。

(2)分析A、B、C、D四个人中,谁的权利最大。

习题4.4图解:(1)ABDBCCDABDBCCDL++=••=BAC &&&&DLBA =1 =1 =1FFAB&&&&&FBA(3)根据真值表可知,四个人当中C 的权利最大。

4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图 解:(1)根据波形图得到真值表:C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

FCB A解:(1)将逻辑函数化成最简与或式并转换成最简与非式。

CB A DC BD A D C B C B A D C B D A D C B C B A D C B D A D C B F •••=+++=+++=根据最简与非式画出用与非门实现的最简逻辑电路:电路略。

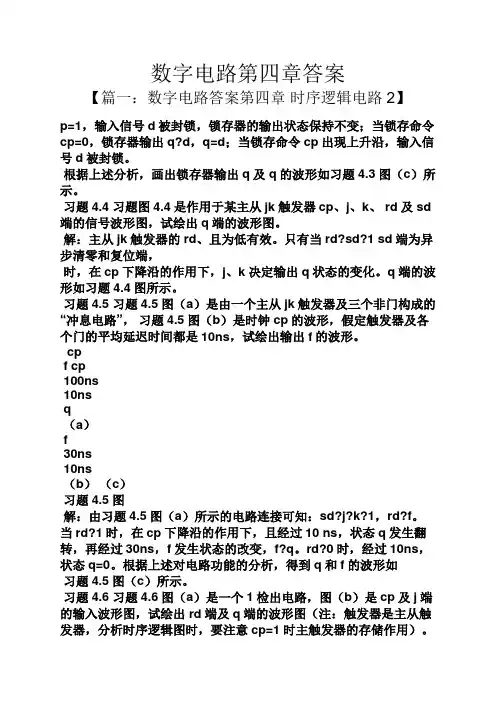

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

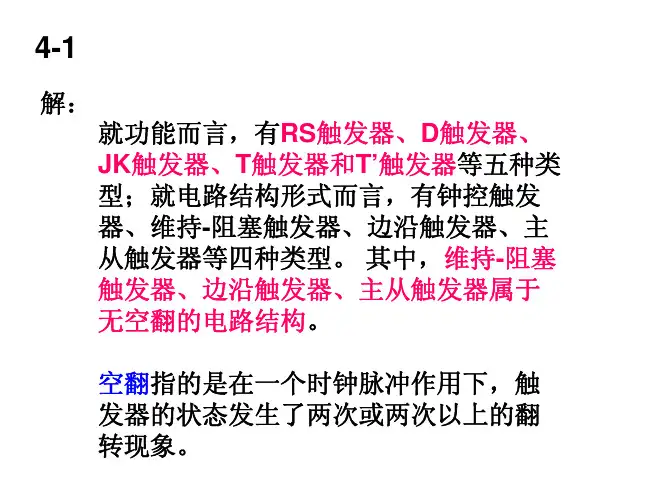

思考题与习题4-1 触发器的主要性能是什么?它有哪几种结构形式?其触发方式有什么不同?触发器是一种存储电路,具有记忆功能。

在数字电路系统中起着重要作用。

依据不同的标准,触发器可以划分为多种不同类型。

从结构上来分,触发器分为基本触发器,时钟触发器,主从触发器以及边沿触发器。

基本触发器为异步(或直接)触发,时钟触发器为 CP电平触发,主从和边沿触发器为边沿触发。

4-2 试分别写出 RS触发器、 JK 触发器、 D触发器、 T 触发器和 T′触发器的状态转换表和特性方程。

(略)4-3 已知同步 RS触发器的 R、S、CP端的电压波形如图T4-3 所示。

试画出 Q、Q端的电压波形。

假定触发器的初始状态为 0。

图 T4-34-4 设边沿 JK 触发器的初始状态为0,CP、J 、K 信号如图 T4-4 所示,试画出触发器输出端 Q、Q的波形。

图 T4-414-5 电路如图 T4-5(a) 所示,输入波形如图 T4-5(b) 所示,试画出该电路输出端G 的波形,设触发器的初始状态为0。

图 T5-24-6 试画出图 T4-6 所示波形加在以下两种触发器上时,触发器输出Q的波形:(1)下降沿触发的触发器(2)上升沿触发的触发器图 T4-64-7 已知 A、B 为输入信号,试写出图T4-7 所示各触发器的次态逻辑表达式。

2图 T4-7Q n 1D A B( a )n 1Q( b )J Q n KQ nAQ n BQ n Q nAQ n BQ n Q nB Q n B Q n4-8 设图 T4-8 所示中各 TTL 触发器的初始状态皆为0,试画出在 CP信号作用下各触发的输出端 Q1- Q6的波形。

图 T4-84-9 试对应画出图T4-9 所示电路中 Q1、 Q2波形。

(初始状态均为0)3图 T4-94-10一逻辑电路如图T4-10 所示,试画出在CP作用下 Y0、Y1、Y 2、Y 3的波形。

(CT74LS139为 2 线— 4 线译码器。

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。