MC145162锁相环(中文)

- 格式:docx

- 大小:572.15 KB

- 文档页数:13

锁相环工作原理锁相环是一种常用于频率合成和时钟同步的电路,它可以将输入信号的频率和相位与参考信号进行比较,并通过反馈控制的方式使输出信号的频率和相位与参考信号保持一致。

锁相环广泛应用于通信系统、测量仪器、雷达、无线电和音频设备等领域。

锁相环由相位比较器、低通滤波器、电压控制振荡器(VCO)和频率分频器等组成。

下面将详细介绍锁相环的工作原理。

1. 相位比较器(Phase Detector)相位比较器是锁相环的核心部件,它用于比较输入信号和参考信号的相位差。

常见的相位比较器有边沿触发型、恒幅差型和恒频差型等。

相位比较器的输出信号是一个脉冲宽度与相位差成正比的方波信号。

2. 低通滤波器(Low Pass Filter)相位比较器输出的方波信号经过低通滤波器,滤除高频成分,得到一个平滑的直流信号。

低通滤波器的作用是将方波信号转换为直流信号,并去除高频噪声。

3. 电压控制振荡器(Voltage Controlled Oscillator,VCO)低通滤波器输出的直流信号作为控制信号输入到电压控制振荡器。

VCO是一种根据输入电压的大小来调节输出频率的振荡器。

控制信号的大小决定了VCO输出频率的偏移量。

4. 频率分频器(Frequency Divider)VCO的输出信号经过频率分频器,将其频率降低到与参考信号频率相近的范围。

频率分频器的作用是将高频信号转换为低频信号,以便与参考信号进行比较。

5. 反馈回路频率分频器的输出信号与参考信号经过相位比较器进行比较,得到一个误差信号。

误差信号经过低通滤波器后,作为控制信号输入到VCO。

VCO根据控制信号的大小来调节输出频率,使其逐步接近参考信号的频率和相位。

通过不断调节VCO的输出频率,锁相环最终实现了输出信号与参考信号的频率和相位同步。

总结:锁相环通过相位比较器、低通滤波器、电压控制振荡器和频率分频器等组成,实现了输入信号与参考信号的频率和相位同步。

它在通信、测量和控制等领域具有重要的应用价值。

A题电压控制LC振荡器论文摘要本系统以89C51最小系统为控制核心,由键控显示、时钟、频率合成、功率放大、自动增益控制、电压峰值检测、频率步进与测量等功能模块组成,其中由单片机控制的全集成化锁相环频率合成器为其核心。

系统实现了频率的产生、测量,输出电压峰值的测量,频率步进的变化,功率输出等各种功能。

特色在于:频率输出的控制上有自动扫频、加减步进选频、直接按键选频及步进可选等功能;输出信号峰值、频率等参数的液晶实时显示;相应集成芯片的使用使电路结构简单明了。

指导老师:杜溪水小组成员:陈妤姗吴丽丽翁亚滨一、方案设计与论证1、LC振荡器的制作方法:方案一:采用常规的电容、电感与分立元件组成振荡器。

它是经典的方法,电路成熟,材料容易采购,也容易制作成功,频率范围也容易实现,甚至它的频率调整可以是连续的。

但它最大的缺点是它的频率稳定度最高也只能达到10-3。

它随温度、时间的变化而变化,未能达到高稳定度的要求。

方案二:一般的频率合成技术采用频率合成器,由手动控制。

它的稳定度提高了,可达到10-5,单纯硬件就可实现,更容易捕捉。

但调整频率,其操作比较麻烦,如再要显示频率,峰值等参数,电路更加复杂。

方案三:采用单片机控制的全集成化的设计。

它增加了单片机程序设计的工作量,调试复杂。

但是它只要再键盘上操作就可输出所需的频率,并直接测量其频率、峰值步进和间距等,使系统的性能有很大的提高。

全集化的设计,大大提高了系统的可靠性、稳定性,如配置温度补偿的晶体振荡器,可使输出频率的稳定性提高到10-6以上。

综合考虑制作要求及实际情况,本系统采用方案三。

2、锁相频率合成模块为了提高LC振荡器输出频率的稳定性,电路采用PLL频率合成技术。

其基本组成如图1:图1(1)集成锁相环频合器的选择方案一:采用串行输入频合器(如MB1504,MC145162),内含参考振荡器、参考分频器、相位检测器、可编程÷N计数器及接收串行输入数据所必需的移位寄存器和锁存电路,其优点是工作频率高,占用单片机的外围接口不多,为实现单片机的其它控制节省了硬件资源。

2014年TI杯福建省大学生电子设计竞赛试题(D题)设计报告——无线电源数字调谐超外差接收装置摘要本设计采用无线电源供电,用MSP430单片机控制产生本振信号,通过超外差接收电路,可自动频率搜索输入载频,自动增益控制,可显示载频频率及调制信号。

本系统无线电能传输电源,采用磁耦合方式;高放AGC和中放AGC共同作用,实现电路增益的自动控制,使电路更加可靠、稳定;本振信号由MSP430单片机控制锁相频率合成电路产生,频率在10.1~20.1MHz范围连续可调,步进1kHz;LC选频电路和选频器件实现选频及通带带宽需求;通过电压检测电路来检测判断输入信号频率。

经测试,无线电能传输电源输出+5V为系统供电正常,本设计可对输入信号实现自动搜索、检测并显示,可对输入调幅信号解调并显示相应的调制信号。

本设计完成了题目所要求的基本指标以及大部分发挥部分的指标。

关键词:无线磁耦合MSP430超外差接收机AGC低功耗1.系统方案设计(一)设计原理磁耦合无线电源:磁耦合谐振式无线电能传输技术,就是利用磁耦合和谐振技术来实现电能的无线传输。

其理论基础是耦合模式理论,其主要思想是系统中具有相同谐振频率的物体之间通过强耦合从而进行高效率的能量交换,而偏离谐振频率的物体之间相互作用则较弱。

超外差接收机:超外差接收,就是将所有要接收的电台在调频电路里调好以后,经过电路本身的作用,就变成另外一个预先设定好的频率,然后再经过放大和检波。

这个固定的频率就是由差额产生的。

在收音机内制造一个本地震荡,使它和外来高频调幅信号同时送到一个晶体管内混频。

由于晶体管的非线性作用导致混频的结果就会产生一个新的频率。

这就是外差作用。

采用了这种电路的接收机就叫外差式接收机,混频和振荡的工作,合称变频。

(二)设计方案整体方案框图:图1总体框图自动增益控制节点四节点三高频信号接收放大本振模块产生本振频率混频合成中频放大检波低频放大键盘键入频率自动扫描检测节点一节点二无线磁耦合供电MSP430控制无线电源数字调谐超外差接收装置由无线电源供电、mso430控制电路、超外差接收通道三部分构成,其中无线电源由无线系统集成芯片XKT-515结合匹配电容电感产生产生震荡发射,由电容电感谐振接收,经整流稳压后为接收机供电,接收机由手动键入或自动扫频监测输入频率,与锁相环产生的相应本振混频输出中频带载信号,并对其进行放大检波输出,在高品放大中频放大以完成设计要求。

锁相环锁相环是指一种电路或者模块,它用于通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

锁相环由鉴相器、环路滤波器和压控振荡器组成。

鉴相器用来鉴别输入信号Ui与输出信号Uo之间的相位差,并输出误差电压Ud。

Ud 中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压Uc。

Uc作用于压控振荡器的结果是把它的输出振荡频率fo拉向环路输入信号频率fi ,当二者相等时,环路被锁定,称为入锁。

维持锁定的直流控制电压由鉴相器提供,因此鉴相器的两个输入信号间留有一定的相位差。

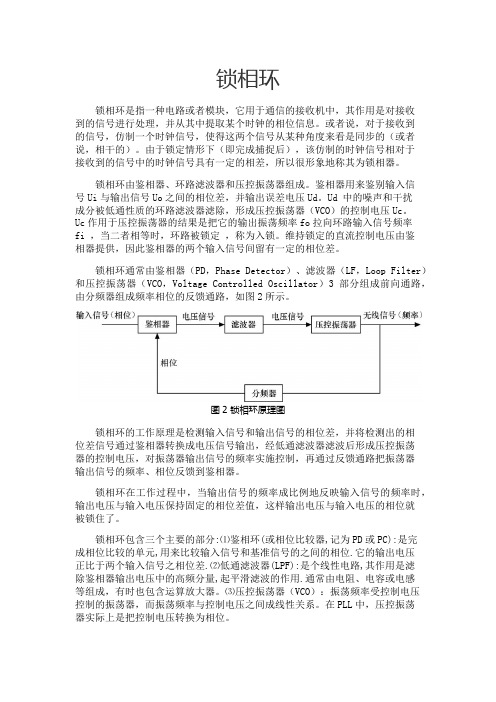

锁相环通常由鉴相器(PD,Phase Detector)、滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)3部分组成前向通路,由分频器组成频率相位的反馈通路,如图2所示。

图2 锁相环原理图锁相环的工作原理是检测输入信号和输出信号的相位差,并将检测出的相位差信号通过鉴相器转换成电压信号输出,经低通滤波器滤波后形成压控振荡器的控制电压,对振荡器输出信号的频率实施控制,再通过反馈通路把振荡器输出信号的频率、相位反馈到鉴相器。

锁相环在工作过程中,当输出信号的频率成比例地反映输入信号的频率时,输出电压与输入电压保持固定的相位差值,这样输出电压与输入电压的相位就被锁住了。

锁相环包含三个主要的部分:⑴鉴相环(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

外文资料Phase-locked loop Technology :A phase-locked loop or phase lock loop (PLL) is a control system that generates a signal that has a fixed relation to the phase of a "reference" signal. A phase-locked loop circuit responds to both the frequency and the phase of the input signals, automatically raising or lowering the frequency of a controlled oscillator until it is matched to the reference in both frequency and phase. A phase-locked loop is an example of a control system using negative feedback. In the order of the PLL is the way of made the frequency stability in the send up wireless,include VCO and PLL integrated circuits,VCO send up a signal,some of the signal is output,and the other through the frequency division with PLL integrated circuits generate the local signal making compared.In the order to remain the same,it’s must be remain the phase displacement same.If the phase displacement have some changes,the output of the PLL integrated circuits have some changes too,to controlle VCO until phase diffe rence to restore,make both cotrolled oscillator’s frequency and phase with input signal which is close-loop electronic circuit keep firm relationship.Phase-locked loops are widely used in radio, telecommunications, computers and other electronic applications. They may generate stable frequencies, recover a signal from a noisy communication channel, or distribute clock timing pulses in digital logic designs such as microprocessors. Since a single integrated circuit can provide a complete phase-locked-loop building block, the technique is widely used in modern electronic devices, with output frequencies from a fraction of a cycle per second up to many gigahertz.Earliest research towards what became known as the phase-locked loop goes back to 1932, when British researchers developed an alternative to Edwin Armstrong's superheterodyne receiver, the Homodyne. In the homodyne or synchrodyne system, a local oscillator was tuned to the desired input frequency and multiplied with the input signal. The resulting output signal included the original audio modulation information.The intent was to develop an alternative receiver circuit that required fewer tuned circuits than the superheterodyne receiver. Since the local oscillator would rapidly drift in frequency, an automatic correction signal was applied to the oscillator, maintaining it in the same phase and frequency as the desired signal. The technique was described in 1932, in a paper by H.de Bellescise, in the French journal Onde Electrique.In analog television receivers since at least the late 1930s, phase-locked-loop horizontal and vertical sweep circuits are locked to synchronization pulses in the broadcast signal. When Signetics introduced a line of monolithic integrated circuits that were complete phase-locked loop systems on a chip in 1969, applications for the technique multiplied. A few years later RCA introduced the "CD4046" CMOS Micropower Phase-Locked Loop, which became a popular integrated circuit. Applications:Phase-locked loops are widely used for synchronization purposes; in space communications for coherent carrier tracking and threshold extension, bit synchronization, and symbol synchronization. Phase-locked loops can also be used to demodulate frequency-modulated signals. In radio transmitters, a PLL is used to synthesize new frequencies which are a multiple of a reference frequency, with the same stability as the reference frequency.Clock recovery :Some data streams, especially high-speed serial data streams (such as the raw stream of data from the magnetic head of a disk drive), are sent without an accompanying clock. The receiver generates a clock from an approximate frequency reference, and then phase-aligns to the transitions in the data stream with a PLL. This process is referred to as clock recovery. In order for this scheme to work, the data stream must have a transition frequently enough to correct any drift in the PLL's oscillator. Typically, some sort of redundant encoding is used; 8B10B is very common.Deskewing :If a clock is sent in parallel with data, that clock can be used to sample the data.Because the clock must be received and amplified before it can drive the flip-flops which sample the data, there will be a finite, and process-, temperature-, and voltage-dependent delay between the detected clock edge and the received data window. This delay limits the frequency at which data can be sent. One way of eliminating this delay is to include a deskew PLL on the receive side, so that the clock at each data flip-flop is phase-matched to the received clock. In that type of application, a special form of a PLL called a Delay-Locked Loop (DLL) is frequently used.Clock generation:Many electronic systems include processors of various sorts that operate at hundreds of megahertz. Typically, the clocks supplied to these processors come from clock generator PLLs, which multiply a lower-frequency reference clock (usually 50 or 100 MHz) up to the operating frequency of the processor. The multiplication factor can be quite large in cases where the operating frequency is multiple gigahertz and the reference crystal is just tens or hundreds of megahertz.Spread spectrum:All electronic systems emit some unwanted radio frequency energy. Various regulatory agencies (such as the FCC in the United States) put limits on the emitted energy and any interference caused by it. The emitted noise generally appears at sharp spectral peaks (usually at the operating frequency of the device, and a few harmonics).A system designer can use a spread-spectrum PLL to reduce interference with high-Q receivers by spreading the energy over a larger portion of the spectrum. For example, by changing the operating frequency up and down by a small amount (about 1%), a device running at hundreds of megahertz can spread its interference evenly over a few megahertz of spectrum, which drastically reduces the amount of noise seen by FM receivers which have a bandwidth of tens of kilohertz.中文翻译锁相环技术:锁相环或锁相回路(PLL)是一个信号控制系统,即用来锁定一系列的“参考”信号。

电压控制LC振荡器王贤辉,张小田,黄应摘要:本设计基于经典西勒振荡电路,设计制作压控LC振荡器。

采用锁相环芯片MC145162将输出频率稳定度提升到10-4以上。

依据AGC原理将输出电压峰峰值稳定在1V左右。

此外,本系统功能强大,还可实现1MHz、100kHz和10kHz 步进调节频率等功能。

关键词:压控振荡;锁相环路;自动增益控制一. 方案论证与设计剖析赛题1本题要求设计并制作一压控LC正弦波振荡器,并要求实现频率步进、输出电压的峰峰值恒定并能实时显示输出电压的峰峰值。

根据以上要求可知,该设计除具有压控LC振荡模块外还必须有频率合成模块、幅度控制模块、峰峰值检测模块和显示模块。

由于输出频率范围很宽,LC振荡电路还需要根据频率范围分段切换来实现对15MHz~35MHz频率范围的覆盖。

各模块实现方案2由以上分析可以得出,要实现本设计的所有功能以及达到所要求的性能指标,就必须在各个模块的实现方案上做到深思熟虑。

针对各模块的实现,分别有以下一些不同的设计方案。

⑴压控LC振荡模块方案一:采用高稳定度的克拉泼(Clapp)经典振荡电路。

方案二:采用高稳定度的西勒(Seiler)经典振荡电路。

以上两种方案中,方案一采用克拉泼电路,该电路振荡频率较为稳定,但该振荡的频率覆盖范围较窄,一般为1.2~1.3,若要覆盖15~35MHz,至少要分3~4段。

而且该振荡在一个较宽的波段内输出幅度不均匀,频率升高后不易起振。

因此该方案不予采纳。

而方案二采用西勒电路,该电路较易起振,振荡频率也较为稳定,当参数设计得当时,覆盖范围可达1.4~1.6,因此只需2~3段即可覆盖设计要求的15~35MHz的频率范围。

故采纳方案二的设计。

⑵频率合成器模块方案一:手动调节频率合成。

通过手动调节电位器改变变容二极管的偏压来改变LC回路的振荡频率。

其优点是电路比较简单,频率调节比较简便。

但该方案无法实现程控自动步进调节频率等功能,由于此外,该方案产生的正弦波稳定性较差,调节频率易受外界环境变化的影响。

锁相环的原理2007-01-23 00:241.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

基于MC145162的锁相频率合成器的设计夏继媛;胡启龙【摘要】提出一种以单片集成PLL芯片MC145162为核心,通过ATmega16L单片机对其进行控制来实现锁相频率合成器的设计方法.探讨了锁相频率合成器的基本原理和工作特性,介绍了MC145162芯片的内部功能结构,给出了基于MC145162的锁相频率合成器的硬件电路结构和软件程序设计方法.经实际测试,锁相效果良好,结构精简,性能可靠.【期刊名称】《深圳职业技术学院学报》【年(卷),期】2011(010)003【总页数】5页(P19-23)【关键词】锁相环;频率合成器;MC145162;AVR单片机【作者】夏继媛;胡启龙【作者单位】深圳职业技术学院电子与信息工程学院,广东深圳518055;深圳职业技术学院电子与信息工程学院,广东深圳518055【正文语种】中文【中图分类】TD679频率合成技术的发展大致经历了直接模拟频率合成(DAS),锁相频率合成(PLL)和直接数字合成(DDS)3个阶段[1].DAS 尽管有频率转换快的优点,但是其体积大的弱点无法适应现代系统要求.DDS 工作频率较低但是频率分辨率很高,并且输出的噪声比较大.锁相(Phase Lock)技术是一种相位负反馈频率控制技术,该技术在锁定时无剩余频差,并具有良好的窄带载波跟踪性能和带宽调制跟踪性能,而且对相位噪声和杂散也具有很好的抑制作用,具有控制灵活、体积小、成本低和输出频率高、频带宽、频谱质量好等优点[2,3].通过锁相频率合成技术实现的频率源已在通信、电视等领域得了广泛应用.本文采用美国 MOTOROLA公司生产的MC145162通用可编程双锁相环(PLL)芯片,此芯片采用CMOS工艺,它的最高工作频率可达到60 MHz,内部包括充分可编程的接收、发送、参考和辅助参考计数器,它们的存取可以通过一个串行接口与MCU连接进行.1 频率合成器的硬件设计1.1 频率合成器的结构对于超短波频率合成器,用于无线收发信设备,设计为 2通道频率合成器分别用于发送和接收电路.将核心电路设计为发射通道和接收通道,此电路的工作原理就是将2套独立VCO电路配合锁相环芯片 MC145162,通过单片机系统控制获得所需要的发送和接收频率.因此,我们将发射通道的频率范围定为:40~60 MHz,接收通道:30~50 MHz;频道间隔25 kHz,如图1所示.图1 锁相式频率合成器电路框图1.2 压控振荡器电路(VCO)如图2所示的电路是一个压控振荡电路(VCO),其工作范围为30~60 MHz,而这种电路结构在高频到特高频(3~500 MHz)范围是VCO的主要结构形式之一,其特点是容易起振.同时由于采用了共集电极组态,振荡频率可做到较高,频率稳定度也较好.为了方便调试,其中电感采用自制的中周.图2 压控振荡器电路图电路中L是T160的电感,而C则为C173,C174,C175,VD160串联后的等效电容.C173,C174,C175的数值较大,VD160的值约为20~30PF,故等效电容主要由VD160决定.若L一定,则频率的变化主要由VD160决定.VD160为变容二极管,其电容量随加到其两端的反向电压变化而变化,因此,VCO的振荡频率受VD160两端的反向电压控制,控制关系是:反向电压增大(减小),变容二极管电容量减小(增大),VCO的振荡频率增大(减小).为提高系统稳定性,电路设计要点如下:1)决定频率的主要元件.经上述分析可知影响 VCO振荡频率的主要元件是中周和变容二极管,其电感量或电容量的改变直接影响到VCO的振荡频率,设计电路时可考虑所需的频率而制定中周的圈数或变容二极管的型号.比如中周圈数可在3~25圈制定,配合型号为SVC251(容量为 30PF左右)的变容二极管,其频率范围可设计在5~120MHz.并且变容二极管可选择的型号(容量)较多,如SVC101,SVC201,SVC251,SVC321等.2)振荡幅度的影响因素.VCO的震荡幅度主要由图3中处于 C173,C174位置的2个电容影响.我们先固定中周为16圈,然后以不同的电容值接入电路,然后测试VCO的频率范围和振荡幅度.测试结果见表1.3)扩展实验系统频率范围的方法在实验中,为了进一步了解 VCO工作频率范围和各个谐振元件参数的影响,以能使VCO达到较好的工作状态为目的,我们用不同元件参数搭配实验,得到VCO输出在10~110MHz的元件参数,见表2. 1.3 信号放大电路为了提高VCO的输出电平,我们在VCO输出后连接射频放大电路,如图3所示.此电路为分压偏置形式,其中R170,R172,R171是偏置电阻,用来调节三极管Q163的工作点电压,输入信号从耦合电容C172输入,放大后的信号由C171输出给缓冲、隔离电路.表1 VCO测试表一中周圈数(圈) 电容(P) 频率范围(MHz)输出幅度Vpp(V) 16 8215.2~26.6 1.69~0.79 16 100 14.5~24.5 1.55~0.66 16 150 13.5~21.81.30~0.50 16 200 12.7~23.5 1.19~0.28 16 220 11.8~23.8 0.90~0.21表2 VCO测试表二中周圈数(圈) 电容(P) 频率范围(MHz)输出幅度Vpp(V) 3 50 74.5~114 0.52~1.51 5 68 48.6~77.6 0.85~1.91 7 100 30.8~52.0 0.3~0.67 11 121 21~36.4 0.45~1.1 17 150 13.8~24.3 0.53~1.36 22 181 9.50~17.8 0.45~1.44图3 放大电路图1.4 缓冲电路如图4所示,电路的功能是隔离振荡电路与输出电路,起到信号缓冲的作用.信号由fin输入后经过三极管Q161、Q162隔离后由Q161发射极输出,其中在Q162发射极取得信号经 C170耦合到MC145162输入信号检测器.图4 缓冲隔离电路图1.5 输出放大电路如图5所示,此电路也称为输出匹配电路.高频放大的级与级之间或功放与负载之间是用输出匹配网络连接的,输出放大电路有以下优点:1)保证放大器传输到负载的功率最大,即起到阻抗匹配的作用;2)抑制工作频率范围以外的不需要频率,起到良好的滤波作用;3)在一定频率范围内保持较好的匹配和较高的效率.本电路由馈电电路和集电极阻抗变换电路构成.信号由 C169耦合输入 TP164可检测到输出信号.由于功放管的集电极电流很大,高次谐波成分很多,好的馈电电路可使电源的交流电流很小,减小电源电压波动.本馈电电路由C162,L160,C164,C166,C168,R160,R165,L162,L163构成,经过3级滤波使高频电流被L160,L162,L163阻止,被C164,C168,C166吸收,从而在电源端造成的高频电压波动很小.图5 输出放大电路图阻抗变换网络对高次谐波的滤除作用是十分明显的,由C164,L161,C165,VC160,C167组成的回路谐振于射频基波频率上,(此处 VC160,L161设计为可调电容和中周,便于调谐)因此在集电极可得到一定的基波阻抗.但对高次谐波而言,L的阻抗很大,C的阻抗很小,集电极电流的高次谐波分量大部分被C吸收,流过L的小部分被C吸收,因此在集电极只有较小的高次谐波电压,负载处的高次谐波电压更小.1.6 环路滤波器电路环路滤波器见图6.环路滤波器具有低通特性,它的作用是虑除鉴相器输出电压中的脉冲分量和高频干扰,滤波器的通带可根据环路的不同功能设计.本电路选择的环路滤波器为RC比例积分滤波器.图6 环路滤波器电路2 频率合成器的软件设计2.1 MCU的编程规划如图7所示,MC145162芯片通过3条数据线与MCU连接,接收MCU发送的控制信号,其通信为串行通信.MCU的编程规划决定于ENB输入所控制的2种格式.在串行数据传输中设启动信号为高,选择控制寄存器/参考频率编程模式,而设ENB为低,则选择发送和接收计数器的编程.2.2 编程时应注意的问题当MPU向MC145162的Din口写入数据时,时钟的脉冲还有使能端口的状态,我们可以看到,ENB端口在写入的过程中是处于低电平有效,而CLK端口则是高低电平地切换.要注意的是在CLK端口在最后一个时刻为高电平.在CLK的前沿,这2个计数器是用时钟脉冲将数据移入PLL的移位寄存器的,时序如图8所示.图7 串行通信接口图8 MC145162控制时序图Tx计数器分频比、Rx计数器分频比均为 16位的数值.编程中同样是定义了4个字节的连续空间来实现存取,当向单片机输入一个频率时,会经过编程处理(BCD转 BIN)后,移位送到VPLTXNH,VPLTXNL,VPLRXNH,VPLRXNL里,最后才作为32位数据输出,程序流程图如图9所示.图9 程序流程图3 应用实例某无线数字通信系统,发射机采用FM调制方式,带宽16KHZ,发射功率为2W,频率稳定度≤20 ppm,谐波辐射(邻道干扰):≤-40 dBc.接收机硬件框图如图10所示.天线感应的信号分别送往 2个接收模块,接收模块对接收信号进行适当处理后,将解调的基带信号和反映电波幅度的信号送微处理器,进行算法处理,完成测向与码元的最佳接收,最终的方向角和汉字报文通信数据在液晶上显示.其中接收模块 1和 2即为图1所示电路结构,利用锁相频率合成芯片MC145162为混频电路设计本振信号源,笔者已经将该设计在AVR单片机上实现并成功应用.图10 接收机硬件框图参考文献:[1] 王锐.DDS激励PLL频率合成器的设计与实现[J].信息技术,2009(6):197-200.[2] 陈景文.基于ADF4360_4锁相频率合成器的混频器本振源电路设计[J].电子元器件应用,2007(10):27-29.[3] 李丹,刘宏立.锁相频率合成芯片ADF4360_1及其在2.4G射频发射机中的应用[J].仪器仪表应用,2006,13(4):96-98.[4] 曾兴雯,刘乃安,陈健.高频电路原理与分析[M].西安电子科技大学出版社,2006:108.。

电压控制LC振荡器(A题)设计与报告总结摘要根据题目要求,设计采用变容二极管BB910实现电压控制LC振荡,核心控制电路基于STM32F103VET6单片机控制。

系统主要由压控式LC振荡电路,锁相环,AGC电路,单片机的控制电路及频率计,电压峰峰值测量电路,TFT液晶显示模块,键盘等部分组成。

通过晶体振荡器,MC1648和MC145162等构成的锁相环频率合成电路来提高输出频率的稳定度,实现100kHz频率步进。

若负载为容性阻抗,采用串联谐振回路以提高输出功率。

为保证输出电压幅度稳定,加入交流电压负反馈和直流AGC电路,可使系统集成度高,稳定性、可靠性强。

关键词STM32F103VET6单片机变容二极管锁相环 AGC电路 MC1648一、方案设计与论证1.主振器模块方案一:使用电感三点式振荡电路。

如下图1-1所示,电感反馈振荡电路容易起振,但电感反馈支路为感性支路,对高次谐波呈现高阻抗,故对回路中的高次谐波反馈较强,波形失真较大;另外,由于两个电感元件上的分布电容并联于电感元件的两端,工作频率越高,分布电容的影响也愈严重,这就使得电感反馈式三端振荡电路的工作频率不能太高。

图1-1 图1-2方案二:使用电容三点式振荡电路。

如上图1-2所示,电容三端振荡器的优点是输出波形较好,该电路中的不稳定电容(分布电容,器件的结电容等)都是与该电路并联的,因此适当加大回路电容量,就可以减弱不稳定的分布电容对振荡频率的影响,提高了频率稳定度。

但是电容三点式主振器在调频时不方便,而且可调范围不大。

方案三:使用采用集成的压控振荡器电路,如图下1-3所示,选用压控振荡器芯片MC1648,其工作电压5V,工作频率可从1.0MHz~150MHz,需要外接一个并行的LC槽路,结合变容二极管BB910,可以实现发挥部分的扩展频率范围要求,另外,MC1648内部有放大电路和自动增益控制,可以实现输出频率稳幅,射极随器有隔离作用,可减小负载对振荡器工作状态的影响,该电路外围元器件少,调试方便。

Motorola MC145162/D (CMOS)翻译——中文福州大学林仁杰翻译一、简介MC145162(可编程的双PLL(锁相环)频率合成器),最高频率可达到60 MHz 和85 MHz 。

适合配合MC3361,MC3362,MC2833等调频发射接收模块的使用,适用于全球范围内的CT-1制式的无绳电话。

同样适用于需要60 MHz以下的频率其它产品。

MC145162-1是MC145162的高频版本,工作频率高达85 MHz。

通过MCU的串行接口,我们可以非常方便地操作它的完全可编程的接收、发射、参考、辅助参考计数器。

正因为这样,所以它可使用于任何CT-1制式的无绳电话。

本元件的发射环和接收环各有一个独立的相位检测器。

一个共用的参考晶体,驱动两个独立的参考频率计数器,为发射环和接收环提供了独立的参考频率。

如果有需要的话,辅助参考计数器可以让我们为发射环和接收环选择一个额外的参考频率。

二、参数范围工作电压范围:2.5 到5.5 V。

工作温度范围:–40 到+75℃功耗:3.0 mA @ 2.5 V最大工作频率:MC145162 - 60 MHz @ 200 mV p–p, VDD = 2.5 VMC145162-1 - 85 MHz @ 250 mV p–p, VDD = 2.5 V可选3线或者4线的串行接口。

内置MCU时钟输出,值为参考晶体的频率÷3/÷4可选。

可由MCU的MCUCLK脚控制省电模式。

内置的参考晶体,支持外置的晶体可达16.0 MHz。

参考频率计数器的分频范围:16-4095辅助参考频率计数器的分频范围:16-16,383发射计数器的分频范围:16-65,535接收计数器的分频范围:16-65,535三、管脚定义输入端:OSCin/OSCout——参考晶体输入/输出引脚(第7、8脚)当连接到一个外接的并联谐振晶体的时候,这些引脚组成了一个参考振荡器。

应用在各国的无绳电话时,图6显示了不同的晶体频率和参考频率的关系。

作为一个外接产生的参考信号时,OSCin可作为输入脚,通常是AC耦合的。

MCUCLK——系统时钟脚(第5脚)这个输出脚提供了一个3分频或者4分频的晶体频率信号(OSCout),由控制寄存器中的专用位来配置。

本信号可以作为MCU或者其他系统的时钟源。

ADin, Din, CLK, ENB——辅助数据输入脚、数据输入脚、时钟脚、使能脚(第2、3、1、4脚)这4个脚提供了一个MCU的串行接口,为参考计数器、发射通道计数器、接受通道计数器编程。

他们还提供PLL的各种控制功能,包括省电模式与编程格式。

TxPS/fTx, RxPS/fRx——发射省电模式、接收省电模式(第13、11脚)正常情况下,这些输出引脚提供了内置节能模式工作的状态信息。

假如发射通道计数器电路处于关机模式,TxPS/fTx脚被置高。

假如接收通道计数器电路处于关机模式,RxPS/fRx 脚被置高。

这些输出脚被用来控制发射机和接收机的外置电源开关,以节省MCU的控制引脚。

在Tx/Rx通道计数器处于测试模式时,TxPS/fTx 与RxPS/fRx引脚分别输出发射通道计数器(fTx)和接收通道计数器(fRx)的分频值。

控制寄存器控制这个测试模式。

计数器的测试模式的详细资料,在本数据手册的Tx/Rx 通道计数器测试部分。

fin-T/fin-R——发射/接收计数器输入引脚(第14、9脚)fin-T 和fin-R 被分别输入到发射与接收计数器。

这些信号通常由VCO环路驱动,且为AC耦合。

最小的输入信号电平为200 mV p-p @ 60.0 MHz。

输出端:TxPDout/RxPDout——发射/接收相位检测器输出引脚(第15、10脚)这些发射与接收相位检测器三态输出脚,被用作环路错误信号(参见图7:相位检测器的输出波形)。

鉴相器增益为VDD/4 π V/弧度。

频率:fV > fR 或fV 超前:输出= 负脉冲频率:fV < fR 或fV 滞后:输出= 正脉冲频率:fV = fR 且同相:输出= 高阻抗状态注意:fR为鉴相器输入脚经分压后的参考频率,而fV为鉴相器输入脚经分频后的VCO频率。

LD——锁定检测脚(第16脚)锁定检测信号与发射环相关联。

输出脚为高电平表示失锁(参见图7:LD输出脚的波形)。

电源部分:VDD——电源正极(第12脚)VDD对VSS的范围为2.5-5.5 V。

VSS——电源负极(第6脚)。

VSS为电源负极,通常接地。

电平:VH = 高电平VL = 低电平在这一点上,当fR和fV同相时,输出脚被拉到电源电压的一半。

注意:当失锁的时候,TxPDout 和RxPDout引脚产生错误的脉冲。

当相位和频率锁定时,输出端为高阻态、那个脚的电压取决于低通滤波电容。

图7.鉴相器/锁定检测器的输出波形四、MCU的编程方法MCU的编程方法有两种格式,由ENB输入引脚所控制。

在串行数据传输的时候,假如使能信号为高,控制寄存器/参考频率编程被选中。

假如ENB为低时,发射计数器与接收计数器的被选中编程。

在发射计数器与接收计数器编程期间,ADin 和Din脚都能输入数据到发射与接收计数器。

在CLK信号的上升沿,两个计数器的数据时序移入PLL的内置移位寄存器。

当用使能信号来编程发射/接收通道时,不必重新编程参考频率计数器/控制寄存器。

在编程控制寄存器/参考频率时,编程字的最高位(MSB)指示输入数据是控制字,或者是参考频率数据字。

假如MSB为1,输入数据为控制字(图8)。

同样参考图8与表1,控制寄存器与位定义。

假如MSB为0,输入数据是参考频率(图9)。

参考频率字有32位,包括了12位的参考频率数据、14位辅助参考频率计数器信息、额外的参考频率选项和辅助参考频率计数器得使能位(图9)。

假如AUX、REF、ENB位都为高,14位辅助参考频率计数器将为各个环路提供了一个额外的相位参考频率输出。

假如AUX、REF、ENB位都为低,为省电起见,辅助参考频率计数器进入关机模式。

(其它关机模式将由控制寄存器按表2和图8执行)。

在ENB信号的下降沿,数据被存入寄存器。

通用通道模式有两种接口:3线或者4线接口模式。

3线接口模式适用于MCU的SPI模式(图10),4线接口模式适用于通用I/O口连接(图11)。

1)3线模式在3线接口模式里,辅助数据选择位被置0。

由16位的发射计数器和16位的接收计数器组成的32位数据,在CLK信号的上升沿,将通过引脚的数据锁存到PLL的内置寄存器。

参见图12和13。

2)4线模式对于4线接口模式,辅助数据选择位被置1。

在这种模式里,16位的发射寄存器数据和16位的接收寄存器数据同时分别输入ADin脚和Din脚。

这种发射寄存器与接收寄存器同时输入数据的方法,使得4线接口模式的编程周期只有3线接口模式的一半。

(参见图14和15)当编程Tx/Rx通道计数器,ENB脚必须动作,以便在上次时钟的上升沿之后提供下降沿来锁存移位数据。

最大数据传输速率为500 kbps。

注意:1、最初的晶体启动时间要10ms,以使得所有的寄存器被清空,允许编程新的数据值。

2、在串行数据传输时,ENB脚置高有效。

Test Bit(测试位)置1:Tx/Rx通道计数器处于测试模式。

置0:正常使用Aux Data Select(辅助数据选项)置1:ADin 和Din脚分别输入16位发射数据和16位接收数据。

置0:正常使用MCU的SPI接口。

不用ADin引脚,将ADin引脚拉低。

REFout /3或/ 4(REFout÷3/÷4 )置1:REFout输出频率= OSCout ÷ 3。

置0:REFout输出频率= OSCout ÷ 4。

TxPD Enable(TxPD使能)置1:发射寄存器、发射鉴相器及相关电路处于关机模式。

Tx PS/fTx 被置高。

RxPD Enable(TxPD使能)置1:接收寄存器、接收鉴相器及相关电路处于关机模式。

Rx PS/fRx 被置高。

Ref PD Enable(Ref PD使能)置1:12位和14位的参考频率计数器都处于关机模式。

图15发射计数器与接收计数器的编程格式。

(4脚接口)注意:串行数据传输的时候,ENB脚置低有效。

参考频率选项与编程图16显示了参考频率编程字的位功能。

用户可以为所有的通道选择“固定”参考频率,或者通过使用2个参考频率计数器,为一个特定的通道提供一个特定参考频率。

但是发射通道6、8和14可设成25 kHz,通道8的参考频率可设为50 kHz。

但是这个参考频率可能不能被用在接收端;此外,接收端的参考频率必须由另外一个参考频率计数器产生。

参考频率越高,相位噪声性能越好,锁定所需要的时间越短。

但是两个参考频率计数器都在工作的话,PLL将消耗更多电流。

通常情况下,12位的参考频率计数器加上÷4 和÷25模块,可以提供所有的参考频率,以满足需要。

用户可以选择他们自己的参考频率,通过引入额外的14位辅助参考频率计数器。

同样地,通过在参考计数器编程字中,设置辅助参考使能位为0,14位辅助参考频率计数器就会被关闭。

在这种情况下,fR2被自动连到C点(÷25块输出)。

通过设置参考计数器编程字里面的fR1-S1 与fR1-S2位,fR1可连接到A或B点。

此时,14位辅助参考频率计数器数据处于“无效”状态。

假如14位辅助参考频率计数器启用(辅助参考位=1),fR2将自动连接到D点(14位计数器输出),fR1可选为连接到A、B或C点,取决于fR1-S1 与fR1-S2位的设置。

表4和图16描述了:辅助参考使能位、fR1-S1 与fR1-S2 位设置的功能。

制器,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。

DDS有如下优点:⑴ 频率分辨率高,输出频点多,可达N个频点(N为相位累加器位数);⑵频率切换速度快,可达us量级;⑶ 频率切换时相位连续;⑷ 可以输出宽带正交信号;⑸ 输出相位噪声低,对参考频率源的相位噪声有改善作用;⑹可以产生任意波形;⑺ 全数字化实现,便于集成,体积小,重量轻,因此八十年代以来各国都在研制和发展各自的DDS产品,如美国QUALCOMM公司的Q2334,Q2220;STANFORD公司的STEL-1175,STEL-1180;AD公司的AD7008,AD9850,AD9854等。

这些DDS芯片的时钟频率从几十兆赫兹到几百兆赫兹不等,芯片从一般功能到集成有D/A转换器和正交调制器。

PLL:Phase Locked Logic 相同步逻辑锁相环的用途是在收、发通信双方建立载波同步或位同步。