跨导运算放大器设计实例n

- 格式:pdf

- 大小:317.72 KB

- 文档页数:26

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

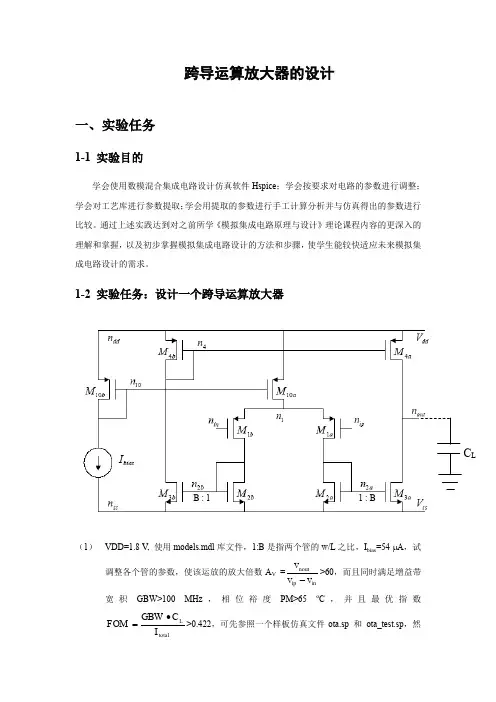

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

折叠式共源-共栅运算跨导放大器姓名:刘淑杰学号:U200714149班级:2007级2班院系:控制系专业:测控技术与仪器同组人姓名:黄大龙葛金炬目录1设计目标 02相关背景知识 (1)(1)课题背景 (1)(2)题目理解 (1)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.3计算DC 增益 (3)3.4计算GBW (5)3.5实际计算 (7)3.6参数验证 (9)4 电路仿真 (10)4.1 用于仿真的电路图 (10)4.2 仿真网表 (10)4.3 仿真波形 (12)5 讨论 (14)收获和建议 (15)参考文献 (17)1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见下表,参考电路原理图如下图所示,用0.35um coms工艺。

Cload DC Gain GBW Vdd Idd3pF 40dB~50dB 300MHz 3V Don’t Care图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识(1)课题背景共源共栅级的普及有两个主要原因。

第一个主要原因是它们由于大输入阻抗,对单级有相当大的增益。

为了得到这个高增益,与输出节点相连的镜像电流源可以用高质量共源共栅镜像电流源实现。

通常,得到这个高增益不会导致任何速度降低,而且有时还会提高速度。

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V, 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54A ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C ,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和C LB : 1 1 : Bota_test.sp ,然后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较;(3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少?最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

模拟集成电路实验——跨导放大器设计实验报告学院:电信学院班级:微电子23班姓名:游晓东学号:2120503069一、设计指标二、电路结构确定电路结构的原因: ① 根据设计指标② 电路结构对称,匹配度高,,Offset CMRR 性能指标好③ 电路稳定性好,只有一个主极点④ 该电路为差分输入,单端输出,共模抑制比大,输出共模点较稳定三、电路原理概述该电路主要由三部分组成:带隙基准电流源、偏置电路、跨导放大器9~21M M 构成一个跨导放大器,其中13M 为尾电流源,向输入的差动对管提供电流偏置。

11,12M M 为输入差分对管,将小信号电压转换成小信号电流。

9,14M M 和10,17M M 为两个对称的电流镜,比例复制小信号电流。

14,15M M 与16,17M M 为共源共栅结构,可以提高输出阻抗和开环增益。

18,19,20,21M M M M 为低压共源共栅电流镜,可以作为单端输出并且提高输出摆幅。

0~8M M 构成偏置电路部分,为跨导放大器提供偏置电流。

22~34,0~2,0~2M M Q Q R R 构成带隙基准电流源部分,为电路提供基准电流源。

四、设计过程1. 分配电流根据静态电流250A μ限制,分配带隙基准电流源部分20A μ,偏置电路部分10A μ(其中每一路2A μ),跨导放大器部分210A μ。

分配14,17M M 的偏置电流14M I 时主要考虑三个指标:,,GBW SR GMGM 要求900~1100/A V μ,因此GM 取1000/A V μ。

由于11GM B gm =⋅,B为14,9M M 的偏置电流之比,因此111000/B gm A V μ⋅= (1)GBW 要求大于3MHZ 。

112LB gm GBWC π⋅=⋅,因此11566/B gm A V μ⋅> (2)SR 要求大于3/V S μ。

92M LB I SRC ⋅=,因此9290M B I A μ⋅> (3)由于9112M ODI gm V =,若OD V 取0.2V ,则由(1)得9100M B I A μ⋅=,由(2)得956.6M B I A μ⋅>,由(3)得945M B I A μ⋅>。

《IC课程设计》报告折叠式共源-共栅运算跨导放大器的设计姓名:王志伟学号:U200713959班级:0707院系:控制系专业:自动化同组人姓名:田绍宇胡月目录1设计目标 (1)2相关背景知识 (2)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.2.1直流工作点分析 (2)3.2.2带宽分析及原件参数计算 (3)3.2.3直流增益的小信号模型分析 (4)3.3 计算参数验证 (5)4电路仿真 (5)4.1交流特性仿真 (7)4.2最大输出摆幅仿真 (9)4.3共模输出的仿真验证 (11)5讨论 (12)6收获和建议 (13)7参考文献 (14)摘要:折叠式共源共栅结构的运算放大器不仅能提高增益、增加电源电压噪声抑制比、而且在输出端允许自补偿。

1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见表1,参考电路原理图如下图所示,用0.35um coms工艺。

图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识随着集成电路技术的不断发展,高性能运算放大器得到广泛应用,其性能直接影响电路及系统的整体性能。

折叠式共源共栅运算放大器具有二阶优化性能,因此设计一个实用价值的折叠式共源共栅运算放大器是非常有现实意义的。

CMOS管的参数并不能通过简单的理论计算进行准确的预测,在给定的工艺条件下,理论计算出的管子宽长不考虑实际情况下工艺条件等诸多外界因素,仿真的结果会和设计指标有很大的差距。

具有较小跨导的跨导放大器结构的一个比较设计方法摘要:一个家用CMOS运算放大器(OTAS)已经被设计成具有非常小的跨导以保证晶体管在温和的反转中工作。

许多的OTA设计方案如传统的利用电流转换、浮栅和大容量驱动技术都已经被讨论过。

这些方案的一些性能特点如功耗、有源硅区、信号噪音比我们也进行了一些详细的比较。

我们已经在一个1.2μm的n阱COMS工艺和工作电源2.7V 的条件下爱制备出了这种跨导放大器。

并且芯片的测试结果与理论计算结果也有很好的吻合。

引言由于人类身体的相对缓慢的电活动在医疗电子设备、有源滤波器和低截止频率等领域是很必要的。

低频电路应用的另一个领域是斜坡生成模拟---数字转换器(ADC)测试和神经网络领域。

因此,我们致力于研究出一个能够在低频率下工作的开发集成解决方案的电路。

对于一个运算跨导放大器—电容(OTA-C)滤波器来实现这样一个低频率来说就意味着需要大型电容器和非常低的跨导。

因此,我们有两个完全独立的角度去处理这个问题。

一种是设计出具有非常低的跨导(一般没伏几微毫安)、高线性;另一种是在芯片上实现大电容(通常是几纳法)。

按照上述思路,我们来分析不同工艺取得低跨导,我们在功耗、有源硅区、信号噪声比(SNR)等性能特性方面针对不同的方法已经开展了比较研究。

特别强调了在温和反转区的MOS晶体管的操作设计以便在功率和面积要求上达到一个较好的折中可能。

OTA拓扑在温和的反转中我们设计四种不同的OTA拓扑结构,在相同的跨导值为10nA/v的所有MOSFET模型中我们用一个方程式来权衡相关的设计参数如功耗、有源硅区和SNR。

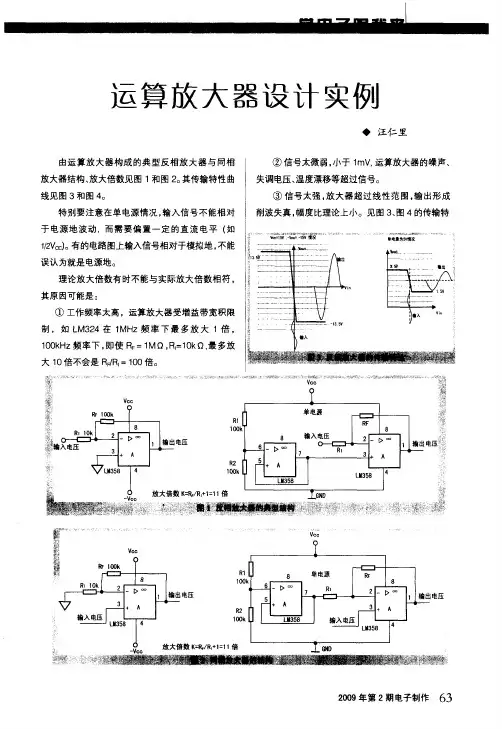

A参考的OTA设计A如图一所示,这个OTA主要由两个不同部分(M1和M2)和三个电流镜。

放大器的全部跨导Gm跟M1、M2相同(M3=M4=M5=M6,M7=M8)。

根据所需的跨导值,此基本拓扑电流的结构水平可以非常小(大约在微微安培每伏),这就会使得W/L的比值为0.001甚至更少。

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

采用共源共栅差分结构实现差分运算跨导放大器的设计-设计应用近十几年来,移动电话、掌上电脑、笔记本电脑等便携式设备及医疗、测试仪器的迅猛发展拉动了具有低压差、低功耗的LDO(LowDropout)稳压器的快速发展。

当前,LDO稳压器已经实现500mV以下的压差。

在LDO稳压器中,电源是主要的噪声源。

尤其在高频,电源电压的变化为系统稳定性带来的影响更大。

误差放大器是LDO稳压器的重要组成部分,其稳定性与整个LDO稳压器系统的稳定性能密切相关。

因此,研究电源电压变化对LDO稳压器中误差放大器的影响是非常必要的。

电源抑制比(PSRR)衡量模拟系统对抗电源噪声的能力,是放大器一个非常重要的性能指标。

本文设计的误差放大器为带共源共栅电流镜负载的共源共栅差分运算跨导放大器。

它应用在一款超低功耗的LDO线性稳压器中,采用共源共栅差分结构,提高了PSRR,低频达到119dB。

同时,该放大器具有高共模抑制比(CMRR),低频达到106dB,静态电流不超过0.62μA。

OTA的设计与仿真PSRR定义为输入端到输出端的电压增益与电源到输出端的电压增益之比,即Gm(s)和Gmp(s)分别是输入端到输出端、电源到输出端之间的跨导。

在LDO线性稳压器中,只有VDD一个低压电压源供电,因此,这里只讨论VDD的PSRR。

电流镜负载放大器是LDO线性稳压器中误差放大器的基本结构,如图1所示。

VDD通过M3、M4,为输出端引入一个电流(go4+sCp4)VDD,通过M3、M1、M2,为输出端引入一个电流(go1+sCp1)VDD,则式中,go为输出导纳,Cp=CGD+CDB。

图1基本电流镜负载差分电路对这种结构的放大器的PSRR进行Spice仿真,如图2所示。

从图2中可以看出,低频时的PSRR只能达到47.6dB,远远不能达到LDO 线性稳压器的性能要求。

从(2)式可以看出,减小M1、M4的输出导纳,可以提高低频时的PSRR,减小M1、M4的寄生电容,即减小MOS管的尺寸,可以提高高频时的PSRR。

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp ,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

模拟集成电路课程设计跨导放大器学院:电信学院班级:微电子92组长:曾云霖(09053057)组员:黄雄(09053042)蒋仪(09053043)跨导放大器设计设计题目:基于所给的CMOS工艺设计一款跨导放大器.跨导放大器的特点是具有非常大的输出阻抗,将输入电压转换成电流输出,相当于压控电流源。

该电路的设计同样需要包括偏置电压电流产生电路。

设计指标:设计指标:(供参考)性能参数测试条件参数指标负载电容30pF电源电压范围 2.5~5.5V静态电流VDD=3。

6V,Temp=27℃〈250μA输出摆幅输入共模电压VDD =3。

6V,Temp=27℃VDD =3。

6V,Temp=27℃0.6~1。

2V0。

1~1V开环增益(低频)VDD =3。

6V,Temp=27℃1800~2200单位增益带宽VDD =3。

6V,Temp=27℃>3MHz相位裕度VDD =3。

6V,Temp=27℃〉60°PSRR(低频)VDD =3。

6V,Temp=27℃>65dB跨导(低频)VDD =3.6V,Temp=27℃(900~1100)μA /V 转换速率VDD =3。

6V,Temp=27℃>3V/μs设计要求:1.确定设计指标(以上指标供参考,可以进行适当修改,但需说明原因); 2.根据设计指标,可以在参考电路结构基础上确定参数和改进设计,也可以查找文献采用其它结构的电路或创造新的电路结构进行设计;3.阅读模型文件,了解可以选用的器件类型与尺寸范围;4.手工设计:根据拟定的设计指标,初步确定满足指标的各元件的模型与参数:MOS:沟道长度与宽度,并联个数;电阻:宽度、长度、串并联个数;电容:宽度、长度、并联个数;三极管:并联个数.5.采用全典型模型,27℃,验证电路是否满足设计指标;6.设计偏置电路:a)选定电路结构;b) 手工设计:确定各元件的模型与尺寸;c)采用全典型模型,仿真验证偏置电流源的性能;7.将偏置电路和主体电路合在一起仿真,采用全典型模型,27℃,VDD=3.6V,要求电路达到“设计指标"要求,否则应对电路结构和参数进行修改与优化,直至满足要求(可能需要多次调整),并应包括以下内容:a)一输入端固定为0。