CMOS恒跨导运算放大器设计

- 格式:ppt

- 大小:1.13 MB

- 文档页数:43

具有恒定跨导的Rail-to-Rail CMOS运算放大器设计指导陈斯(徐州师范大学物理系电子科学教研室)注:文章中有很多关于MOS方面的基础知识,可能对于你们来说比较陌生,可以去找一些关于这方面的书籍看看。

下学期我会给你们做专门的讲解的。

你们先作个大概的了解,并确定具体的方向。

1引言近年来,随着集成电路工艺尺寸的不断减小,低电压的发展趋势越来越快。

下图为半导体工艺与电源电压的关系。

从图中可以看出,电压随着工艺最小尺寸的减小而不断降低。

电压减小的原因是因为尺寸的减小导致了器件的击穿电压的减小。

此外数字电路的功耗正比于电源电压的平方,因此,为了减小功耗必须降低电源的电压。

但是从模拟电路设计者来看,电源电压的减小会导致模拟信号动态范围的减小。

如果MOS管的域值电压随着电源的降低而等比减小的话,动态范围就不会受到严重的影响。

但由于数字逻辑的原因,域值电压不能大幅地减小,所以低电压会对电路的设计带来一定的影响。

2 一般原理在模拟电路和数模混合电路中,对于低电压的追求逐渐成为集成电路的一种时尚。

然而低电压导致了运算放大器输入共模范围的降低,传统的PMOS或NMOS差分对输入已不能满足大的输入共模范围的要求。

为解决这一瓶颈,rail-to-rail运算放大器随之而产生。

通常的Rail-to-Rail运放采用两级结构,运放的输出级可以采用简单的class-A或class-AB来实现,难点在于输入级的设计。

输入级一般采用PMOS和NMOS并联的互补差分结构,但其跨导在整个共模输入范围内变化两倍。

这种跨导的变化不仅影响环路的增益, 也会影响运放的频率补偿。

同时,由于输入信号是rail-to-rail ,具有很高的信噪比,因此要求整个rail-to-rail 运放的输入级保持恒定的跨导(g m )。

一般来说,运算放大器的输入级都采用差分放大器的输入模式。

在CMOS 工艺中,差分放大器可以通过PMOS 或NMOS 的差分对来实现。

2004 年 6月 JOURNAL OF CIRCUITS AND SYSTEMS June , 2004 文章编号:1007-0249 (2004) 03-0069-04一种前馈型全摆幅恒跨导准恒增益CMOS 运放设计*吴金, 周震(东南大学 微电子中心,江苏 南京 210096)摘要:设计了一种适合在低电源电压下工作的前馈型输入级放大结构,在全摆幅的动态工作范围内,输入级跨导保持不变,采用负载电流补偿以保证增益近似恒定,输出采用前馈型AB 类输结构,实现全摆幅输出。

关键词:运放;恒跨导;准恒增益;全摆幅中图分类号:TN43 文献标识码:A1 引言近年来,随着各种便携式电子产品的广泛应用,对低压低功耗电子系统提出了越来越高的要求。

CMOS 模拟电路工作电压的降低,遇到来自工艺方面的限制,即阈电压V TH 无法按比例缩小,同时电路性能的保持甚至改善变得更加困难。

低压下,随着噪声影响的所占比重的增加,迫切要求有效信号能够达到DD V GND ~的全电平摆幅范围,Rail-To-Rail (RTR )CMOS 运算放大器就是针对以上要求而提出的一种适合于低压工作的高性能模拟单元电路[1-2]。

传统的RTR CMOS 运放主要采用了互补的N 型和P 型差分对作为输入级,采用负反馈跨导线性(TL )环路控制总输入跨导的恒定,并采用Class AB 结构[3]以实现全摆幅的信号输出。

RTR 运放恒定跨导或增益的控制需要采用各种反馈或前馈结构。

前馈是指输入信号的一部分通过并联的非主通道达到输出,与信号反馈的传输方向相反。

前馈可提高控制的响应速度,而反馈有利于系统稳定性的提高。

针对传统RTR CMOS 运放反馈控制电路复杂、速度限制明显、以及负载电流变化导致增益不稳等主要缺陷,提出了简单前馈控制和负载电流补偿的改进方法,以期达到简化电路设计、提高速度并稳定增益的目的。

2 前馈型恒跨导输入级设计MP 1和MP 2为P 型输入差分对,MN 1和MN 2为N 型输入差分对,MP 3和MN 3组成串连MOS 二级管,MP 1、MN 1、MP 3、MN 3四个MOSFET 组成一个闭合TL 前馈控制环路,电路约束关系为)3()3()1()1(MN GS MP GS MN GS MP GS V V V V +=+。

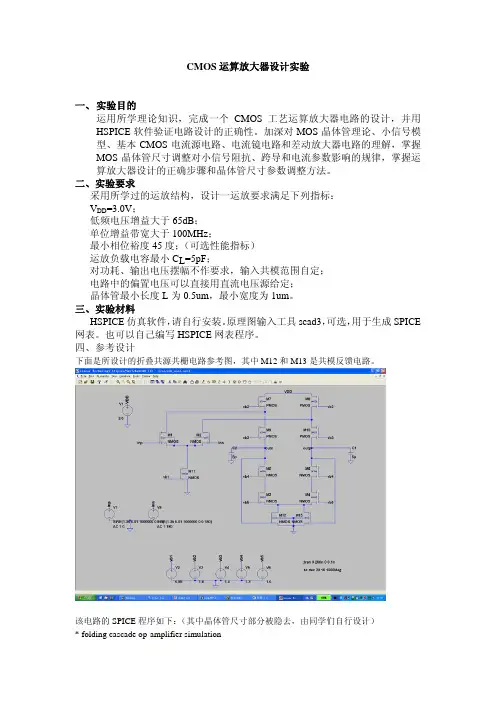

CMOS运算放大器设计实验一、 实验目的运用所学理论知识,完成一个CMOS工艺运算放大器电路的设计,并用HSPICE软件验证电路设计的正确性。

加深对MOS晶体管理论、小信号模型、基本CMOS电流源电路、电流镜电路和差动放大器电路的理解,掌握MOS晶体管尺寸调整对小信号阻抗、跨导和电流参数影响的规律,掌握运算放大器设计的正确步骤和晶体管尺寸参数调整方法。

二、实验要求采用所学过的运放结构,设计一运放要求满足下列指标:V DD=3.0V;低频电压增益大于65dB;单位增益带宽大于100MHz;最小相位裕度45度;(可选性能指标)运放负载电容最小C L=5pF;对功耗、输出电压摆幅不作要求,输入共模范围自定;电路中的偏置电压可以直接用直流电压源给定;晶体管最小长度L为0.5um,最小宽度为1um。

三、实验材料HSPICE仿真软件,请自行安装。

原理图输入工具scad3,可选,用于生成SPICE 网表。

也可以自己编写HSPICE网表程序。

四、参考设计下面是所设计的折叠共源共栅电路参考图,其中M12和M13是共模反馈电路。

该电路的SPICE程序如下:(其中晶体管尺寸部分被隐去,由同学们自行设计)* folding cascade op-amplifier simulationM1 N006 inp N004 N004 NMOS l=xu w=xuM2 N005 inn N004 N004 NMOS l=xu w=xuM3 N002 vb5 N001 0 NMOS l=xu w=xuM4 N003 vb5 N001 0 NMOS l=xu w=xuM5 outn vb4 N002 0 NMOS l=xu w=xuM6 outp vb4 N003 0 NMOS l=xu w=xuM9 outn vb3 N006 VDD PMOS l=xu w=xuM10 outp vb3 N005 VDD PMOS l=xu w=xuM7 N006 vb2 VDD VDD PMOS l=xu w=xuM8 N005 vb2 VDD VDD PMOS l=xu w=xuM11 N004 vb1 0 0 NMOS l=1u w=xu* 共模反馈晶体管,工作在深线性区M12 N001 outn 0 0 NMOS l=0.5u w=xxxuM13 N001 outp 0 0 NMOS l=0.5u w=xxxu*将共模电压设为参数:vdm.param vdm=0* 偏置电压源,实际电压值需要同学们根据过驱动电压计算V1 VDD 0 3.0C1 outp 0 15pC2 outn 0 15pV2 vb1 0 0.8V3 vb2 0 1.9V4 vb3 0 1.55V5 vb4 0 1.1V6 vb5 0 0.88* 直流分析电压源和瞬态分析电压源V7 inp Vcm dc vdm SIN(0 0.0001 100000 0 0 0) AC 1V8 Vcm inn dc vdm SIN(0 0.0001 100000 0 0 0)V9 Vcm 0 1.32* PMOS和NMOS晶体管模型.model nmos nmos LEVEL=1 VTO=0.7 GAMMA=0.45 PHI=0.9+ NSUB=9e+14 LD=0.08e-6 UO=350 LAMBDA=0.1+ TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+ MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8.model pmos pmos LEVEL=1 VTO=-0.8 GAMMA=0.4 PHI=0.8 + NSUB=5e+14 LD=0.09e-6 UO=100 LAMBDA=0.2+ TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+ MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5E-8* the option line is important, please copy this line if you use hspice.option POST ACCT NOMOD ACCURATE list ACOUT=0.op* 大信号差分信号的直流扫描方式.dc vdm -1 1 0.001* 瞬态分析命令.tran 5n 100u 0n* 交流小信号分析,从10Hz到2GHz,每10倍频程10个点.ac dec 10 10 2G* 交流分析和瞬态分析的输出信号定义,vdb表示输出分贝值,vp表示输出相位.probe vdb(outp,outn) vp(outp,outn)* id表示漏端的电流,vm表示电压的幅值.probe id(M11), id(M1), id(M3), id(M5), id(M7), id(M9), vm(outp,outn), vm(inp,inn).end参考结果:低频增益78dB,相位阈度45.7度,单位增益带宽125MHz,输入信号100kHz 时的增益为64dB。

恒跨导高摆率轨对轨运算放大器的设计张伟娟;邹伟;徐坤玉【摘要】本文在分析MOS管恒跨导输入级和AB类输出级运算放大器的基础上设计了一个高摆率、恒跨导的轨对轨运算放大器。

在输入级中采用了齐纳二极管的稳压原理,保证Rail-to-Rail运算放大器的输入跨导恒定。

为了实现高转换率,本文采用了一种新型的压摆率提高电路。

另外,为了提高系统的稳定性,采用了控制零点的米勒补偿进行频率补偿。

采用CSMC 0.5 μm CMOS工艺,用H-Spice对整个运算放大器电路进行仿真验证,结果表明运算放大器输入输出范围基本达到满摆幅,最大跨导变化率仅为3.9%和具有较高的增益和摆率。

%Based on analyzing MOS transistor constant-gm input stage and class AB output of operational amplifier, a high-slew-rate and constant-gm, rail-to-rail operational amplifier was designed. A Zener-diode structure was inserted in the input stage to keep the gm of the input stage constant. A novel slew rate enhancement circuit was implemented to achieve a high slew rate. In addition, the miller compensation was adopted to improve the stability of the system. The circuit was realized in CSMC 0.5 μm CMOS process and is simulated by H-Spice for whole of operational amplifier. The simulated results showed that the operational amplifier has rail-to-rail input and output and the maximum gm fluctuation is only 3.9%. It has quality of high gain and rate.【期刊名称】《电子测试》【年(卷),期】2011(000)011【总页数】4页(P58-61)【关键词】恒跨导;轨对轨运算放大器;摆率【作者】张伟娟;邹伟;徐坤玉【作者单位】兰州交通大学电子与信息工程学院,甘肃兰州730070;兰州交通大学电子与信息工程学院,甘肃兰州730070;兰州交通大学电子与信息工程学院,甘肃兰州730070【正文语种】中文【中图分类】TN4320 引言运算放大器是集成电路中应用最广泛的电路单元之一,它是模拟及数模混合电路中的一个重要模块。

目录1 引言 (1)2 软件介绍 (3)3 运算放大器设计基础 (5)3.1运放的主要性能指标 (5)3.2运算放大器的基本结构 (6)3.2.1全差分运放 (6)3.2.2套筒式结构 (7)3.2.3折叠式结构 (8)4 系统总体设计 (10)4.1电路设计的整体结构 (10)4.2 主放大电路设计 (11)4.3 偏置电路的设计 (13)4.4 输出级的设计 (13)4.5 共模反馈的设计 (14)4.6 总体布局 (15)5 仿真与分析 (17)5.1运放直流与交流特性 (17)5.2噪声特性分析 (19)5.3电源抑制比 (19)5.4设计指标 (20)5.5放大器参数 (21)6 版图设计与分析 (22)6.1 L-Edit介绍 (22)6.2版图设计规则 (22)6.3基本器件版图设计 (23)6.3.1 NMOS版图设计 (23)6.3.2 电容电阻版图设计 (24)6.4版图的总体设计 (26)6.4.1主电路模块版图 (26)6.4.2偏置模块版图 (27)6.4.3输出模块版图 (27)6.4.4整体模块版图 (28)6.5 LVS版图比对 (29)7 结论 (31)谢辞 ................................................................................................... 错误!未定义书签。

参考文献 .. (32)附录1 (33)附录2 (35)1 引言集成运算放大器(Integrated Operational Amplifier)简称集成运放,是由多个CMOS管与电容电阻通过耦合方式实现提高增益的模拟集成电路[1]。

集成运放具有增益高、输入阻抗大、输出阻抗低、共模抑制比高和失调与漂移性小等优点,而且当输入电压值为零时,输出值也为零。

集成运放是构成常用集成电路系统的通用模块[2] [3]。

CMOS高性能运算放大器研究与设计CMOS高性能运算放大器研究与设计引言:随着科技的不断进步和应用的广泛推广,运算放大器(Operational Amplifier,简称Op-Amp)作为一种重要的模拟电路器件,得到了广泛的关注和应用。

CMOS (Complementary Metal-Oxide-Semiconductor)技术由于其功耗低、集成度高等优势,被广泛应用于运算放大器的研究和设计中。

本文将介绍CMOS高性能运算放大器的研究与设计,主要包括运算放大器的基本原理、运算放大器的基本电路结构、CMOS技术的特点和优势、CMOS高性能运算放大器的设计方法和优化技术等方面。

一、运算放大器的基本原理运算放大器是一种特殊的差动放大器,它能够实现电压放大、电流放大、功率放大等功能。

运算放大器有两个输入端,一个非反相输入端和一个反相输入端;有一个输出端和一个电源端,电源端一般有正电源和负电源两个。

在理想情况下,运算放大器具有无限的增益、无限的输入阻抗和零的输出阻抗。

但实际情况下,由于运算放大器的内部结构等因素的限制,无法完全满足理想的条件。

因此,在运算放大器的设计中,需要考虑如何提高增益、输入阻抗和输出阻抗等性能指标。

二、运算放大器的基本电路结构运算放大器的基本电路结构由差动放大器、电压放大器和输出级组成。

差动放大器用于实现输入信号的差分放大,电压放大器用于实现信号的放大,输出级用于驱动负载电阻。

差动放大器由两个晶体管组成,一个晶体管作为非反相输入端,另一个晶体管作为反相输入端。

通过调节两个晶体管的尺寸比例,可以实现不同的放大倍数。

电压放大器由级联的共源放大器组成,通过逐级放大,实现信号的放大。

输出级由差分放大器和输出级筛选电路组成,通过差分放大器将信号转化为可驱动负载电阻的电流信号,再经过输出级筛选电路,将电流信号转化为电压信号。

三、CMOS技术的特点和优势CMOS技术是一种基于金属-氧化物-半导体(MOS)结构的半导体制造技术。

1.5V低功耗CMOS恒跨导轨对轨运算放大器邓红辉;尹勇生;高明伦【期刊名称】《科技导报》【年(卷),期】2009(0)23【摘要】运算放大器是模拟集成电路中用途最广、最基本的部件。

随着系统功耗及电源电压的降低,传统的运算放大器已经不能满足低压下大共模输入范围及宽输出摆幅的要求。

轨对轨运算放大器可以有效解决这一问题,然而传统的轨对轨运算放大器存在跨导不恒定的缺点。

本文设计一种1.5V低功耗CMOS恒跨导轨对轨运算放大器,输入级采用最小电流选择电路,不仅实现了跨导的恒定,而且具有跨导不依赖于理想平方律模型、MOS管可以工作于所有区域、移植性好的优点。

输出级采用前馈式AB类输出级,不仅能够精确控制输出晶体管电流,而且使输出达到轨对轨全摆幅。

所设计的运算放大器采用了改进的级联结构,以减小运算放大器的噪声和失调。

基于SMIC0.18μm工艺模型,利用Hspice软件对电路进行仿真,仿真结果表明,当电路驱动2pF的电容负载以及10kΩ的电阻负载时,直流增益达到83.2dB,单位增益带宽为7.76MHz,相位裕度为63°;输入输出均达到轨对轨全摆幅;在整个共模输入变化范围内跨导变化率仅为2.49%;具有较高的共模抑制比和电源抑制比;在1.5V低压下正常工作,静态功耗仅为0.24mW。

【总页数】5页(P57-61)【关键词】轨对轨;恒跨导;最小电流选择电路;前馈式AB类输出级【作者】邓红辉;尹勇生;高明伦【作者单位】合肥工业大学电子科学与应用物理学院微电子设计研究所【正文语种】中文【中图分类】TN402【相关文献】1.3.3V/0.18μm恒跨导轨对轨CMOS运算放大器的设计 [J], 马玉杰;高俊丽;后永奇;耿晓勇;杨建红2.一种恒跨导轨对轨CMOS运算放大器的设计 [J], 薛超耀;韩志超;欧健;黄冲3.一种恒跨导轨到轨CMOS运算放大器的设计 [J], 乔红斌4.一种恒跨导轨到轨CMOS运算放大器的设计 [J], 乔红斌5.一种低压恒跨导轨对轨CMOS运算放大器设计 [J], 高瑜宏; 李俊龙因版权原因,仅展示原文概要,查看原文内容请购买。

cmos运算放大器设计实例-回复如何设计一个CMOS运算放大器。

CMOS运算放大器是一种常用的电路结构,可用于放大输入信号并增强其幅度。

本文将以CMOS运算放大器设计为主题,逐步介绍设计过程。

第一步:确定设计需求在设计CMOS运算放大器之前,需要明确设计需求,例如增益、带宽、输入阻抗和输出阻抗等。

这些需求将决定电路拓扑、晶体管尺寸和工作点设置等。

第二步:选择电路拓扑根据设计需求,选择合适的电路拓扑。

常用的CMOS运算放大器拓扑包括传统的两级差分放大器、折叠式运算放大器和共源共栅放大器等。

选择合适的拓扑将决定电路的性能和可靠性。

第三步:确定晶体管尺寸根据电路拓扑和设计需求,确定每个晶体管的尺寸。

晶体管的尺寸直接影响到电路的增益和带宽等性能指标。

根据经验公式和手册中提供的参数,计算每个晶体管的尺寸。

第四步:设置工作点在设计CMOS运算放大器时,需要设置每个晶体管的工作点,以确保电路正常工作。

通过设定适当的偏置电压和电流,使每个晶体管处于合适的工作区域,以获得最佳性能。

第五步:分析电路性能在设计CMOS运算放大器之前,需要进行详细的电路性能分析。

包括直流增益、交流增益、输入和输出阻抗、带宽等。

通过数学模型和电路分析软件,可以预测电路的性能,并进行必要的调整和优化。

第六步:模拟仿真在实际设计CMOS运算放大器之前,进行详细的模拟仿真是必不可少的。

使用专业的电路仿真软件,输入设计参数和模型,对电路进行仿真和分析。

通过仿真结果,可以验证设计的准确性和性能。

第七步:布局设计在完成电路设计和仿真之后,进行布局设计是下一步的关键。

合理布局电路和导线,减少晶体管之间的互容和互感等干扰,以确保电路能够正常工作。

第八步:制造和测试设计完成后,将电路发送到制造厂商进行制造。

制造完成后,对电路进行测试和调试,以确保电路的性能和可靠性。

总结:设计一个CMOS运算放大器需要经过多个步骤,包括确定设计需求、选择电路拓扑、确定晶体管尺寸、设置工作点、分析电路性能、模拟仿真、布局设计和制造测试等。

模拟集成电路课程设计跨导放大器学院:电信学院班级:微电子92组长:曾云霖(09053057)组员:黄雄(09053042)蒋仪(09053043)跨导放大器设计设计题目:基于所给的CMOS工艺设计一款跨导放大器.跨导放大器的特点是具有非常大的输出阻抗,将输入电压转换成电流输出,相当于压控电流源。

该电路的设计同样需要包括偏置电压电流产生电路。

设计指标:设计指标:(供参考)性能参数测试条件参数指标负载电容30pF电源电压范围 2.5~5.5V静态电流VDD=3。

6V,Temp=27℃〈250μA输出摆幅输入共模电压VDD =3。

6V,Temp=27℃VDD =3。

6V,Temp=27℃0.6~1。

2V0。

1~1V开环增益(低频)VDD =3。

6V,Temp=27℃1800~2200单位增益带宽VDD =3。

6V,Temp=27℃>3MHz相位裕度VDD =3。

6V,Temp=27℃〉60°PSRR(低频)VDD =3。

6V,Temp=27℃>65dB跨导(低频)VDD =3.6V,Temp=27℃(900~1100)μA /V 转换速率VDD =3。

6V,Temp=27℃>3V/μs设计要求:1.确定设计指标(以上指标供参考,可以进行适当修改,但需说明原因); 2.根据设计指标,可以在参考电路结构基础上确定参数和改进设计,也可以查找文献采用其它结构的电路或创造新的电路结构进行设计;3.阅读模型文件,了解可以选用的器件类型与尺寸范围;4.手工设计:根据拟定的设计指标,初步确定满足指标的各元件的模型与参数:MOS:沟道长度与宽度,并联个数;电阻:宽度、长度、串并联个数;电容:宽度、长度、并联个数;三极管:并联个数.5.采用全典型模型,27℃,验证电路是否满足设计指标;6.设计偏置电路:a)选定电路结构;b) 手工设计:确定各元件的模型与尺寸;c)采用全典型模型,仿真验证偏置电流源的性能;7.将偏置电路和主体电路合在一起仿真,采用全典型模型,27℃,VDD=3.6V,要求电路达到“设计指标"要求,否则应对电路结构和参数进行修改与优化,直至满足要求(可能需要多次调整),并应包括以下内容:a)一输入端固定为0。

cmos运算放大器设计实例概述及解释说明1. 引言1.1 概述本篇文章是关于CMOS运算放大器设计实例的概述与解释说明。

在现代电路设计中,运算放大器被广泛应用于模拟电路和信号处理领域,在各种电子设备和系统中扮演重要角色。

而CMOS(互补金属-氧化物-半导体)技术作为一种主流的集成电路制造工艺,具有低功耗、高可靠性和高集成度等优势,并且适合用于低压低功耗的移动设备和便携式电子产品。

1.2 文章结构本篇文章将分为五个部分进行详细讲解。

首先,在引言部分对文章进行总体概述,介绍了CMOS运算放大器的设计原理以及本文的目的。

接下来,在第二部分将详细介绍CMOS技术、运算放大器基本原理以及CMOS运算放大器的特点。

然后,第三部分将重点讲解CMOS运算放大器设计的步骤,包括整体设计方案确定、差模放大器设计和分析以及单端放大器设计和优化。

在第四部分,我们将给出一个具体的样例电路,并对其进行实现和分析,包括电路图和参数规格说明、差模输入阶段设计和性能分析,以及输出级设计和性能分析。

最后,在第五部分我们将总结实验结果并进行相应的讨论,并提出一些建议用于改进建议。

1.3 目的本文的目的是通过对CMOS运算放大器设计实例的详细解释与说明,帮助读者更好地了解CMOS技术、运算放大器的基本原理以及CMOS运算放大器的特点。

同时,通过具体样例电路的实现和分析,展示CMOS运算放大器设计步骤,并总结出实验结果并进行讨论,从而为读者提供有关CMOS运算放大器设计方面的参考与指导。

2. CMOS运算放大器设计原理:2.1 CMOS技术简介:CMOS(Complementary Metal-Oxide-Semiconductor)技术是一种常用的集成电路制造技术,它采用半导体材料和金属氧化物栅结构。

相比于其他晶体管技术,CMOS具有低功耗、高集成度和抗辐射等优点,在现代电子领域得到广泛应用。

2.2 运算放大器基本原理:运算放大器(Operational Amplifier,简称OA)是一种重要的模拟电路元件,它是差分放大器的一种改进形式。

cmos运算放大器设计实例-回复CMOS运算放大器设计实例引言:CMOS(互补金属氧化物半导体)技术是现代电子电路设计中最常用的技术之一。

CMOS运算放大器是CMOS技术的重要应用之一,在模拟电路设计领域有着广泛的应用。

本文将以CMOS运算放大器设计实例为主题,详细介绍设计过程的每一步及背后的原理。

第一部分: 设计目标和规范(200字)在进行CMOS运算放大器的设计前,需要明确设计目标和规范。

我们假设设计目标是设计一个具有高增益、低功耗和高输入阻抗的运算放大器。

规范要求在供电电压为3V时,输出电压范围应该最大化,并且放大器的带宽应该在1MHz以上。

第二部分: 放大器框图设计(400字)首先,我们从设计CMOS运算放大器的框图开始。

一个标准的CMOS运算放大器通常由差分输入级、差分放大级和输出级组成。

差分输入级负责提供高输入阻抗和抑制共模噪声,差分放大级负责放大输入信号,输出级驱动输出负载。

第三部分: 偏置电流设计(400字)在设计CMOS运算放大器时,需要对差分放大级的偏置电流进行设计。

偏置电流对放大器的性能有很大的影响。

通常,偏置电流越大,放大器的增益越大,但功耗也随之增加。

我们需要在增益和功耗之间找到一个平衡点。

第四部分: 带宽和相位裕度设计(400字)为了实现高带宽和良好的相位裕度,我们需要进行差分放大级的交流增益调节。

调节交流增益可以改变放大器的带宽特性,以满足设计规范中对带宽的要求。

此外,相位裕度也是一个非常重要的指标,它衡量了放大器在高频时能否保持稳定的增益和相位性能。

第五部分: 输出级设计(300字)在设计输出级时,我们需要考虑输出电压摆幅和输出电流的要求。

输出级通常采用共射极(source follower)结构,能够提供较大的输出驱动能力。

通过合理设计输出级,我们可以达到设计规范中对输出电压范围的要求,并且保持较低的功耗。

第六部分: 电源抑制和共模抑制设计(200字)电源抑制和共模抑制是CMOS运算放大器设计中需要考虑的两个重要指标。

【精品】CMOS运算放⼤器的分析及设计毕业论⽂(此⽂档为word格式,下载后您可任意编辑修改!)摘要随着集成电路⼯艺的发展,CMOS电路由于其低成本、低功耗以及速度的不断提⾼,在集成电路中获得越来越⼴泛的应⽤。

CMOS运算放⼤器也因其独特的性能优势常被⽤于模拟集成系统或⼦系统中,它的性能的好坏直接决定了整个模拟集成系统性能的好坏。

因此,有必要对⽤CMOS运算放⼤器进⾏深⼊的学习和研究。

CMOS运算放⼤器作为模拟集成电路最重要的功能模块,其设计⼀般包括以下⼏个步骤:确定设计要求;设计或综合;仿真;⼏何版图设计;版图后仿真;流⽚;测试。

本论⽂主要对两级CMOS运算放⼤器进⾏了前端设计及仿真。

论⽂在确定了两级CMOS 运放设计规范要求的基础上,设计了两级CMOS运算放⼤器的基本电路结构,分析了各组成模块的电路功能,,通过分析性能参数与MOS管⼏何参数的关系,得到了电路中各MOS管的宽长⽐。

论⽂在介绍仿真环境OrCAD的结构特点及其⼯作性能的基础上,对所设计的电路进⾏了PSpice软件仿真,得到了设计电路的直流⼯作点、瞬态以及频率特性的仿真结果。

仿真结果分析表明所设计的电路符合预期的设计要求和设计指标,也验证了设计的两级CMOS运算放⼤器的可靠性和可⾏性。

关键词:CMOS;运算放⼤器;PSpice仿真;⼩信号放⼤;频率响应AbstractWith the development of CMOS technique, CMOS integrated circuits and continuously improved speed. As the CMOS process widely used because of its unique performance.As the most important functional module in analog integrated circuits, the design of CMOS operational amplifier includes several steps as follows: determination design requirements, design or synthesis, simulation, design geometric layout, post-layout simulation, tape-out and test. The formal steps of the design of the two-stage CMOS operational amplifiers was provided in this paper, and the basic circuit structures of the two-stage CMOS operational amplifier was introduced. Based on determining the op-amp design specifications, the relationship between performance parameters and transistor geometry parameters was analyzed and the ratio of the transistors width to length was calculated. As a kind of simulation tool, the structural characteristics and work performance of OrCAD was described in detail. The feasibility of the design was determined by using PSpice simulation. Analysis of bias point, transient and the frequency characteristics of the circuit completed in this paper, and the simulation results showed that the designed circuit meets the design requirements and targets, also design the reliability and feasibility of the two-stage CMOS operational amplifier comfired.Key words: CMOS;Operational amplifier;Pspice simulation;Small signal amplification;Frequency response毕业设计(论⽂)原创性声明和使⽤授权说明原创性声明本⼈郑重承诺:所呈交的毕业设计(论⽂),是我个⼈在指导教师的指导下进⾏的研究⼯作及取得的成果。

收稿日期:2005-08-31基金项目:深圳市天瑞高鑫实业有限公司基金资助项目。

作者简介:谢强(1981-),男,硕士研究生,主要从事低功耗CMO S 运算放大器设计方面的研究。

2006年4月宇航计测技术Apr .,2006第26卷 第2期Journal of Astronautic Metrology and MeasurementVol .26,No .2文章编号:1000-7202(2006)02-0060-05 中图分类号:TN432.1 文献标识码:A一种恒跨导轨对轨输入级运算放大器的设计谢 强 李宏建 朱家俊(湖南大学应用物理系,长沙410082) 摘 要 提出了一种恒跨导轨对轨输入级的结构,从理论上详细分析了这种结构的可行性和优越性,在输入MOS 差分对管处于强反型区和弱反型区时,它都能提供几乎不变的跨导,且采用0.6μmC MOS 工艺对这种运算放大器进行了模拟仿真,其结果与理论值很相符合。

关键词 CMOS 运算放大器 恒跨导 轨对轨Design of A CMOS Op -Amp with Constant -g m andRail -to -Rail Input StageXIE Qiang LI Hong -jian ZHU Jia -jun(Department of Applied Physics ,Hunan University ,Changsha 410082) A bstract A constant -g m Rail -to -Rail CMOS operational -a mplifier input stage is designed ,Conceptuallythe feasibility and the superiority of this architectur e is discussed in details .It pr ovides nearly constant net trans -conductance independent of input transistor operating region (strong ,moderate or weak inversion ),and the Op -Amp with this constant -g m and Rail -to -Rail input stage is simulated in 0.6μm C MOS process ,The re -sults are accorded with the before -mentioned analysis ver y well . Key words CMOS Operational a mplifier Constant -g m Rail -to -Rail1 引 言近年来,在笔记本电脑、移动通信、植入人体的生物医学装置等便携设备飞速发展的推动下,低压低功耗运算放大器已成为低电压电路的重要组成部分[1-3],所供电压的减小导致了输入共模电压范围的减小,从而导致了信号本身变化的减小。

一种恒跨导满幅CMOS运算放大器设计赵素梅;刘诗赋;崔智军【摘要】针对满幅运算放大器输入级跨导不恒定和简单AB类输出级性能较差这两个问题,采用两路结构相同的最小电流选择电路来稳定输入级的总跨导;浮动电流源控制的无截止前馈AB类输出级减小了交越失真,实现了运放的满幅输出;该电路采用0.6μm的BiCMOS工艺设计;利用Hspice进行仿真验证,结果表明,在0~3V 输入共模范围内,输入级跨导的变化小于3.03%,开环增益94.7dB,单位增益带宽为7.2MHz,相位裕量为65°.【期刊名称】《计算机测量与控制》【年(卷),期】2010(018)005【总页数】4页(P1161-1163,1167)【关键词】恒跨导;满幅;AB类输出;运算放大器【作者】赵素梅;刘诗赋;崔智军【作者单位】西北工业大学,电子信息学院,陕西,西安,710129;西北工业大学,电子信息学院,陕西,西安,710129;西北工业大学,电子信息学院,陕西,西安,710129【正文语种】中文【中图分类】TN4320 引言随着集成电路的发展,CMOS工艺的低功耗模拟电路越来越受到重视,这对模拟集成电路的基本单元——运算放大器提出了更高的要求。

在低电压下,CMOS运算放大器的输入输出信号的动态范围将大大减小[1],传统的PMOS或NMOS差分对输入已不能满足大的输入共模范围的要求,这样共模输入范围和输出摆幅从电源电压的一端变化到另一端的满幅(rail-to-rail,轨对轨)运放应运而生。

轨对轨运放的输入级通常采用PMOS和NMOS并联的互补差分结构[2],但由此引发的问题是输入级跨导在整个共模输入范围内是不恒定的,这不仅会影响环路的增益,引入额外的谐波失真,同时使频率补偿变得十分困难,严重时可能会导致系统不稳定。

传统的AB类输出级频率特性和动态特性较差,增益带宽积无法做得很高[3],因此稳定跨导在输入共模范围内恒定、提高输出级电路的增益带宽积和动态特性是轨对轨满幅运放设计的重点。